一种电源输出电路的制作方法

1.本技术涉及电源管理技术领域,尤其是一种电源输出电路。

背景技术:

2.在设计选型系统电源时,因系统供电的特殊性,现有的应用于dlp产品机芯系统的电源一般不具备冗余功能,当dlp系统的供电电源出现故障时,dlp系统需要在更换供电电源后才能正常工作,容灾能力较差。此外,dlp系统的供电电源不具备待机电压,无法在低功耗下维持系统的基本工作,导致系统可用性较低。

技术实现要素:

3.为解决上述技术问题,本发明实施例提供了一种电源输出电路。

4.本发明实施例所采取的技术方案是:

5.一种电源输出电路,包括:

6.第一并联输出模块,用于根据第一输出电源信号生成第三输出电源信号,所述第一输出电源信号包括第一电压和第一电流,所述第三输出电源信号包括第三电压和第三电流,所述第三电压等于所述第一电压,所述第三电流等于所述第一电流;

7.第二并联输出模块,用于根据第二输出电源信号生成第四输出电源信号,所述第二输出电源信号包括第二电压和第二电流,所述第四输出电源信号包括第四电压和第四电流,所述第四电压等于所述第二电压,所述第四电流等于所述第二电流;

8.待机电源输出模块,用于根据所述第二输出电源信号生成待机电源信号,所述待机电源输出模块包括降压模块和隔离模块,所述降压模块用于对所述第二输出电源信号进行降压,生成第五输出电源信号,所述隔离模块用于根据所述第五输出电源信号隔离输出所述待机电源信号。

9.作为一种可选的实施方式,所述降压模块包括降压芯片及对应的降压电路,所述隔离模块采用第一二极管;

10.所述降压模块的输入端口连接所述第二输出电源信号,所述降压模块的输出端口输出所述第五输出电源信号,所述降压模块的输出端口与所述第一二极管的正极连接,所述第一二极管的负极输出所述待机电源信号。

11.作为一种可选的实施方式,所述待机电源输出模块还包括供电模块,所述供电模块用于给所述降压芯片供电,所述供电模块包括低压差线性稳压器;

12.所述供电模块的输入端口连接所述第二输出电源信号,所述供电模块的输出端口与所述降压芯片的电源端口连接。

13.作为一种可选的实施方式,所述待机电源输出模块还包括金手指输出模块,所述金手指输出模块包括金手指、第一电阻、第二电阻、第三电阻、第一电容和第一nmos管;

14.所述第一电阻的第一端与所述供电模块的输出端口连接,所述第一电阻的第二端与所述第一nmos管的栅极连接,所述第一nmos管的栅极与所述第二电阻的第一端连接,所

述第二电阻的第二端与所述金手指的第一管脚连接,所述第一管脚没有被按压时为悬空状态,所述第一管脚被按压时接地,所述第二电阻的第一端与第一电容的第一端连接,所述第一电容的第二端与第三电阻的第一端连接,所述第三电阻的第一端与所述第一nmos管的源极连接,所述第一nmos管的源极接地,所述第一nmos管的栅极与所述第三电阻的第二端连接,所述第一nmos管的漏极与所述降压芯片的使能引脚连接,所述使能引脚接收到高电平时启用所述降压芯片。

15.作为一种可选的实施方式,所述第一并联输出模块包括第一冗余控制芯片和第二nmos管,所述第二nmos管的源极连接所述第一输出电源信号,所述第二nmos管的源极还与所述第一冗余控制芯片的输入引脚连接,所述第一冗余控制芯片的栅极驱动引脚与所述第二nmos管的栅极连接,所述第一冗余控制芯片的输出引脚与所述第二nmos管的漏极连接,所述第二nmos管的漏极连接所述第一并联输出模块的输出端口,所述第一并联输出模块的输出端口用于输出所述第三输出电源信号。

16.作为一种可选的实施方式,所述电源输出电路还包括第一开启缓冲模块,所述第一开启缓冲模块根据预设的第一控制信号控制所述第一冗余控制芯片缓慢开启或关闭,其中,当所述第一控制信号为高电平时,所述第一开启缓冲模块控制所述第一冗余控制芯片缓慢开启;当所述第一控制信号为低电平时,所述第一开启缓冲模块控制所述第一冗余控制芯片关闭。

17.作为一种可选的实施方式,所述第一开启缓冲模块包括第四电阻、第五电阻、第六电阻、第七电阻、第二电容、瞬态二极管、第三nmos管、第四nmos管、第五nmos管、第六nmos管和光耦,所述光耦包括输入端二极管和输出端三极管;

18.所述第三nmos管的栅极连接所述第一控制信号,所述第三nmos管的栅极与所述第四电阻的第一端连接,所述第四电阻的第二端与所述第三nmos管的源极连接,所述第三nmos管的源极与所述第五电阻的第一端连接,所述第五电阻的第一端与所述第四nmos管的源极连接,所述第四nmos管的源极连接预设的第一参考地,所述第四nmos管的栅极与所述第五电阻的第二端连接,所述第五电阻的第二端与所述第三nmos管的漏极连接,所述第三nmos管的漏极与所述输入端二极管的正极连接,所述输入端二极管的正极连接第五输出电源信号,所述输入端二极管的负极与所述第四nmos管的漏极连接,所述输出端三极管的集电极连接预设电源信号,所述输出端三极管的发射极与所述第五nmos管的栅极连接,所述第五nmos管的栅极与所述第六电阻的第一端连接,所述第六电阻的第一端与所述瞬态二极管的负极连接,所述瞬态二极管的负极与所述第二电容的第一端连接,所述第二电容的第一端与所述第七电阻的第一端连接,所述第七电阻的第二端与所述第六电阻的第二端连接,所述第六电阻的第二端与所述瞬态二极管的正极连接,所述瞬态二极管的正极与所述第二电容的第二端连接,所述第二电容的第二端与所述第五nnos管的源极连接,所述第五nmos管的源极连接预设的第二参考地,所述第五nmos管的漏极连接所述预设电源信号,所述第五nmos管的漏极与所述第六nmos管的栅极连接,所述第六nmos管的源极与所述第一冗余控制芯片的接地引脚连接,所述第六nmos管的漏极连接所述第一参考地。

19.作为一种可选的实施方式,所述第二并联输出模块包括第二冗余控制芯片和第七nmos管;

20.所述第七nmos管的源极连接所述第二并联输出模块的输入端口,所述第二并联输

出模块的输入端口用于连接所述第二输出电源信号,所述第七nmos管的漏极连接所述第二并联输出模块的输出端口,所述第二并联输出模块的输出端口用于输出所述第四输出电源信号,所述第二冗余控制芯片的栅极驱动引脚与所述第七nmos管的栅极连接。

21.作为一种可选的实施方式,所述电源输出电路在所述第二输出电源信号和所述第二并联输出模块的输入端口之间还设置有第二开启缓冲模块,所述第二开启缓冲模块根据预设的第二控制信号控制所述第二输出电源信号与所述第二并联输出模块的输入端口之间的通路的连通或断开,其中,当所述第二控制信号为高电平时,所述第二开启缓冲模块连通所述第二输出电源信号与所述第二并联输出模块的输入端口之间的通路;当所述第二控制信号为低电平时,所述第二开启缓冲模块断开所述第二输出电源信号与所述第二并联输出模块的输入端口之间的通路。

22.作为一种可选的实施方式,所述电源输出电路还包括第三并联输出模块,所述第三并联输出模块用于根据第五输出电源信号生成第六输出电源信号,所述第五输出电源信号包括第五电压和第五电流,所述第六输出电源信号包括第六电压和第六电流,所述第六电压等于所述第五电压,所述第六电流等于所述第五电流。

23.本发明实施例的电源输出电路,通过设置第一并联输出模块,基于原有的电源的第一输出电源信号生成第三输出电源信号,其中第三电压等于第一电压,第三电流等于第一电流;通过设置第二并联输出模块,基于电源原有的第二输出电源信号生成第四输出电源信号,其中第四电压等于第二电压,第四电流等于第二电流,将第一输出电源信号和第三输出电源信号给同一个负载供电,将第二输出电源信号和第四输出电源信号给同一个负载供电即可实现电源的并联冗余,当其中一个电源出现故障时其他电源不受影响,提升了电源的容灾能力;通过设置待机电源输出模块,根据第二输出电源信号生成待机电源信号,使得原有的电源具备待机电压,提升了可用性。

附图说明

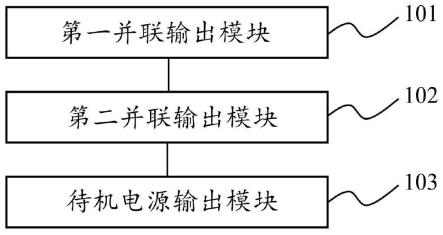

24.图1为本发明实施例电源输出电路的结构示意图;

25.图2为本发明实施例电源输出电路的待机电源输出模块的电路连接示意图;

26.图3为本发明实施例电源输出电路与供电模块的电路连接示意图;

27.图4为本发明实施例电源输出电路的金手指输出模块的电路连接示意图;

28.图5为本发明实施例电源输出电路的第一并联输出模块和第一开启缓冲模块的电路连接示意图;

29.图6为本发明实施例电源输出电路的第二并联输出模块和第二开启缓冲模块的电路连接示意图。

30.附图标记:101、第一并联输出模块;102、第二并联输出模块;103、待机电源输出模块;u1、降压芯片;vd48_0a、第一输出电源信号;vd12_0、第二输出电源信号;vd48_1、第三输出电源信号;vd12_1、第四输出电源信号;vd5.0_1、第五输出电源信号;5vsb、待机电源信号;u2、低压差线性稳压器;dgnd、第一参考地;u3、第一冗余控制芯片;u4、光耦;u5、第二冗余控制芯片;vd10.0_a、预设电源信号;d1、第一二极管;d2、瞬态二极管;m1第一nmos管;m2、第二nmos管;m3、第三nmos管;m4、第四nmos管;m5、第五nmos管;m6、第六nmos管;m7、第七nmos管;m8、第八nmos管;r1、第一电阻;r2、第二电阻;r3、第三电阻;r4、第四电阻;r5、第五

电阻;r6、第六电阻;r7、第七电阻;c1、第一电容;c2、第二电容;c3、充放电电容;q1、三极管。

具体实施方式

31.为了使本技术领域的人员更好地理解本技术方案,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分的实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本技术保护的范围。

32.本技术的说明书和权利要求书及所述附图中的术语“第一”、“第二”、“第三”和“第四”等是用于区别不同对象,而不是用于描述特定顺序。此外,术语“包括”和“具有”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。

33.在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本技术的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

34.在设计选型系统电源时,因系统供电的特殊性,现有的应用于dlp产品机芯系统的电源一般不具备冗余功能,当dlp系统的供电电源出现故障时,dlp系统需要在更换供电电源后才能正常工作,容灾能力较差。此外,dlp系统的供电电源不具备待机电压,无法在低功耗下维持系统的基本工作,导致系统可用性较低。为此,本发明实施例提出了一种电源输出电路,通过设置第一并联输出模块,基于原有的电源的第一输出电源信号生成第三输出电源信号,其中第三电压等于第一电压,第三电流等于第一电流;通过设置第二并联输出模块,基于电源原有的第二输出电源信号生成第四输出电源信号,其中第四电压等于第二电压,第四电流等于第二电流,将第一输出电源信号和第三输出电源信号给同一个负载供电,将第二输出电源信号和第四输出电源信号给同一个负载供电即可实现电源的并联冗余,当其中一个电源出现故障时其他电源不受影响,提升了电源的容灾能力;通过设置待机电源输出模块,根据第二输出电源信号生成待机电源信号,使得原有的电源具备待机电压,提升了可用性。

35.如图1所示,本发明实施例提出了一种电源输出电路,包括:

36.第一并联输出模块101,用于根据第一输出电源信号vd48_0a生成第二输出电源信号vd48_1,第一输出电源信号vd48_0a包括第一电压和第一电流,第二输出电源信号vd48_1包括第三电压和第三电流,第三电压等于第一电压,第三电流等于第一电流;

37.第二并联输出模块102,用于根据第二输出电源信号vd12_0生成第四输出电源信号vd12_1,第二输出电源信号vd12_0包括第二电压和第二电流,第四输出电源信号vd12_1包括第四电压和第四电流,第四电压等于第二电压,第四电流等于第二电流;

38.待机电源输出模块103,用于根据第二输出电源信号vd12_0生成待机电源信号5vsb,待机电源输出模块103包括降压模块和隔离模块,降压模块用于对第二输出电源信号vd12_0进行降压,生成第五输出电源信号vd5.0_1,隔离模块用于根据第五输出电源信号

vd5.0_1隔离输出待机电源信号5vsb。

39.可选地,在一些实施例中,基于dlp系统的供电电源进行电源输出控制,实现电源信号的并联均流和待机电源信号5vsb的生成。dlp系统的供电电源为48v/12v电源,其中第一输出电源信号vd48_0a为48v/10a,第二输出电源信号vd12_0为12v/10a。本发明的一些实施例根据第一输出电源信号vd48_0a,通过第一并联输出模块101生成第二输出电源信号vd48_1,根据第二输出电源信号vd12_0,通过第二并联输出模块102生成第四输出电源信号vd12_1,其中第二输出电源信号vd48_1为48v/10a,与第一输出电源信号vd48_0a相同,第四输出电源信号vd12_1为12v/10a,与第二输出电源信号vd12_0相同。可以理解的是,将第一输出电源信号vd48_0a和第二输出电源信号vd48_1给同一个负载供电可实现第一输出电源信号vd48_0a和第二输出电源信号vd48_1的并联冗余,当第一输出电源信号vd48_0a和第二输出电源信号vd48_1均正常输出至该负载时,第一输出电源信号vd48_0a和第二输出电源信号vd48_1中的任意一个给该负载供电,或者第一输出电源信号vd48_0a和第二输出电源信号vd48_1协同工作,共同给该负载供电;当第一输出电源信号vd48_0a和第二输出电源信号vd48_1其中一个电源信号无法给该负载供电时,由另一个电源信号给该负载供电,提升了电源和系统(dlp系统)的可用性和容灾能力。同样地,将第二输出电源信号vd12_0和第四输出电源信号vd12_1给同一个负载供电,即可实现第二输出电源信号vd12_0和第四输出电源信号vd12_1的并联冗余,当第二输出电源信号vd12_0和第四输出电源信号vd12_1均正常输出至该负载时,第二输出电源信号vd12_0和第四输出电源信号vd12_1中的任意一个给该负载供电,或者第二输出电源信号vd12_0和第四输出电源信号vd12_1协同工作,共同给该负载供电;当第二输出电源信号vd12_0和第四输出电源信号vd12_1其中一个电源信号无法给该负载供电时,由另一个电源信号给该负载供电,提升了电源和系统(dlp系统)的可用性和容灾能力。

40.作为一种可选的实施方式,降压模块包括降压芯片u1及对应的降压电路,隔离模块采用第一二极管d1;

41.降压模块的输入端口连接第二输出电源信号vd12_0,降压模块的输出端口输出第五输出电源信号vd5.0_1,降压模块的输出端口与第一二极管d1的正极连接,第一二极管d1的负极输出待机电源信号5vsb。

42.可选地,参照图2,在一些实施例中,降压芯片u1采用lm2743,降压模块包括型号为lm2743的降压芯片u1及lm2743的降压电路,其中,lm2743的hg引脚驱动上管nmos,lg引脚驱动下管nmos。根据先验知识可知,lm2743的hg引脚与lg引脚联锁,即上管nmos和下管nmos无法同时导通,避免第二输出电源信号vd12_0直接接地,造成短路。此外,lm2743的isen引脚为电流限制阈值设置引脚,输出的电流值为40μa,需要连接电阻进行电流限制设置。根据先验知识可知,lm2743的isen引脚的电流限制是通过检测下管nmos导通时r

ds

(源漏电阻)的压降来实现的,即压降v

ds

=i

out

*r

ds

。根据图2可知,lm2743的isen引脚在进行电流限制阈值设置后,经lc整流滤波电路过滤交流信号,生成第五输出电源信号vd5.0_1。

43.根据先验知识可知,二极管具有单向导通性(正向导通,反向截止),本发明的一些实施例根据降压模块输出的第五输出电源信号vd5.0_1,采用第一二极管d1隔离输出待机电源信号5vsb,避免了待机电源信号5vsb对第五输出电源信号vd5.0_1的影响。

44.作为一种可选的实施方式,待机电源输出模块103还包括供电模块,供电模块用于

给降压芯片u1供电,供电模块包括低压差线性稳压器u2;

45.供电模块的输入端口连接第二输出电源信号vd12_0,供电模块的输出端口与降压芯片u1的电源端口连接。

46.可选地,在一些实施例中,供电模块采用如图3所示的低压差线性稳压器u2(ldo)的降压电路,通过对第二输出电源信号vd12_0进行降压,并将降压后的电源信号输出至降压芯片u1的电源端口,以实现对降压芯片u1的供电。

47.可选地,在一些实施例中,当应用于dlp系统的供电电源的电源输出控制时,第二输出电源信号vd12_0为12v/10a,通过供电模块对第二输出电源信号vd12_0进行降压,生成降压后的电源信号(图3中的5vs),用于给降压芯片u1供电。可以理解的是,降压后的电源信号的电压值需要根据降压芯片u1的型号进行调整,在一些实施例中,降压芯片u1的型号为lm2743,则供电模块对第二输出电源信号vd12_0降压后输出的电源信号的电压值可为5v。

48.参照图4,作为一种可选的实施方式,待机电源输出模块103还包括金手指输出模块,金手指输出模块包括金手指、第一电阻r1、第二电阻r2、第三电阻r3、第一电容c1和第一nmos管m1;

49.第一电阻r1的第一端与供电模块的输出端口连接,第一电阻r1的第二端与第一nmos管m1的栅极连接,第一nmos管m1的栅极与第二电阻r2的第一端连接,第二电阻r2的第二端与金手指的第一管脚连接,第一管脚没有被按压时为悬空状态,第一管脚被按压时接地,第二电阻r2的第一端与第一电容c1的第一端连接,第一电容c1的第二端与第三电阻r3的第一端连接,第三电阻r3的第一端与第一nmos管m1的源极连接,第一nmos管m1的源极接地,第一nmos管m1的栅极与第三电阻r3的第二端连接,第一nmos管m1的漏极与降压芯片u1的使能引脚连接,使能引脚接收到高电平时启用降压芯片u1。

50.根据图4,可以理解的是,当金手指的第一管脚没有被按压时为悬空状态,即金手指的第一管脚输出高电平(图4中的5vsvon),此时第一nmos管m1导通,第一nmos管m1的漏极为低电平,即降压芯片u1的使能引脚接收到低电平,降压芯片u1停止工作;当金手指的第一管脚被按压时接地,即金手指的第一管脚输出低电平(图4中的5vsvon),此时第一nmos管m1截止,第一nmos管m1的漏极为高电位,即降压芯片u1的使能引脚接收到高电平,降压芯片u1启动,开始工作。由此可知,本发明的实施例通过设置金手指输出模块,在按压金手指(第一管脚)时启用降压芯片u1,实现了金手指控制待机电源信号5vsb输出功能。

51.参照图5,作为一种可选的实施方式,第一并联输出模块101包括第一冗余控制芯片u3和第二nmos管m2,第二nmos管m2的源极连接第一输出电源信号vd48_0a,第二nmos管m2的源极还与第一冗余控制芯片u3的输入引脚连接,第一冗余控制芯片u3的栅极驱动引脚与第二nmos管m2的栅极连接,第一冗余控制芯片u3的输出引脚与第二nmos管m2的漏极连接,第二nmos管m2的漏极连接第一并联输出模块101的输出端口,第一并联输出模块101的输出端口用于输出第二输出电源信号vd48_1。

52.其中,第一冗余控制芯片u3通过栅极驱动引脚驱动第二nmos管m2的导通和截止。可选地,在一些实施例中,第一冗余控制芯片u3为n+1冗余控制芯片,能够均流两路并联电源的电流。当第二nmos管m2导通时,第一并联输出模块101的输出端口输出第二输出电源信号vd48_1。

53.作为一种可选的实施方式,电源输出电路还包括第一开启缓冲模块,第一开启缓

冲模块根据预设的第一控制信号(图5中的onoff)控制第一冗余控制芯片u3缓慢开启或关闭,其中,当第一控制信号为高电平时,第一开启缓冲模块控制第一冗余控制芯片u3缓慢开启;当第一控制信号为低电平时,第一开启缓冲模块控制第一冗余控制芯片u3关闭。

54.可以理解的是,本发明实施例通过第一开启缓冲模块控制第一冗余控制芯片u3缓慢开启,起到了防浪涌的效果。

55.可以理解的是,第一控制信号相当于第一并联输出模块101的开关信号,本发明实施例通过在第一控制信号为高电平时通过第一开启缓冲模块控制第一冗余控制芯片u3缓慢开启,在第一控制信号为低电平时通过第一开启缓冲模块控制第一冗余控制芯片u3关闭,实现了基于第一控制信号的第一并联输出模块101的开关机功能。

56.参照图5,作为一种可选的实施方式,第一开启缓冲模块包括第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第二电容c2、瞬态二极管d2、第三nmos管m3、第四nmos管m4、第五nmos管m5、第六nmos管m6和光耦u4,所述光耦u4包括输入端二极管和输出端三极管;

57.第三nmos管m3的栅极连接第一控制信号,第三nmos管m3的栅极与第四电阻r4的第一端连接,第四电阻r4的第二端与第三nmos管m3的源极连接,第三nmos管m3的源极与第五电阻r5的第一端连接,第五电阻r5的第一端与第四nmos管m4的源极连接,第四nmos管m4的源极连接预设的第一参考地dgnd,第四nmos管m4的栅极与第五电阻r5的第二端连接,第五电阻r5的第二端与第三nmos管m3的漏极连接,第三nmos管m3的漏极与输入端二极管的正极连接,输入端二极管的正极连接第五输出电源信号vd5.0_1,输入端二极管的负极与第四nmos管m4的漏极连接,输出端三极管的集电极连接预设电源信号vd10.0_a,输出端三极管的发射极与第五nmos管m5的栅极连接,第五nmos管m5的栅极与第六电阻r6的第一端连接,第六电阻r6的第一端与瞬态二极管d2的负极连接,瞬态二极管d2的负极与第二电容c2的第一端连接,第二电容c2的第一端与第七电阻r7的第一端连接,第七电阻r7的第二端与第六电阻r6的第二端连接,第六电阻r6的第二端与瞬态二极管d2的正极连接,瞬态二极管d2的正极与第二电容c2的第二端连接,第二电容c2的第二端与第五nnos管的源极连接,第五nmos管m5的源极连接预设的第二参考地,第五nmos管m5的漏极连接预设电源信号vd10.0_a,第五nmos管m5的漏极与第六nmos管m6的栅极连接,第六nmos管m6的源极与第一冗余控制芯片u3的接地引脚连接,第六nmos管m6的漏极连接第一参考地dgnd。

58.其中,光耦u4用于隔离预设电源信号vd10.0_a和第五输出电源信号vd5.0_1,预设电源信号vd10.0_a为电源输出电路内部产生的电源信号。

59.根据图5可知,当第一控制信号为高电平时,第三nmos管m3导通,此时第三nmos管m3的漏极为低电位,第四nmos管m4不导通,因此光耦u4不工作,第五nmos管m5的栅极为低电位,第五nmos管m5不导通。此时,预设电源信号vd10.0_a给第六nmos管m6上电,第六nmos管m6导通,则第一冗余控制芯片u3的接地引脚连接至第一参考地dgnd,第一冗余控制芯片u3开始工作。可以理解的是,从第三nmos管m3的栅极接收到为高电平的第一控制信号到第一冗余控制芯片u3开始工作存在一段缓冲时间,实现了在第一控制信号为高电平时通过第一开启缓冲模块控制第一冗余控制芯片u3缓慢开启的功能,提升了第一并联输出模块101的防浪涌能力;当第一控制信号为低电平时,第三nmos管m3不导通,此时第三nmos管m3的漏极为高电位,第四nmos管m4导通,因此光耦u4工作,第五nmos管m5的栅极为高电位,第五nmos管m5导通。此时,预设电源信号vd10.0_a无法给第六nmos管m6上电,第六nmos管m6的栅极为

低电位,第六nmos管m6不导通,则第一冗余控制芯片u3的接地引脚无法连接至第一参考地dgnd,第一冗余控制芯片u3停止工作。

60.可选地,在一些实施例中,第一参考地dgnd为大地。

61.参照图6,作为一种可选的实施方式,第二并联输出模块102包括第二冗余控制芯片u5和第七nmos管m7;

62.第七nmos管m7的源极连接第二并联输出模块102的输入端口,第二并联输出模块102的输入端口用于连接第二输出电源信号vd12_0,第七nmos管m7的漏极连接第二并联输出模块102的输出端口,第二并联输出模块102的输出端口用于输出第四输出电源信号vd12_1,第二冗余控制芯片u5的栅极驱动引脚与第七nmos管m7的栅极连接。

63.其中,第二冗余控制芯片u5通过栅极驱动引脚驱动第七nmos管m7的导通和截止。可选地,在一些实施例中,第二冗余控制芯片u5为n+1冗余控制芯片,能够均流两路并联电源的电流。当第七nmos管m7导通时,第二并联输出模块102的输出端口输出第四输出电源信号vd12_1。

64.可选地,在一些实施例中,当应用于dlp系统的供电电源的电源输出控制时,第一输出电源信号vd48_0a为48v/10a,第二输出电源信号vd12_0为12v/10a,第二冗余控制芯片u5与第一冗余控制芯片u3的功能相同,均起到并联均流的作用,但相较于第一冗余控制芯片u3,第二冗余控制芯片u5控制的并联电压较低。

65.作为一种可选的实施方式,电源输出电路在第二输出电源信号vd12_0和第二并联输出模块102的输入端口之间还设置有第二开启缓冲模块,第二开启缓冲模块根据预设的第二控制信号(图6中的onoff)控制第二输出电源信号vd12_0与第二并联输出模块102的输入端口之间的通路的连通或断开,其中,当第二控制信号为高电平时,第二开启缓冲模块连通第二输出电源信号vd12_0与第二并联输出模块102的输入端口之间的通路;当第二控制信号为低电平时,第二开启缓冲模块断开第二输出电源信号vd12_0与第二并联输出模块102的输入端口之间的通路。

66.可以理解的是,第二控制信号相当于第二并联输出模块102的开关信号,本发明实施例通过在第二控制信号为高电平时通过第二开启缓冲模块控制第二并联输出模块102输出第四输出电源信号vd12_1,在第二控制信号为低电平时通过第二开启缓冲模块控制第二并联输出模块102无信号输出,实现了基于第二控制信号的第二并联输出模块102的开关机功能。

67.可选地,参照图6,在一些实施例中,第二开启缓冲模块可包括充放电电容c3、三极管q1和第八nmos管m8,其中,第八nmos管m8导通时第二输出电源信号vd12_0与第二并联输出模块102的输入端口之间的通路的连通,第八nmos管m8不导通时第二输出电源信号vd12_0与第二并联输出模块102的输入端口之间的通路的断开。当第二控制信号为高电平时,充放电电容c3控制三极管q1缓慢导通,从而控制第八nmos管m8缓慢导通,使得第二输出电源信号vd12_0与第二并联输出模块102的输入端口之间的通路的缓慢连通,即从接收到为高电平的第二控制信号到第二并联输出模块102输出第四输出电源信号vd12_1存在一段缓冲时间,实现了在第二控制信号为高电平时通过第二开启缓冲模块控制第二并联输出模块102缓慢开启的功能,提升了第二并联输出模块102的防浪涌能力;当第二控制信号为低电平时,充放电电容c3控制三极管q1截止,从而控制第八nmos管m8截止,使得第二输出电源信

号vd12_0与第二并联输出模块102的输入端口之间的通路的断开,第二并联输出模块102无信号输出。

68.作为一种可选的实施方式,电源输出电路还包括第三并联输出模块,第三并联输出模块用于根据第五输出电源信号vd5.0_1生成第六输出电源信号,第五输出电源信号vd5.0_1包括第五电压和第五电流,第六输出电源信号包括第六电压和第六电流,第六电压等于第五电压,第六电流等于第五电流。

69.综上所述,本发明实施例的电源输出电路,通过设置第一并联输出模块101,基于原有的电源的第一输出电源信号vd48_0a生成第二输出电源信号vd48_1,其中第三电压等于第一电压,第三电流等于第一电流;通过设置第二并联输出模块102,基于电源原有的第二输出电源信号vd12_0生成第四输出电源信号vd12_1,其中第四电压等于第二电压,第四电流等于第二电流,将第一输出电源信号vd48_0a和第二输出电源信号vd48_1给同一个负载供电,将第二输出电源信号vd12_0和第四输出电源信号vd12_1给同一个负载供电即可实现电源的并联冗余,当其中一个电源出现故障时其他电源不受影响,提升了电源的容灾能力;通过设置待机电源输出模块103,根据第二输出电源信号vd12_0生成待机电源信号5vsb,使得原有的电源具备待机电压,提升了可用性。

70.以上是对本发明的较佳实施进行了具体说明,但本发明并不限于所述实施例,熟悉本领域的技术人员在不违背本发明精神的前提下还可做作出种种的等同变形或替换,这些等同的变形或替换均包含在本技术权利要求所限定的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1