静电放电电流的抑制电路、显示器和设备终端的制作方法

本申请涉及显示领域,具体涉及一种静电放电电流的抑制电路、显示器和设备终端。

背景技术:

1、目前,随着对于移动设备电池的续航能力要求逐渐提高,移动设备驱动芯片对应的驱动电压逐渐降低,从而确保电池能够续航更长的时间。

2、然而,随着驱动电压的降低,移动设备驱动芯片的esd(electro-staticdischarge,静电放电电流)抑制特性逐渐减弱,即esd噪声增加,进而导致对应的输入信号相位延迟。

技术实现思路

1、鉴于此,本申请提供一种静电放电电流的抑制电路,能够抑制上述esd噪声的能力,进而使得对应的信号相位延迟大大降低。

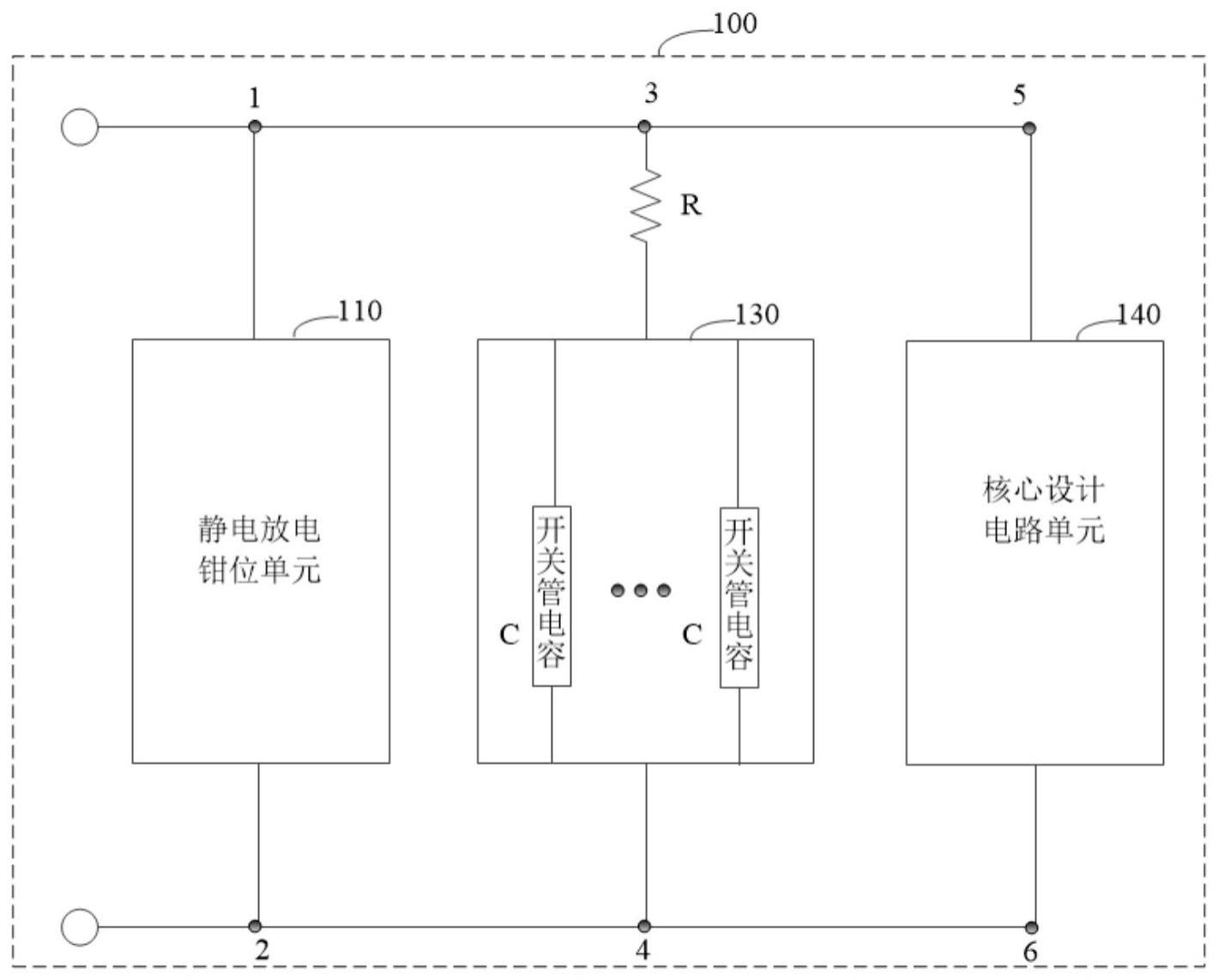

2、一种静电放电电流的抑制电路,包括:

3、静电放电钳位单元,用于对输入电源的静电放电电流进行第一级衰减;

4、去耦单元,用于对静电放电钳位单元的输出电流进行第二级衰减;

5、去耦单元包括多个并联连接的去耦子单元,每个去耦子单元均包括串联连接的开关管电容和保护电阻,保护电阻的一端与静电放电钳位单元的输出端相连接,保护电阻的另一端与开关管电容的栅极控制端相连接。

6、在一个实施例中,抑制电路还包括核心设计电路单元,核心设计电路单元的输入端与去耦单元的输出端电性连接。

7、在一个实施例中,开关管电容为pmos开关管。

8、在一个实施例中,开关管电容为nmos开关管。

9、在一个实施例中,保护电阻为0.5kω~1kω。

10、在一个实施例中,开关管电容为0.8pf~1.2pf。

11、在一个实施例中,核心设计电路单元包括锁存电路单元、反相器电路单元、存储电路单元以及数据选择器电路单元中的任意一种。

12、在一个实施例中,存储电路单元为非易失性存储单元。

13、此外还提供一种oled显示器,包括上述抑制电路。

14、此外还提供一种设备终端,包括上述oled显示器。

15、上述静电放电电流的抑制电路,包括静电放电钳位单元,用于对输入电源的静电放电电流进行第一级衰减;去耦单元,用于对静电放电钳位单元的输出电流进行第二级衰减,去耦单元包括多个并联连接的去耦子单元,每个去耦子单元均包括串联连接的开关管电容和保护电阻,保护电阻的一端与静电放电钳位单元的输出端相连接,保护电阻的另一端与开关管电容的栅极控制端相连接,该抑制电路通过在每个开关管电容的栅极控制端单独连接设置一个保护电阻,从而使得静电放电电流分别通过每个保护电阻和开关管电容进行衰减,进而能够提高抑制上述esd噪声的能力,最终使得对应的输入信号相位延迟大大降低。

技术特征:

1.一种静电放电电流的抑制电路,其特征在于,包括:

2.根据权利要求1所述的抑制电路,其特征在于,所述抑制电路还包括核心设计电路单元,所述核心设计电路单元的输入端与所述去耦单元的输出端电性连接。

3.根据权利要求1所述的抑制电路,其特征在于,所述开关管电容为pmos开关管电容。

4.根据权利要求1所述的抑制电路,其特征在于,所述开关管电容为nmos开关管电容。

5.根据权利要求1所述的抑制电路,其特征在于,所述保护电阻为0.5kω~1kω。

6.根据权利要求1所述的抑制电路,其特征在于,所述开关管电容为0.8pf~1.2pf。

7.根据权利要求2所述的抑制电路,其特征在于,所述核心设计电路单元包括锁存电路单元、反相器电路单元、存储电路单元以及数据选择器电路单元中的任意一种。

8.根据权利要求7所述的抑制电路,其特征在于,所述存储电路单元为非易失性存储单元。

9.一种oled显示器,其特征在于,包括权利要求1至7中任一项所述的抑制电路。

10.一种设备终端,其特征在于,包括权利要求9所述的oled显示器。

技术总结

本申请涉及静电放电电流的抑制电路、OLED显示器和设备终端,该抑制电路包括静电放电钳位单元,用于对输入电源的静电放电电流进行第一级衰减;去耦单元,用于对静电放电钳位单元的输出电流进行第二级衰减,去耦单元包括多个并联连接的去耦子单元,每个去耦子单元均包括串联连接的开关管电容和保护电阻,保护电阻的一端与静电放电钳位单元的输出端相连接,保护电阻的另一端与开关管电容的栅极控制端相连接,该抑制电路通过在每个开关管电容的栅极控制端单独连接设置一个保护电阻,从而使得静电放电电流分别通过每个保护电阻和开关管电容进行衰减,提高抑制上述ESD噪声的能力,最终使得输入信号相位延迟大大降低。

技术研发人员:谭力,施伟,宋羲燮

受保护的技术使用者:晟合微电子(肇庆)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!