一种谐振回路结构的制作方法

1.本实用新型涉及电路结构领域,特别涉及一种谐振回路结构。

背景技术:

2.lcc谐振电路,主要是指电感、电容并联谐振组成的lc振荡器。因为lc回路有选频特性。理由:回路的等效阻抗z=(-j/ωc)/(r+jωl),可知,阻抗z与信号频率有关。不同频率的信号电流(同等大小的电流)在通过回路时,产生的电压是不同的。只有一个频率的信号电流产生的电压最大,就是当信号角频率ω=ω0=1/√lc时。此时回路阻抗最大,叫做并联谐振。

3.但是,现有的电路结构一般采用电感以及电容的配合组成,且电压输出不稳定,对于适配器来说,电压的不稳定容易造成相应电子设备(如手机)的负荷,造成电子设备的损坏。同时采用多个电感以及电容配合,在相同的降压谐振时,其体积较大,因此适配器的厚度也相应增加,影响了适配器的美观。

技术实现要素:

4.本实用新型的主要目的是提出一种谐振回路结构,旨在通过并联设置的coolmos,组成lcc谐振回路,起到降压(21v)谐振,且减压较为稳定,避免了电子设备的损坏。

5.为实现上述目的,本实用新型提出一种谐振回路结构,包括:

6.主控制芯片,所述主控制芯片包括:

7.gateh脚,llc高端mosfet的栅极驱动器输出,

8.suphs脚,高端驱动器电源输入,

9.hb脚,用于高端驱动器的低电平基准电压源和用于半桥斜坡的输入检测;

10.第一coolmos,所述第一coolmos与gateh脚相连接;

11.第二coolmos,所述第二coolmos与suphs脚相连接;

12.所述第一coolmos、第二coolmos相互并联并与hb脚半桥节点。

13.优选地,所述第一coolmos和第二coolmos包括并联设置的第一二极管和第一电阻。

14.优选地,所述第一coolmos和hb脚之间并联有第二电阻。

15.优选地,所述第二coolmos和hb脚之间并联有固定电容。

16.优选地,所述第一coolmos与gateh脚之间还串联有第三电阻。

17.优选地,所述第二coolmos与suphs脚之间还串联有单向二极管和第四电阻。

18.本实用新型技术方案当电压输入,通过第一coolmos和第二coolmos的可以将gateh脚和suphs脚压降降至最低,特别是使用大型mosfet和高开关频率时,二极管两端的巨大压降降低了高端mosfet的栅极驱动,通过hb脚的半桥节点检测可以将电压降压(21v)谐振。

附图说明

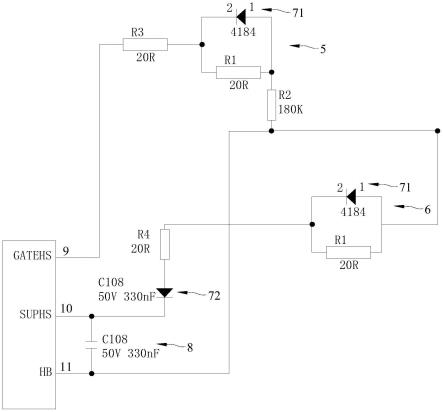

19.图1为本实用新型结构原理图。

20.图中,9为gateh脚,10为suphs脚,11为hb脚,r1为第一电阻,r2为第二电阻,r3为第三电阻,r4为第四电阻,5为第一coolmos,6为第二coolmos,71为第一二极管,72为单向二极管,8为固定电容。

具体实施方式

21.下面将结合附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型的一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

22.需要说明,若本实用新型实施例中有涉及方向性指示(诸如上、下、左、右、前、后、顶、底、内、外、垂向、横向、纵向,逆时针、顺时针、周向、径向、轴向

……

),则该方向性指示仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

23.另外,若本实用新型实施例中有涉及“第一”或者“第二”等的描述,则该“第一”或者“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本实用新型要求的保护范围之内。

24.如图1所示,一种谐振回路结构,包括:

25.主控制芯片(所述主控制芯片为tea2016aat,其为高效谐振电源的数字可配置llc和pfc组合控制器。同时集成了llc控制器功能以及dcm和qr模式下工作的pfc控制器。借助tea2016aat可以构建出完整的谐振电源,不仅设计简单,所需组件数也很少),所述主控制芯片包括:

26.gateh脚9,llc高端mosfet的栅极驱动器输出,

27.suphs脚10,高端驱动器电源输入,

28.hb脚11,用于高端驱动器的低电平基准电压源和用于半桥斜坡的输入检测;

29.第一coolmos5,所述第一coolmos5与gateh脚9相连接;

30.第二coolmos6,所述第二coolmos6与suphs脚10相连接;

31.所述第一coolmos5、第二coolmos6相互并联并与hb脚11半桥节点。

32.当电压输入,通过第一coolmos5和第二coolmos6的可以将gateh脚9和suphs脚10压降降至最低,特别是使用大型mosfet和高开关频率时,二极管两端的巨大压降降低了高端mosfet的栅极驱动,通过hb脚11的半桥节点检测可以将电压降压(21v)谐振。

33.在本实用新型实施例中,所述第一coolmos5和第二coolmos6包括并联设置的第一二极管71和第一电阻r1。coolmos在同等功率下封装较小,有利于电源小型化;同时栅极开启电压限高,搞干扰能力强;且栅极电荷小,驱动功率小;还具有节电容小,开关损耗小。

34.在本实用新型实施例中,所述第一coolmos5和hb脚11之间并联有第二电阻r2,通

过第二电阻r2限制第一coolmos5和第二coolmos6之间的并联电流。

35.在本实用新型实施例中,所述第二coolmos6和hb脚11之间并联有固定电容8,使第二coolmos6和hb脚11进行阻挡。

36.在本实用新型实施例中,所述第一coolmos5与gateh脚9之间还串联有第三电阻r3。

37.在本实用新型实施例中,所述第二coolmos6与suphs脚10之间还串联有单向二极管72和第四电阻r4。

38.以上所述仅为本实用新型的优选实施例,并非因此限制本实用新型的专利范围,凡是在本实用新型的实用新型构思下,利用本实用新型说明书及附图内容所作的等效结构变换,或直接/间接运用在其他相关的技术领域均包括在本实用新型的专利保护范围内。

技术特征:

1.一种谐振回路结构,其特征在于,包括:主控制芯片,所述主控制芯片包括:gateh脚,llc高端mosfet的栅极驱动器输出,suphs脚,高端驱动器电源输入,hb脚,用于高端驱动器的低电平基准电压源和用于半桥斜坡的输入检测;第一coolmos,所述第一coolmos与gateh脚相连接;第二coolmos,所述第二coolmos与suphs脚相连接;所述第一coolmos、第二coolmos相互并联并与hb脚半桥节点。2.如权利要求1所述的谐振回路结构,其特征在于:所述第一coolmos和第二coolmos包括并联设置的第一二极管和第一电阻。3.如权利要求1所述的谐振回路结构,其特征在于:所述第一coolmos和hb脚之间并联有第二电阻。4.如权利要求1所述的谐振回路结构,其特征在于:所述第二coolmos和hb脚之间并联有固定电容。5.如权利要求1所述的谐振回路结构,其特征在于:所述第一coolmos与gateh脚之间还串联有第三电阻。6.如权利要求1所述的谐振回路结构,其特征在于:所述第二coolmos与suphs脚之间还串联有单向二极管和第四电阻。7.如权利要求1所述的谐振回路结构,其特征在于:所述主控制芯片为tea2016aat。

技术总结

本实用新型公开了一种谐振回路结构,包括主控制芯片、第一COOLMOS和第二COOLMOS,所述主控制芯片包括GATEH脚LLC高端MOSFET的栅极驱动器输出、SUPHS脚高端驱动器电源输入和HB脚用于高端驱动器的低电平基准电压源和用于半桥斜坡的输入检测;所述第一COOLMOS与GATEH脚相连接,所述第二COOLMOS与SUPHS脚相连接;所述第一COOLMOS、第二COOLMOS相互并联并与HB脚半桥节点。当电压输入,通过第一COOLMOS和第二COOLMOS的可以将GATEH脚和SUPHS脚压降降至最低,特别是使用大型MOSFET和高开关频率时,二极管两端的巨大压降降低了高端MOSFET的栅极驱动,通过HB脚的半桥节点检测可以将电压降压(21V)谐振。压(21V)谐振。压(21V)谐振。

技术研发人员:王爱花

受保护的技术使用者:东莞市宝铼珀通讯科技有限公司

技术研发日:2022.03.01

技术公布日:2022/8/23

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1