一种三倍负压电荷泵及射频开关芯片的制作方法

1.本实用新型涉及射频开关技术领域,具体为一种用于射频开关的三倍负压电荷泵。

背景技术:

2.目前,用于通信设备的射频器件包括射频收发器、放大器、开关、电源及天线等,为减少器件整体面积,常在mipi接口(移动设备处理器接口)中使用1.8v或1.2v的单根电源线vio为射频开关供电,并采用负压电荷泵对vio 电压进行抬升及反向转换,以满足射频开关关闭时的电压需求。

3.常用负压电荷泵包括:两倍负压电荷泵、三倍负压电荷泵,其中,三倍负压电荷泵由两个两倍负压泵级联获得,但目前常用三倍负压电荷泵存在结构复杂,占用面积大的问题,原因在于,目前常用的级联的两倍负压电荷泵结构中,振荡器输出的反相时钟信号clk1、clk2需要至少四个电容实现信号反向,为确保电容性能,需使四个电容的面积保持一致,这不仅增加了工艺复杂度,并且在实际制造过程中四个电容的设置占用了较大的空间面积。另外,两级级联电路的驱动电压由额外的辅助电路提供,辅助电路的设置,也增加了整个集成电路系统的面积,无法满足集成电路的高度集成化、微型化要求。

技术实现要素:

4.针对现有技术中存在的上述问题,本实用新型提供了一种三倍负压电荷泵,其结构设计简单合理,可减少电容占用面积,且无需设置额外的辅助电路即可满足电压驱动需求。

5.为实现上述目的,本实用新型采用如下技术方案:

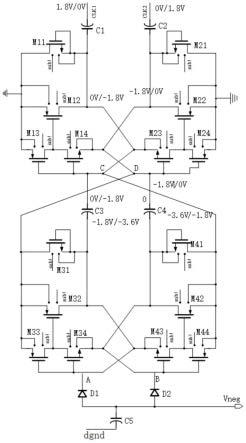

6.一种三倍负压电荷泵,其包括一级负压电荷泵、二级负压电荷泵,所述一级负压电荷泵与所述二级负压电荷泵级联,所述一级负压电荷泵包括第一电容 c1、第二电容c2、第一开关单元、第二开关单元,其特征在于,所述二级负压电荷泵包括第三电容c3、第四电容c4、第三开关单元、第四开关单元;所述第一开关单元包括mos管m11、m12、m13、m14,所述第二开关单元包括mos管m21、m22、m23、m24,所述第一电容c1的一端连接时钟信号clk1,另一端分别连接 mos管m11的发射极、mos管m12的集电极、mos管m23的发射极、mos管m13 与m14的基极、第三电容c3一端、mos管m41的集电极、mos管m42的发射极、 mos管m44的发射极;所述第二电容c2的一端连接时钟信号clk2,另一端分别连接mos管m21的发射极、mos管m22的集电极、mos管m14的发射极、mos管 m23与m24的基极、第四电容c4一端、mos管m31的集电极、mos管m32的发射极、mos管m33的发射极;

7.所述第三电容c3的另一端分别连接所述mos管m31的发射极、mos管m32 的集电极、mos管m43的发射极、mos管m34与m33的基极、二极管d1的阴极,所述第四电容c4的另一端分别连接所述mos管m41的发射极、mos管m42的集电极、mos管m34的发射极、mos管m43与m44的基极、二极管d2的阴极;所述二极管d1、d2的阳极连接后分别连接电容c5一端、输出端vneg,

所述电容 c5另一端接地。

8.其进一步特征在于,

9.所述mos管m11、m21、m14、m23、m31、m41、m34、m43均为nmos管;

10.所述mos管m12、m22、m13、m24、m32、m42、m33、m44均为pmos管

11.所述时钟信号clk1、clk2由时钟电路产生,所述时钟电路为非交叠式时钟电路,包括mos管m51、m52、m53、m54、逻辑或非门f11、f21、逻辑非门f12、 f13、f14、f21、f22、f23、f24,所述mos管m51与m52构成第一反相器,所述mos管m53与m54构成第二反相器,所述mos管m51、m52的基极分别连接所述逻辑非门m22的输出端、逻辑非门f23的输入端,所述mos管m51、m52的集电极连接所述逻辑或非门f11的输入端1端口,所述逻辑或非门f11的输入端 2端口连接时钟信号clka,所述mos管m53、m54的基极分别连接所述逻辑非门 f12的输出端、逻辑非门f13的输入端,所述mos管m53、m54的集电极连接所述逻辑非门f21的输入端1端口,所述逻辑非门21的输入端2端口连接时钟信号clkb,所述逻辑或非门f11的输出端顺次连接串联的所述逻辑非门f12、f13、 f14,所述逻辑或非门f21的输出端顺次连接串联的所述逻辑非门f22、f23、 f24,所述逻辑非门f14的输出端输出时钟信号clk2,所述逻辑非门f24的输出端输出时钟信号clk1;所述mos管m51、m53的发射极分别连接电压源vdd,所述mos管m52、m54的发射极均接地;

12.所述mos管m51、m53均为pmos管,所述mos管m52、m54均为nmos管;

13.所述互补时钟信号由互补时钟信号产生电路产生,所述互补时钟信号产生电路包括mos管m26~m30,所述mos管m26、m29的栅极均连接时钟信号clk,所述mos管m26、m27、m28的源极均连接电压源vddh,所述mos管m26漏极分别连接mos管m29漏极、mos管m27、m30栅极,并输出时钟信号clka,所述 mos管m27漏极分别连接所述mos管m30漏极、mos管m28、m31栅极,并输出时钟信号clkb,所述mos管m29、m30、m31源极均接地;

14.所述mos管m26、m27、m28均为pmos管,所述mos管m29、m30、m31均为 nmos管。

15.一种射频开关芯片,其包括依次连接的驱动电压模块、电平转换模块、射频开关,所述驱动电压模块包括正压电荷泵、负压电荷泵,所述正压电荷泵用于为所述电平转换模块提供正压,所述负压电荷泵用于为所述电平转换单元提供负压,所述电平转换模块用于将所述正压、负压转换为的控制电压,所述控制电压用于对所述射频开关中开关的开启或关闭进行控制,其特征在于,所述负压电荷泵为上述三倍负压电荷泵,用于为所述电平转换单元提供三倍负压电荷泵。

16.采用本实用新型上述结构可以达到如下有益效果:该三倍负压电荷泵中一级负压电荷泵包括两个电容:第一电容c1、第二电容c2,即时钟信号clk1、 clk2通过相应的第一电容c1、第二电容c2即可实现充放电,相比于一级负压电荷泵中需要设置四个电容的方式,电容数量减少,从而减小了电容的占用面积和制作工艺复杂度。该三倍负压电荷泵中,二级负压电荷泵的驱动电压由一级负压电荷泵提供,因此,其无需设置额外的辅助电路即可满足二级负压电荷泵的驱动需求,辅助电路的减少也减小了整个集成电路系统的尺寸,从而满足了集成电路的高度集成化、微型化要求。

17.将该三倍负压电荷泵应用于射频开关芯片中,通过三倍负压电荷泵中的一级负压电荷泵与二级负压电荷泵级联,产生三倍负压,从而为射频开关的开启或关闭提供充足的电压,确保了射频开关芯片中的开关能够稳定开启或关闭。

附图说明

18.图1为目前常用两倍负压电荷泵的电路原理图;

19.图2为本技术三倍负压电荷泵的电路原理图;

20.图3为本技术非交叠时钟信号产生电路的电路原理图;

21.图4为本技术互补时钟信号产生电路的电路原理图;

22.图5为本技术三倍负压电荷泵的输入电压vdd、时钟信号clk及输出端vneg 输出三倍负压的仿真效果图。

具体实施方式

23.为了使本技术领域的人员更好地理解本实用新型方案,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分的实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本实用新型保护的范围。

24.需要说明的是,本实用新型的说明书和权利要求书及上述附图中的术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、装置、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

25.图1为目前常用的两倍负压电荷泵电路结构,从该图中可以看出,其包含四个电容c10、c20、c30、c40,三倍负压电路由该两个两倍负压电荷泵构成,每个负压电荷泵中设置有四个电容,四个电容的设置不仅占用了整个系统较多的空间面积,而且四个电容匹配度需保持一致,增大了工艺复杂度。另外,两个两倍负压电荷泵级联时,需要设置额外的辅助电路为二级负压电荷泵提供驱动电压,辅助电路的设置进一步增大了整个系统的尺寸。

26.针对目前存在的三倍负压电荷泵中多个电容以及辅助电路的设置占用了整个集成电路系统较多空间面积,无法满足集成电路高集成度、微型化要求的问题,以及每级负压电荷泵中四个电容的匹配度需保持一致,增大了工艺复杂度的问题,本实用新型提供了一种三倍负压电荷泵的具体实施例。

27.见图2,该三倍负压电荷泵包括一级负压电荷泵、二级负压电荷泵,一级负压电荷泵与二级负压电荷泵级联,一级负压电荷泵包括第一电容c1、第二电容c2、第一开关单元、第二开关单元,二级负压电荷泵包括第三电容c3、第四电容c4、第三开关单元、第四开关单元;第一开关单元包括mos管m11、m12、 m13、m14,第二开关单元包括mos管m21、m22、m23、m24,第一电容c1的一端连接时钟信号clk1,另一端分别连接mos管m11的发射极、mos管m12的集电极、mos管m23的发射极、mos管m13与m14的基极、第三电容c3一端、mos 管m41的集电极、mos管m42的发射极、mos管m44的发射极;第二电容c2的一端连接时钟信号clk2,另一端分别连接mos管m21的发射极、mos管m22的集电极、mos管m14的发射极、mos管m23与m24的基极、第四电容c4一端、 mos管m31的集电极、mos管m32的发射极、mos管m33的发射极。

28.第三电容c3的另一端分别连接mos管m31的发射极、mos管m32的集电极、 mos管m43的发射极、mos管m34与m33的基极、二极管d1的阴极,第四电容 c4的另一端分别连接mos管m41的发射极、mos管m42的集电极、mos管m34 的发射极、mos管m43与m44的基极、二极管d2的

阴极;二极管d1、d2的阳极连接后分别连接电容c5一端、输出端vneg,电容c5另一端接地。

29.本实施例中,mos管m11、m21、m14、m23、m31、m41、m34、m43均为nmos 管;mos管m12、m22、m13、m24、m32、m42、m33、m44均为pmos管。

30.见图3,时钟信号clk1、clk2由时钟电路产生,时钟电路为非交叠式时钟电路,包括pmos管m51、m53、nmos管m52、m54、逻辑或非门f11、f21、逻辑非门f12、f13、f14、f21、f22、f23、f24,mos管m51与m52构成第一反相器, mos管m53与m54构成第二反相器,mos管m51、m52的基极分别连接逻辑非门 m22的输出端、逻辑非门f23的输入端,mos管m51、m52的集电极连接逻辑或非门f11的输入端1端口,逻辑或非门f11的输入端2端口连接时钟信号clka, mos管m53、m54的基极分别连接逻辑非门f12的输出端、逻辑非门f13的输入端,mos管m53、m54的集电极连接逻辑非门f21的输入端1端口,逻辑非门21 的输入端2端口连接时钟信号clkb,逻辑或非门f11的输出端顺次连接串联的逻辑非门f12、f13、f14,逻辑或非门f21的输出端顺次连接串联的逻辑非门 f22、f23、f24,逻辑非门f14的输出端输出时钟信号clk2,逻辑非门f24的输出端输出时钟信号clk1;mos管m51、m53的发射极分别连接电压源vdd,mos 管m52、m54的发射极均接地;本实施例中,mos管m51、m53均为pmos管,mos 管m52、m54均为nmos管。时钟信号clk经互补时钟信号产生电路产生互补的时钟信号clka、clkb,互补时钟信号产生电路的具体结构见图4,互补时钟信号产生电路包括pmos管m26~m28、nmos管m29~m31,由pmos管m26与nmos管 m29、pmos管m27与nmos管m30、pmos管m28与nmos管m31分别组成逻辑非门,通过逻辑非门反相产生互补的的时钟信号clka、clkb,再经非交叠时钟信号产生电路产生非交叠的时钟信号clk+、clk-,非交叠时钟信号产生电路见图 3,该电路通过pmos管与nmos管组成的逻辑非门、逻辑或非门、逻辑非门以及交叉结构的作用,使互补时钟信号不在同一时刻输出,从而产生互补非交叠的时钟信号clk+、clk-。

31.应用上述三倍负压电荷泵产生三倍负压,具体步骤包括:s1、时钟电路产生的非交叠时钟信号clk1、clk2分别输入至相应的第一电容c1、第二电容c2 一端;同时第一电容c1的一端输入电压vdd,第二电容c2的一端接地,本实施例中电压vdd为1.8v,则第一电容c1另一端的电压为0v,第二电容c2一端电压为0v,则第二电容c2另一端电压为-1.8v;

32.s2、当第一电容c1一端输入电压为1.8v、第二电容c2一端电压为0v时, nmos管m11、m21导通,pmos管m13与m23、nmos管m14与m24关闭;此时,c 点电压为0v,d点电压为-1.8v;

33.s3、根据电容两端信号切换,电容的电压无法突变的原理,当第一电容c1、第二电容c2输入端的信号切换时,即第一电容c1输入时钟信号clk2、0v电压,第二电容c2输入时钟信号clk1、1.8v电压时,第一电容c1、第二电容c2另一端的电压分别为-1.8v、0v,此时,mos管m22、m23、m12、m14导通,mos 管m11、m21关闭;此时,c点电压为-1.8v,d点电压为0v;

34.s4、当第一电容c1、第二电容c2输入端的信号再次切换时,即第一电容 c1输入时钟信号clk1、1.8v电压,第二电容c2输入时钟信号clk2、0v电压时,第一电容c1、第二电容c2另一端的电压分别为-1.8v、0v,此时,mos管 m22、m23、mos管m24关闭、mos管m12、m14关闭,mos管m13导通,mos管 m11、m21关闭,此时,c点电压为-1.8v,d点电压为0v;

35.同理,s5、当c点电压为0v,d点电压为-1.8v时,第三电容c3另一端电压为-1.8v,第四电容c4另一端电压为-3.6v,nmos管m31、m41导通,pmos 管m33与m43、nmos管m34与m44关闭,a点电压为-1.8v,b点电压为-3.6v,二极管d2截止,输出端vneg输出电压-3.6v;

36.s6、当c点电压为-1.8v,d点电压为0v时,第三电容c3另一端电压-3.6v,第四电容c4另一端电压为-1.8v,此时,mos管m42、m43、m32、m34导通,mos 管m31、m41关闭;此时,a点电压为-3.6v,b点电压为-1.8v,二极管d1截止,二极管d2导通,输出端vneg输出电压-3.6v;

37.s7、c点电压为-1.8v,d点电压为0v时,第三电容c3另一端电压为-3.6v,第四电容c4另一端电容为-1.8v,此时,mos管m42、m43、mos管m44关闭、 mos管m32、m34关闭,mos管m33导通,mos管m31、m41关闭,二极管d1导通,二极管d2截止,因此,输出端vneg输出电压为:-3.6v+0.7v+0.2v=-2.7v, 0.7v为二极管d1或d2的管压降,0.2v为整个三倍负压电荷泵的内部损耗,因此,该三倍负压电荷泵最终输出的电压为-2.7v。

38.依次循环上述步骤s1、s2与s5、s3与s6、s4与s7,使输出端vneg连续输出-3.6v电压,该一级负压电荷泵、二级负压电荷泵中分别包含有两个电容,相比于每级负压电荷泵中包含有四个电容的方式,该三倍负压电荷泵中的电容数量显著减少,整个三倍负压电荷泵电路中,电容占用了较大的面积,因此,电容的减少了占用面积,满足了集成电路的高度集成化、微型化要求,同时使两个电容性能保持一致比使同一电荷泵中四个电容性能保持一致更容易制作,因此,降低了工艺难度。

39.图5给出了采用本技术三倍负压电荷泵的输入电压vdd与输出端vneg输出三倍负压的仿真效果图,图5中横轴表示时间dx,纵轴分别表示输入电压vdd、时钟信号clk、输出端输出的三倍负压vneg,曲线b表示时钟信号clk的变化情况,曲线a、c分别表示输入电压vdd、输出的三倍负压vneg在时钟信号clk 产生的非交叠的时钟信号clk+、clk-控制作用下的变化情况,时间dx=253ns 为一个时钟周期,从图5可以看出,在一个时钟周期内,随着输入电压vdd的变化,该三倍负压电荷泵输出的三倍负压vneg随之变化,并且能够连续输出稳定的负电压信号,并且,该负电压信号能够达到约2.7v,满足后续射频开关的控制要求。

40.将上述三倍负压电荷泵应用于射频开关芯片中,射频开关芯片包括依次连接的驱动电压模块、电平转换模块、射频开关,驱动电压模块包括正压电荷泵、负压电荷泵,正压电荷泵用于为电平转换模块提供正压,负压电荷泵为上述三倍负压电荷泵,用于为电平转换单元提供负压,电平转换模块用于将正压、负压转换为的控制电压,控制电压用于对射频开关中开关的开启或关闭进行控制。通过三倍负压电荷泵中的一级负压电荷泵与二级负压电荷泵级联,产生三倍负压,从而为射频开关的开启或关闭提供充足的电压,确保了射频开关芯片中的开关能够稳定开启或关闭。

41.以上的仅是本技术的优选实施方式,本实用新型不限于以上实施例。可以理解,本领域技术人员在不脱离本实用新型的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1