一种基于ESD防护的GPIO电路的制作方法

一种基于esd防护的gpio电路

技术领域

1.本实用新型涉及半导体技术领域,更为具体地说,涉及一种基于esd(electrostatic discharge,静电释放)防护的gpio(general-purpose input/output,通用输入输出)电路。

背景技术:

2.esd保护器件是芯片esd保护设计中最核心的最小单元,esd器件的设计成功与否直接关系到整个芯片保护设计能否顺利完成。在esd事件发生时,起保护作用的esd防护器件要承受大电流与高电压,而在大电流与高电压的情况下,半导体器件的工作方式会发生很大的变化。esd事件是短时间的大电流放电事件,因此研究esd防护器件非常有必要。现有的gpio电路一般直接利用其输出电路中的nmos和pmos作为esd防护结构,其对esd防护能力较差,并且因为同时有nmos和pmos而增大了闩锁效应的风险。

技术实现要素:

3.有鉴于此,本实用新型提供了一种基于esd防护的gpio电路,有效解决了现有存在的技术问题,不仅提高了gpio电路的esd防护能力,还有效避免了闩锁效应的风险。

4.为实现上述目的,本实用新型提供的技术方案如下:

5.一种基于esd防护的gpio电路,包括:电极引脚;与所述电极引脚电连接的输出电路和esd防护电路;以及,与所述esd防护电路电连接的输入电路;

6.所述esd防护电路包括多指型ggnmos器件、第一电阻至第n电阻和二极管;所述多指型ggnmos器件包括第一子ggnmos至第n子ggnmos,第i电阻包括第一子电阻和第二子电阻,第i子ggnmos的漏极与所述电极引脚电连接,所述第i子ggnmos的栅极与所述第i电阻的第一子电阻和第二子电阻的第一端电连接,所述第一子电阻的第二端、所述第二子电阻的第二端和所述第i子ggnmos的源极均电连接接地端;所述二极管的阴极与所述电极引脚电连接,所述二极管的阳极电连接接地端,n为不小于2的整数,i为不大于n的正整数。

7.可选的,所述第i电阻为非金属硅化物多晶硅电阻;

8.所述第一子电阻和所述第二子电阻与所述第i子ggnmos的栅极通过多晶硅电连接,且所述第一子电阻和所述第二子电阻分别电连接于所述第i子ggnmos的栅极的在第一方向上的两端部,所述第一方向与所述第i子ggnmos的栅极的延伸方向平行。

9.可选的,所述gpio电路包括:环绕所述多指型ggnmos器件和所述第一电阻至第n电阻的p+保护环,及环绕所述p+保护环的n+保护环;

10.所述p+保护环的掺杂类型与所述多指型ggnmos器件的衬底的掺杂类型相同,且所述p+保护环的掺杂浓度大于所述多指型ggnmos器件的衬底的掺杂浓度,所述n+保护环的掺杂类型与所述p+保护环的掺杂类型相反。

11.可选的,在所述第一方向和第二方向上,所述p+保护环的宽度相同,所述第一方向和所述第二方向相垂直。

12.可选的,所述esd防护电路还包括二级ggnmos、三级ggnmos、第一分压电阻、第二分压电阻、二级电阻和三级电阻;

13.所述一分压电阻的第一端与所述电极引脚电连接,所述第一分压电阻的第二端、所述二级ggnmos的漏极和所述第二分压电阻的第一端相电连接,所述二级ggnmos的栅极与所述二级电阻的第一端电连接,所述二级电阻的第二端与所述二级ggnmos的源极电连接接地端;

14.所述第二分压电阻的第二端与三级ggnmos的漏极和所述输入电路电连接,所述三级ggnmos的栅极与所述三级电阻的第一端电连接,所述三级电阻的第二端与所述三级ggnmos的源极电连接接地端。

15.可选的,所述三级电阻为位于所述三级ggnmos所在衬底上的n型diff电阻。

16.可选的,在所述gpio电路的厚度方向上,所述多指型ggnmos器件、第一电阻至第n电阻、二极管、二级ggnmos、第一分压电阻和二级电阻均位于所述电极引脚的下方。

17.可选的,所述输出电路包括第一nmos至第mnmos、第一pmos至第mpmos、第一n侧电阻至第mn侧电阻、第一p侧电阻至第mp侧电阻和衬底电阻,m为不小于2的整数;

18.第jpmos的源极和所述衬底电阻的第一端电连接电源端,所述衬底电阻的第二端与所述第jpmos的衬底电连接,第jpmos的漏极与第jp侧电阻的第一端电连接,第jp侧电阻的第二端与所述电极引脚电连接,第jpmos的栅极与p侧驱动子电路的输出端电连接,j为不大于m的正整数;

19.第jnmos的源极电连接接地端,第jnmos的漏极与第jn侧电阻的第一端电连接,第jn侧电阻的第二端与所述电极引脚电连接,第jnmos的栅极与n侧驱动子电路的输出端电连接。

20.可选的,所述多指型ggnmos器件、第jnmos、电阻区、第jpmos和电路区在第一方向上依次设置,所述电阻区至少包括第jp侧电阻和第jn侧电阻,第一方向与所述第i子ggnmos的栅极延伸方向相平行。

21.可选的,所述gpio电路还包括与所述电极引脚电连接的辅助电路,所述辅助电路包括辅助nmos、辅助pmos和辅助电阻,所述辅助电阻的第一端与所述电极引脚电连接,所述辅助电阻的第二端与所述辅助nmos的漏极和辅助pmos的漏极电连接,所述辅助pmos的源极与电源端电连接,所述辅助nmos的源极电连接接地端。

22.相较于现有技术,本实用新型提供的技术方案至少具有以下优点:

23.本实用新型提供了一种基于esd防护的gpio电路,esd防护电路包括多指型ggnmos器件和二极管。进而,通过多指型ggnmos器件和二极管实现gpio电路的esd防护,提高了gpio电路的esd防护能力。并且多指型ggnmos器件仅包括nmos,有效避免了闩锁效应的风险。

附图说明

24.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

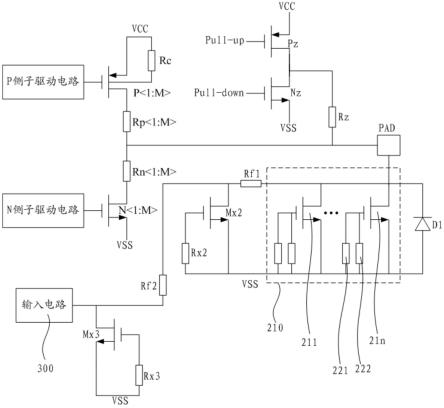

25.图1为本实用新型实施例提供的一种基于esd防护的gpio电路的等效电路图;

26.图2为本实用新型实施例提供的一种子ggnmos与连接第一子电阻和第二子电阻的版图;

27.图3为本实用新型实施例提供的一种基于esd防护的gpio电路的版图

具体实施方式

28.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

29.正如背景技术所述,esd保护器件是芯片esd保护设计中最核心的最小单元,esd器件的设计成功与否直接关系到整个芯片保护设计能否顺利完成。在esd事件发生时,起保护作用的esd防护器件要承受大电流与高电压,而在大电流与高电压的情况下,半导体器件的工作方式会发生很大的变化。esd事件是短时间的大电流放电事件,因此研究esd防护器件非常有必要。现有的gpio电路一般直接利用其输出电路中的nmos和pmos作为esd防护结构,其对esd防护能力较差,并且因为同时有nmos和pmos而增大了闩锁效应的风险。

30.基于此,本实用新型实施例提供了一种基于esd防护的gpio电路,有效解决了现有存在的技术问题,不仅提高了gpio电路的esd防护能力,还有效避免了闩锁效应的风险。

31.为实现上述目的,本实用新型实施例提供的技术方案如下,具体结合图1至图3对本实用新型实施例提供的技术方案进行详细的描述。

32.结合图1至图3所示,图1为本实用新型实施例提供的一种基于esd防护的gpio电路的等效电路图,图2为本实用新型实施例提供的一种子ggnmos与连接第一子电阻和第二子电阻的版图,及图3为本实用新型实施例提供的一种基于esd防护的gpio电路的版图。

33.本实用新型实施例提供的gpio电路包括:电极引脚pad;与所述电极引脚pad电连接的输出电路和esd防护电路;以及,与所述esd防护电路200电连接的输入电路300;

34.所述esd防护电路包括多指型ggnmos器件210、第一电阻至第n电阻和二极管d1;所述多指型ggnmos器件210包括第一子ggnmos211至第n子ggnmos21n,第i电阻包括第一子电阻221和第二子电阻222,第i子ggnmos的漏极与所述电极引脚pad电连接,所述第i子ggnmos的栅极与所述第i电阻的第一子电阻221和第二子电阻222的第一端电连接,所述第一子电阻221的第二端、所述第二子电阻222的第二端和所述第i子ggnmos的源极均电连接接地端vss;所述二极管d1的阴极与所述电极引脚pad电连接,所述二极管d1的阳极电连接接地端vss,n为不小于2的整数,i为不大于n的正整数。

35.如图2所示,本实用新型实施例提供的多指型ggnmos器件210包括p型衬底,p型衬底上包括有n个ggnmos,任意一子ggnmos包括n型重掺杂的漏极201和源极202,漏极201和源极202之间设有沟道和栅极203,栅极203为多晶硅形成。其中,至少部分ggnmos共用漏极201,以及每个ggnmos的栅极203和源极202电连接接地端vss。

36.在本实用新型一实施例中,本实用新型提供的第一子电阻和第二子电阻的阻止可以为1k-2kω。子ggnmos上的寄生电容cdg和第一子电阻与第二子电阻构成了rc电路;在esd放电时,前期快速上升的esd电压耦合到子ggnmos的栅极上的电压能让其导通,有一部分电

流流过,然后随着esd电压的变化率减小,子ggnmos的沟道关闭,随后寄生的npn导通成为主要的放电通路;由于本技术提供的所有子ggnmos的栅极的连接结构相同,均是连接第一子电阻和第二子电阻后电连接接地端,因此能提升均匀导通性,提高多指型ggnmos器件的可靠性。同时,当负静电电压打到电极引脚上时,由于二极管的存在,能够加强负静电esd电流的泄放,提升负静电防护能力。

37.由上述内容可知,本实用新型提供的技术方案,esd防护电路包括多指型ggnmos器件和二极管。进而,通过多指型ggnmos器件和二极管实现gpio电路的esd防护,提高了gpio电路的esd防护能力。并且多指型ggnmos器件仅包括nmos,有效避免了闩锁效应的风险。

38.在本实用新型一实施例中,本实用新型提供的所述第i电阻为非金属硅化物多晶硅(unsalicide poly)电阻,亦即第一子电阻和第二子电阻均为非金属硅化物多晶硅电阻。

39.如图2所示,所述第一子电阻221和所述第二子电阻222与所述第i子ggnmos的栅极通过多晶硅223电连接,且所述第一子电阻221和所述第二子电阻222分别电连接于所述第i子ggnmos的栅极203的在第一方向y上的两端部,所述第一方向y与所述第i子ggnmos的栅极203的延伸方向平行。其中,多晶硅223在第一方向y上的两侧边,与第一方向y的夹角可以设置为45度,对此本实用新型不做具体限制。

40.可以理解的,本实用新型提供的每个子ggnmos的栅极的两端分别电连接第一子电阻和第二子电阻,子ggnmos、第一子电阻和第二子电阻形成一个重复单元,该重复单元的版图在第二方向上均匀排列,提升了多指型ggnmos器件的均匀导通性,提高了多指型ggnmos器件的可靠性。

41.进一步如图3所示,本实用新型提供的所述gpio电路包括:环绕所述多指型ggnmos器件210和所述第一电阻至第n电阻的p+保护环230,及环绕所述p+保护环230的n+保护环240。

42.所述p+保护环230的掺杂类型与所述多指型ggnmos器件210的衬底的掺杂类型相同,且所述p+保护环230的掺杂浓度大于所述多指型ggnmos器件210的衬底的掺杂浓度,所述n+保护环240的掺杂类型与所述p+保护环230的掺杂类型相反。可选的,在所述第一方向y和第二方向x上,所述p+保护环230的宽度相同,所述第一方向y和所述第二方向x相垂直。

43.可以理解的,本实用新型实施例提供的技术方案,p+保护环朝向多指型ggnmos器件的内轮廓线至多指型ggnmos器件外轮廓线的各处距离基本一致,这样能够使得子ggnmos同一位置寄生的npn的rbe电阻尽可能大小一致,提升寄生npn导通的均匀性,提升多指型ggnmos器件的esd的放电能力。同时,当负静电电压打到电极引脚上时,子ggnmos寄生的体二极管会正偏泄放电流,为了增加子ggnmos寄生npn的rbe电阻,降低子ggnmos寄生npn的开启电压,p+保护环与子ggnmos的漏极有一定的间距,使得这个寄生的体二极管放电能力有限,因此,通过电连接于电极引脚和接地端之间的二极管,能够加强负静电esd电流的泄放,提升负静电防护能力。

44.如图1所示,本实用新型实施例提供的所述esd防护电路还包括二级ggnmosmx2、三级ggnmosmx3、第一分压电阻rf1、第二分压电阻rf2、二级电阻rx2和三级电阻rx3;

45.所述一分压电阻rf1的第一端与所述电极引脚pad电连接,所述第一分压电阻rf1的第二端、所述二级ggnmosmx2的漏极和所述第二分压电阻rf2的第一端相电连接,所述二级ggnmosmx2的栅极与所述二级电阻rx2的第一端电连接,所述二级电阻rx2的第二端与所

述二级ggnmosmx2的源极电连接接地端vss。

46.所述第二分压电阻rf2的第二端与三级ggnmosmx3的漏极和所述输入电路300电连接,所述三级ggnmosmx3的栅极与所述三级电阻rx3的第一端电连接,所述三级电阻rx3的第二端与所述三级ggnmosmx3的源极电连接接地端vss。

47.可以理解的,本实用新型实施例提供的esd防护电路还采用了二级和三级esd防护,三级ggnmos还串联有第二分压电阻,故而第一分压电阻不用太大,第一分压电阻的阻值可以小于第二分压电阻的阻值,这样当esd电流经过多指型ggnmos器件泄放后,电压还比较高的时候,二级ggnmos会开启泄放电流,通过第一分压电阻分压后,第一分压电阻第二端路径上的电压会降低很多。二级ggnmos开启后也会泄放比较大的静电电流,在所述gpio电路的厚度方向上,本实用新型实施例提供的所述多指型ggnmos器件、第一电阻至第n电阻、二极管、二级ggnmos、第一分压电阻和二级电阻均可以位于所述电极引脚的下方,进而使得二级ggnmos上的静电电流能够很好的泄放。三级esd防护可以选取尺寸较小的三级ggnmos和阻值较大的第二分压电阻,本实用新型提供的三级ggnmos可以与输入电路的nmos放置于一起,这样三级ggnmos和输入电路的nmos的衬底可以共用,对输入侧放电起到防护作用。

48.在本实用新型一实施例中,本实用新型提供的所述三级电阻为位于所述三级ggnmos所在衬底上的n型diff电阻,这样三级电阻与p型衬底也寄生了一个二极管而提升esd防护能力。

49.如图1所示,本实用新型实施例提供的所述输出电路包括第一nmos至第mnmosn《1:m》、第一pmos至第mpmosp《1:m》、第一n侧电阻至第mn侧电阻rn《1:m》、第一p侧电阻至第mp侧电阻rp《1:m》和衬底电阻rc,m为不小于2的整数。

50.第jpmos的源极和衬底电阻rc的第一端电连接电源端vcc,衬底电阻rc的第二端与所述第jpmos的衬底电连接,第jpmos的漏极与第jp侧电阻的第一端电连接,第jp侧电阻的第二端与所述电极引脚pad电连接,第jpmos的栅极与p侧驱动子电路的输出端电连接,j为不大于m的正整数。

51.第jnmos的源极电连接接地端vss,第jnmos的漏极与第jn侧电阻的第一端电连接,第jn侧电阻的第二端与所述电极引脚pad电连接,第jnmos的栅极与n侧驱动子电路的输出端电连接。

52.可以理解的,本实用新型实施例提供的输出电路的输出线连接的是晶体管的漏极,故而可以直接连接电极引脚,这样也能够提升输出电路的驱动能力。同时,将晶体管和一电阻(nmos和n侧电阻、pmos和p侧电阻)串联后作为一个重复单元,而后将重复单元并联后形成一个强驱动的电路,这样pad到每个重复单元的电阻都较大,但是并联后又不会影响整体的驱动能力,不仅能够提升驱动线路的耐压性能,还节省了布线面积。本实用新型实施例提供的n侧电阻和p侧电阻均可以制备为非金属硅化物(unsalicide)n型diff电阻,其可以为方块电阻,占用面积较小;同时,还能够与p型衬底形成寄生二极管起到辅助放电的作用,提高esd防护能力。进一步的,本实用新型实施例提供的pmos的衬底不直接电连接电源端,而是通过衬底电阻电连接到电源端,迫使esd电流不流经pmos的衬底寄生二极管,避免了驱动线路内部器件的损坏的情况。

53.如图3所示,本实用新型实施例提供的所述多指型ggnmos器件210、第jnmosnj、电阻区250、第jpmospj和电路区260在第一方向y上依次设置,所述电阻区250至少包括第jp侧

电阻和第jn侧电阻,电路区260包括n侧子驱动电路和p侧子驱动电路,第一方向y与所述第i子ggnmos的栅极延伸方向相平行。

54.可以理解的,本实用新型实施例提供的多指型ggnmos器件、第一nmos至第mnmos、第一pmos至第mpmos、第一n侧电阻至第mn侧电阻、第一p侧电阻至第mp侧电阻、n侧子驱动电路和p侧子驱动电路在版图上的排列布局,尽可能的不浪费芯片面积的同时,加大了n型晶体管和p型晶体管之间的间距,同时通过保护环的设置,极大的避免了闩锁效应的影响。

55.进一步如图1所示,本实用新型实施例提供的所述gpio电路还包括与所述电极引脚电pad连接的辅助电路,所述辅助电路包括辅助nmosnz、辅助pmospz和辅助电阻rz,所述辅助电阻rz的第一端与所述电极引脚pad电连接,所述辅助电阻rz的第二端与所述辅助nmosnz的漏极和辅助pmospz的漏极电连接,所述辅助pmospz的源极与电源端vcc电连接,所述辅助nmosnz的源极电连接接地端vss。辅助pmospz的栅极接入上拉信号pull-up,辅助nmosnz的栅极接入下拉信号pull-down。如图3所示,本实用新型实施例提供的辅助电路270可以位于三级ggnmosmx3背离多指型ggmos器件210一侧。

56.本实用新型实施例提供了一种基于esd防护的gpio电路,esd防护电路包括多指型ggnmos器件和二极管。进而,通过多指型ggnmos器件和二极管实现gpio电路的esd防护,提高了gpio电路的esd防护能力。并且多指型ggnmos器件仅包括nmos,有效避免了闩锁效应的风险。

57.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本实用新型。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本实用新型的精神或范围的情况下,在其它实施例中实现。因此,本实用新型将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1