集成振荡抑制电路的功率模块及方法

本发明属于电力电子器件,尤其涉及一种集成振荡抑制电路的功率模块及方法。

背景技术:

1、以碳化硅(silicon carbide,sic) mosfet为代表的宽禁带半导体功率器件为电力电子技术的发展注入强大的活力。由于sic mosfet具有开关速度快、导通电阻低、工作温度高等优势,已逐渐代替si igbt,被广泛运用于电力牵引、光伏发电、智能电网等领域。然而,功率回路的杂散电感和负载的寄生电容将会为sic mosfet的高速特性造成极大的阻碍,由此会导致器件电压和电流发生超调和振荡,降低了电力系统的稳定性,剧烈的开关振荡会增加额外的功率损耗,这大大限制了其应用前景。因此,针对sic mosfet研究一种最优的方式来抑制开关振荡十分有必要。

2、当前,sic mosfet中不必要的开关振荡受到了广泛的关注。众多研究人员对sicmosfet产生的原理进行了详尽的分析,并提出了相应的办法来抑制开关振荡以及过电压;同时,针对解决方案对器件开关损耗也进行了分析。抑制sic mosfet开关振荡的方法主要分为以下几类:

3、(1)通过优化电路板布局和器件的封装结构来最小化功率环杂散电感,以缓解开关振荡持续时间和电压超调;

4、(2)通过增大门极电阻或者有源门极驱动的方式来降低开关速度,从而降低振荡、抑制电磁干扰,但无疑令sic mosfet失去自身优势,也会增大开关的开通、关断时间,进而增加开关损耗;

5、(3)采用外加缓冲电路的方式来抑制开关振荡和电压、电流的超调。

6、第(3)种方式是当前最为常用的方式。根据外加缓冲电路的位置,可将其分为主回路缓冲电路和耦合缓冲电路。主回路缓冲电路主要包括在功率回路中串联铁氧体磁珠、解耦电容,并联rc和c-rc缓冲电路方式,这些方式均能够通过缓冲电路的作用来抑制开关振荡,但是功率回路中插入额外的功率电感,将增加传导损耗和体积,而解耦电容会引起低频振荡,同时以上主回路缓冲电路均会增加开关的开通损耗和关断损耗。

7、耦合缓冲电路利用感应耦合原理来抑制主功率回路中的开关振荡,在抑制振荡的同时将缓冲损耗完全转移至二次侧,可以降低耦合缓冲电路的开关损耗,但是,耦合缓冲电路虽然十分具有优势,但其会造成一定的电压、电流过冲,易对器件造成一定的损伤,并且针对耦合线圈的设计仍有待商榷。

技术实现思路

1、本发明的目的在于提供一种集成振荡抑制电路的功率模块及方法,以解决传统功率模块振荡抑制效果不佳,开关损耗大,以及开关过程中存在电压过冲问题。

2、本发明是通过如下的技术方案来解决上述技术问题的:一种集成振荡抑制电路的功率模块,包括sic mosfet管q1、sic mosfet管q2、第一过压抑制单元、第二过压抑制单元、耦合电路、负载端子、dc-端子以及dc+端子;

3、所述sic mosfet管q1的漏极与所述dc+端子、第一过压抑制单元中电容c1的第一端、第二过压抑制单元中电感l2的第一端、第二过压抑制单元中电阻r2的第一端连接,其源极与所述负载端子、第一过压抑制单元中的二极管d1阴极、sic mosfet管q2的漏极以及第二过压抑制单元中二极管d2的阳极连接;所述sic mosfet管q2的源极与所述dc-端子、第二过压抑制单元中电容c2的第一端、第一过压抑制单元中电感l1的第一端、第一过压抑制单元中电阻r1的第一端连接;

4、所述耦合电路是由电阻rc与电感lc构成的回路,所述电感lc包括磁芯以及绕制在所述磁芯上的线圈;所述电感lc的磁芯与dc+端子通过电磁感应产生虚拟电感lv,或者所述电感lc的磁芯与dc+端子和dc-端子通过电磁感应产生虚拟电感lv。

5、进一步地,所述第一过压抑制单元包括二极管d1、电容c1、二极管d3、电感l1以及电阻r1;所述二极管d1的阳极与所述电容c1第二端、二极管d3的第一端、电阻r1的第二端连接;所述二极管d3的第二端与所述电感l1的第二端连接;

6、所述第二过压抑制单元包括二极管d2、电容c2、二极管d4、电感l2以及电阻r2;所述二极管d2的阴极与电容c2的第二端、二极管d4的第一端、电阻r2的第二端连接;所述二极管d4的第二端与所述电感l2的第二端连接。

7、进一步地,在所述sic mosfet管q1的漏极与源极并联有二极管d5;在所述sicmosfet管q2的漏极与源极并联有二极管d6。

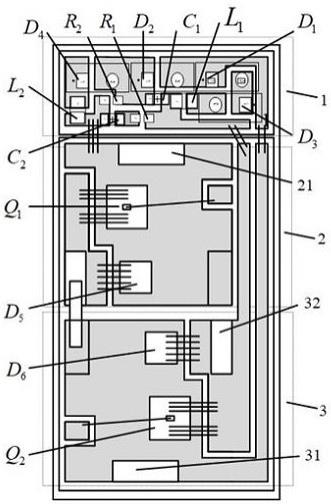

8、进一步地,所述sic mosfet管q1、sic mosfet管q2、第一过压抑制单元、第二过压抑制单元、负载端子、dc-端子以及dc+端子均设于dbc基板上;所述dbc基板沿长度方向依次划分第一区、第二区以及第三区;所述第一过压抑制单元、第二过压抑制单元设于第一区,所述sic mosfet管q1、dc+端子设于第二区,所述sic mosfet管q2、负载端子和dc-端子设于第三区;所述sic mosfet管q1、sic mosfet管q2、第一过压抑制单元、第二过压抑制单元之间通过铜层和/或键合线连接;

9、所述负载端子位于sic mosfet管q2的漏极所在铜层,所述dc-端子位于sicmosfet管q2的源极通过键合线所连接的铜层,所述dc+端子位于sic mosfet管q1漏极所在铜层。

10、进一步地,所述sic mosfet管q1、sic mosfet管q2、第一过压抑制单元、第二过压抑制单元以及dbc基板均设于封装外壳内;所述电阻rc、电感lc设于所述封装外壳上,且所述电感lc套设于穿过封装外壳的dc+端子、或dc+端子和dc-端子上。

11、进一步地,所述磁芯采用nizn铁氧体磁芯,所述线圈采用利兹线。

12、进一步地,所述电感lc的尺寸由所述虚拟电感lv的感值来确定,具体确定过程为:

13、通过仿真得到sic mosfet管的开关损耗与回路寄生电感之间的关系曲线,进而得到总开关损耗与回路寄生电感之间的关系曲线;

14、以所述总开关损耗与回路寄生电感之间的关系曲线的最低点所对应的电感值作为虚拟电感lv的最小感值;

15、根据所述虚拟电感lv的最小感值确定电感lc的尺寸,具体关系表达式为:

16、;

17、其中, u r为电感lc的磁性材料磁导率, u0为空气磁导率, h为电感lc的磁芯高度, r2为电感lc的磁芯内环半径或直径, r1为电感lc的磁芯外环半径或直径, l v为虚拟电感lv的感值。

18、基于同一构思,本发明还提供一种利用如上所述的功率模块进行振荡抑制的方法,包括以下步骤:

19、当所述功率模块通电后,直流母线电压升高,电阻r1对电容c1充电至直流母线电压vdc,电阻r2对电容c2充电至直流母线电压vdc;

20、当sic mosfet管q1接收到关断信号后,sic mosfet管q1的漏源电压vds逐渐升高,当漏源电压vds大于直流母线电压vdc时,二极管d1导通,漏源电压vds为电容c1充电,实现sicmosfet管q1的漏源极关断过电压抑制;当sic mosfet管q2接收到关断信号后,sic mosfet管q2的漏源电压vds逐渐升高,当漏源电压vds大于直流母线电压vdc时,二极管d2导通,漏源电压vds为电容c2充电,实现sic mosfet管q2的漏源极关断过电压抑制;

21、当sic mosfet管q1关断后,电容c1获取的过电压通过二极管d3和电感l1回馈至直流母线,直到电容c1的电压降至直流母线电压;当sic mosfet管q2关断后,电容c2获取的过电压通过二极管d4和电感l2回馈至直流母线,直到电容c2的电压降至直流母线电压;

22、当sic mosfet管q1或sic mosfet管q2接收到开通信号后,虚拟电感lv的引入使直流母线的寄生电感增大,sic mosfet管q1或sic mosfet管q2的漏源电压的变化量增大,当sic mosfet管q1或sic mosfet管q2的漏源电压的变化量接近sic mosfet管q1或sicmosfet管q2的漏源电压时,实现零电压开通。

23、有益效果

24、与现有技术相比,本发明的优点在于:

25、本发明耦合电路中电感lc的磁芯与dc端子通过电磁感应方式引入虚拟电感,通过虚拟电感增加直流母线的寄生电感来实现了sic mosfet管的零电压开通,降低了开关损耗,通过耦合电路中的电阻rc引入的虚拟阻尼达到了很好的振荡抑制效果;同时,利用过压抑制单元有效抑制了sic mosfet管关断过程中的过电压,有效减少了开关过程中的电压过冲。

26、本发明的元器件集成在dbc基板上,提高了功率模块的稳定性,节省了空间。本发明不仅适用于半桥模块,引入虚拟阻尼和过压抑制方式使其能够用于并联模块和三相模块。

- 还没有人留言评论。精彩留言会获得点赞!