一种快速负载响应的DC-DC升压变换器及电源管理系统

本发明涉及dc-dc升压变换器,特别是涉及一种快速负载响应的dc-dc升压变换器及电源管理系统。

背景技术:

1、在可移动设备(如万物互联iot、led驱动、pa包络跟踪)的电源管理芯片设计中,业界对dc-dc升压变换器(boost converter)的性能提出了更高的要求。特别地,在需要快速负载响应的应用中,当输出端负载电流快速变化时,升压变换器需要尽可能缩短响应时间以使输出电压迅速恢复稳态。其次,高效率是对一个电源管理芯片的基本需求,效率的提升意味着更长的芯片寿命和更高的能量转换率。而电压转换比的大小决定了升压变换器的适用范围的大小,如果某种升压变换器的电压转换比的理论极限过低,那么就意味着它的应用范围受限。现在的市场需求中,以锂电池为输入电压(2.7-4.2v)的升压变换器的输出电压往往高于5-6v,因此需要一个能提供相对较宽范围电压转换比的升压变换器。

2、传统拓扑结构的升压变换器(conventional boost converter)如图1所示,通过两个工作模态(φ1和φ2)的切换来完成升压。这种拓扑结构的主要缺陷是:从时域来看,当瞬态负载响应发生时,即负载电流io突然增大,增大的电流消耗了输出电容co上的电荷,因此输出电压vo会产生瞬态压降。由于电感需要被充电进而使得电感电流上升才能使升压变换器回到稳态,传统型变换器就需要更多的时间停留在φ1,而输出电容co在φ1下单独给输出端负载提供电流,这会使得输出电压vo进一步下降,然后随着电感电流逐渐恢复到稳态值,vo才逐渐恢复到稳态。因此,传统型升压变换器的瞬态响应过程会很慢,产生的电压降也较大。从频域来看,在传统型的小信号模型中,存在一个右边平面零点(right-half-plane zero,),如图1所示,这会使得增益以20db/dec的速度增加而相位以-45degree/dec的速度下降。这种性质在很大程度上限制了系统的带宽,并给频率补偿网络的设计带来困难。

3、图2展示了一种名为双通路升压变换器(dual path step-up converter)的拓扑结构,简称为dpuc。它可以将右半平面零点移至更高频率来获得更高的带宽并能降低电感平均电流来降低导通损耗。然而,dpuc只能将右半平面零点的位置向高频推移从而增加带宽,并未完全消除其带来的负面影响,因为只要右零点还存在,系统带宽的扩展仍会受限。dpuc的另一个缺点是削弱了电压转换比(conversion ratio)。如果φ1对应的占空比是d,φ2对应的占空比是1-d,那么dpuc的电压转换比为恒小于传统型的电压转换比另外,dpuc的拓扑结构需要两个耐压分别为vo和(2vo-vin)的高压管(图2中的s2和s1),而高压管带有更大的寄生电容和导通阻抗,这会使得效率降低。因此dpuc在开关管耐压上显示出了劣势。

4、如图2所示1-plus-d的升压变换器,它也可以实现消除右半平面零点的功能。然而,1-plus-d结构的缺陷在于其电压转换比的理论最大值无法超过2,如果考虑实际的电容硬充电损耗,其电压提升能力会进一步降低。因此,1-plus-d虽然有相比传统型和dpuc而言更好的动态性能,但应用范围非常受限。

5、此外,还存在其他可以移动甚至消除右半平面零点的拓扑结构,但需要不止一个电感和飞跨电容以及更多的开关管,这会在很大程度上提升成本、增加系统的体积(尤其是电感会使片外系统体积大大增加)并且降低效率,不适合可移动设备的芯片设计。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种单电感、单飞跨电容的快速负载响应dc-dc升压变换器及电源管理系统,同时具有宽范围电压转换比和高效率的特点。

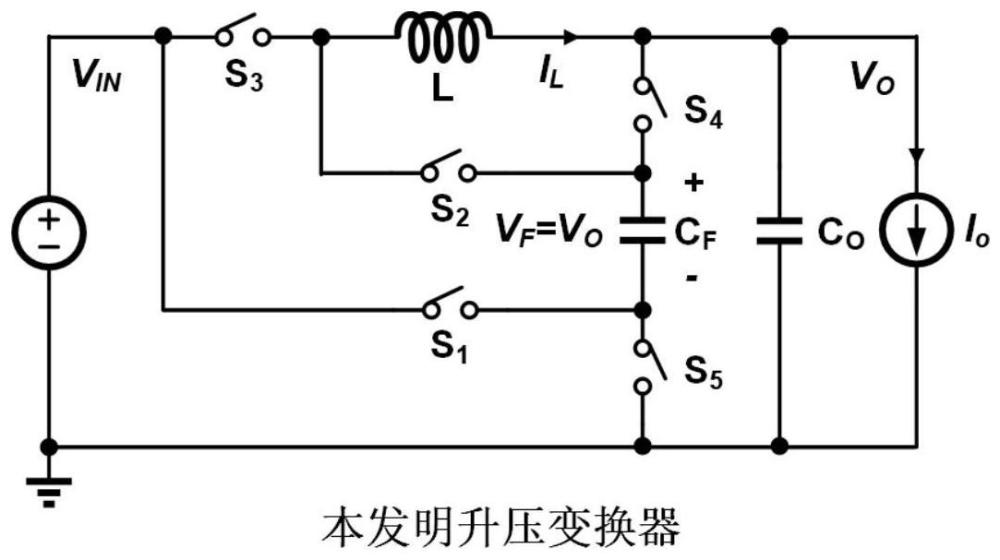

2、本发明的目的是通过以下技术方案来实现的:一种快速负载响应的dc-dc升压变换器,其特征在于:包括直流输入电压源vin、第一开关s1~第五开关s5、电感l、输出电容co、输出电流源io以及飞跨电容cf;

3、所述直流输入电压源vin的正极分别与第一开关s1和第三开关s3的第一端连接,直流输入电压源vin的负极接地;第一开关s1的第二端连接到飞跨电容cf的第二端;第三开关s3的第二端连接到电感l的第一端,电感l的第二端连接到负载电流源io的第一端,负载电流源io的第二端与直流输入电压源vin的负极连接;第二开关s2的第一端连接到电感l的第一端,第二开关s2的第二端连接到飞跨电容cf的第一端;

4、第四开关s4的第一端连接到负载电流源io的第一端,第四开关s4的第二端连接到飞跨电容cf的第一端,第五开关s5的第一端连接到飞跨电容cf的第二端,第五开关s5的第二端接地,所述输出电容co的一端与负载电流源io的第一端连接,另一端则与负载电流源io的第二端连接;所述负载电流源io的第一端和第二端之间的电压作为升压变换器的输出电压vo。

5、在本发明升压变换器的功率级中,电感l,飞跨电容cf和输出电容co是片外器件;开关s1~s5则由芯片内绝缘栅型场效应晶体管(mosfet)实现。开关s1~s2由p型mosfet实现而开关s3~s5由n型mosfet实现。

6、本发明的电源管理系统,包括控制子系统、驱动子系统和所述dc-dc升压变换器;

7、所述控制子系统包括分压电阻,基于误差放大器的type-ii补偿网络、时钟与斜坡生成电路、比较器、rs锁存器、死区时间保护模块和驱动逻辑电路模块;所述驱动子系统包括开关驱动器模块。

8、考虑到控制系统需要接入vdd工作电压,故驱动子系统还包括电平转换器模块,电平转换器模块采用传统的电平转换器将控制器的电压域0-vdd转移到功率级电压域0-vin之间,控制器的电源电压为vdd,用于给控制器内部的误差放大器、比较器和逻辑电路供电。由于vdd一般不用给大功率器件提供电流,而仅仅是给平均电流仅为不到2ma的控制器供电,因此可以从电源管理的系统中直接获取一个参考电位。本芯片在测试中选取vdd=5v,由一个片外电压源来提供。本发明升压变换器的控制子系统和驱动子系统同样完全在片内实现。

9、所述第一反馈分压电阻rf1的一端与输出电流源io的第一端连接,第一反馈分压电阻rf1的另一端通过第二反馈分压电阻rf2接地;所述误差放大器(error amplifier)的反向输入端连接到第一反馈分压电阻rf1和第二反馈分压电阻rf2之间;所述误差放大器的同相输入端用于输入参考电压vref。误差放大器的等效输出电阻为ro,ro等价于在误差放大器的输出端连接一个电阻至地,阻值约为几百千欧姆级别。并且误差放大器的输出端vea与rc和cc的串联支路相连从而构成type-ii补偿网络。vea和被斜坡生成电路生成的ramp信号比较之后形成方波信号vc,vc被输入到rs锁存器的reset端(r端口),时钟与斜坡生成电路输出的时钟信号(clk)传输到rs锁存器模块的set端口(s端口),rs锁存器模块的同相输出端(q端口)用于输出占空比为d的方波信号q,并传输到死区时间和驱动逻辑电路,rs锁存器模块的反向输出端口(q’端口)悬空。

10、方波信号在经过信号处理之后携带各个开关管的驱动电平信息和死区时间保护信息进入到控制开关驱动器模块中。在本技术的实施例中,死区时间保护模块产生一个足够时长的死区时间。考虑到真实的mosfet功率开关的导通与关断需要一定的响应时间,设置一个时长足够的死区时间段来保证在两个工作模态相互切换的瞬间,前一个模态的功率开关组完全关断之后,后一个模态的功率开关组再导通,避免产生短路电流。本发明使用数字逻辑延迟单元来设置死区时间以保证足够的切换延迟。

11、驱动逻辑电路模块,放置在电平转换器和开关驱动器模块的前一级,用来设定占空比为d的方波信号q与两个工作模态的功率开关组之间的对应关系:当q=1时,控制开关驱动器模块使得第一模态开关组导通;当q=0时,控制开关驱动器模块使得第二模态开关组导通;本发明的驱动逻辑电路模块用集成在芯片内部的数字逻辑单元实现,也可以使用fpga或其他逻辑电路实现。

12、所述开关驱动器模块用于控制开关的闭合或者关断,从而实现两个工作模态相互切换的稳态。开关驱动器模块中,s1和s5两个开关采用经典的反相器链驱动器,而s3和s4采用经典的电压自举型驱动器,开关s2的栅极可以直接连接在vo上进行自动开启与闭合,可以不需要设计特殊驱动以降低驱动电路的复杂度。

13、所述电源管理系统的控制子系统由电压模式的pwm控制方式实现。在每个周期开始之前,clk会将rs锁存器的set端置1一段时间(约10-20ns),这会使得q被置1并且ramp会掉落回vramp的最低点,在ramp回升至高于vea之前,vc一直为0,reset端一直无效,则q一直维持在1状态,在经过选通和驱动逻辑的处理之后会令开关s1和s2导通而开关s3、s4和s5断开,功率级进入φ1状态;然后当ramp回升至高于vea之后,vc变成1使得reset信号有效,从而q被强制置0,开关s1和s2断开而开关s3、s4和s5导通,功率级进入φ2状态;当误差放大器的正极信号vref上升时,vea也会随之上升,这会使得q=1在一个周期内的比例更大,也就会获得更高的输出电压vo。

14、本发明的有益效果是:相比于cbc,本发明具有相同的理论电压转换比,但可以实现快速负载响应;相比于dpuc和与1-plus-d型升压变换器,本发明提出的升压变换器的电压转换比范围更宽,且响应速度更快;本发明有且仅有一个开关管的耐压是vo,其他开关管的耐压均不会超过vin。这使得本发明所述的升压变换器可以更少使用高压管。在通常情况下,耐压超过6v的开关mosfet需要使用高压管来实现,而高压管的开关损耗和导通损耗要比低压管(一般指耐压在5v以下的开关mosfet)高出几倍。开关mosfet的耐压更小让本发明可实现高效率设计。

- 还没有人留言评论。精彩留言会获得点赞!