一种隔离耦合元件的制作方法

本发明涉及一种瞬态响应(str)交流/直流(ac/dc)转换器及其在高功率密度充电中的应用。str ac/dc转换器具有使用更小的变压器和电容器并提高性能的优点。结合独特的印刷电路板(pcb)设计和部件集成,组装成一个紧凑型功率传递(pd)充电器,为快速充电应用提供超过0.6w/cc的功率密度。

背景技术:

1、图1a是基于脉宽调制(pwm)控制反激ac/dc转换器的传统充电器的简化电路图。变压器tx1将从一次侧电源接收到的能量传输到二次侧,为负载供电。变压器tx1的初级线圈的第一端连接到变压器输入电压vbulk,一般是来自交流壁装电源插座的整流输出电压(整流电压)。变压器初级线圈的第二端连接到主开关q1,以调节通过变压器初级线圈的电流,以便将能量传输到变压器的次级侧。主控制器位于变压器的一次侧,用于控制主开关的接通和断开。一个反馈回路,其误差放大器位于变压器的次级侧,通过光耦将输出信息反馈给第一侧的控制器。如图1b所示,图1a中电路的工作频率在峰值负载时限制在65khz至85khz,脉宽调制控制器的控制带宽(bw)受电流模式控制环路带宽(bw~0.1×fs)约为开关频率的十分之一的限制。由于工作频率低,控制带宽窄,输出电压瞬态响应慢。图1c显示了负载在空载和100%负载之间过渡时,由于工作频率fs的缓慢过渡,输出电压、vout和瞬态响应的大波动。此外,对于传统的脉宽调制控制器,为了保持与负载状态变化对应的高转换效率,需要在连续导通模式(ccm)和中断导通模式(dcm)的不同操作模式之间切换脉宽调制控制器的操作。为了保持控制器的稳定运行,通常需要恒流补偿回路和恒压补偿回路。因此,传统的基于脉宽调制控制的反激式交直流转换器的充电器不可避免地需要额外的元件。

2、图1d和图1e分别显示了图1a传统充电器中常用的传统垂直mosfet晶体管的横截面图和俯视图。该晶体管的漏极d位于晶体管芯片的底面上,连接到引线框架芯片基座上,引线框架芯片基座底部表面暴露于封装中;源极和栅极位于晶体管芯片的顶面上,源极和栅极连接到源极引线s和栅极引线g。图1f显示了图1a的传统充电器的pcb布局10,pcb布局10配置为接收图1d和图1e的传统mosfet器件。传统mosfet器件具有小面积源极引线连接到pcb上的小铜垫11,大面积漏极引线14连接到pcb上的大铜垫12。mosfet芯片的漏极通过漏极引线14和铜垫区12之间的大接触区与变压器tx1连接,mosfet芯片的源极通过电阻r2接地。由于热耗散和电磁干扰(emi)降噪之间不可避免的折衷,pcb布局10的性能没有得到优化。mosfet器件q1会发热,需要一个大的铜垫区域12(例如,长度大于10mm,宽度大于5mm)进行冷却。然而,大面积漏极引线14具有高电压和高dv/dt值,它将emi噪声与系统耦合,这对于低压应用来说可能不是问题。然而,对于500v或更高电压应用,由于快速变化和高漏极电压,emi噪声很高,它需要一个小的铜垫区域12来降低电磁干扰噪声,这与需要使用更大的铜垫区域12进行冷却的要求相反。一个大的铜垫区域12的结果是产生的电磁干扰噪声大,为了满足规范要求,经常需要采用附加的大体积散热器和金属屏蔽来提高散热性能和射频干扰屏蔽。此外,对于高压应用,大面积的高压漏极引线需要较大的安全空间,因此增加了器件面积,使得在保持高电压安全空间的同时,最大限度地减小器件尺寸成为一项挑战。

3、便携式设备充电器的理想功能包括:提供安全充电而不损坏待充电设备的高性能、快速充电以节省时间和紧凑尺寸以节省空间以方便移动。这种理想的特性将迫使充电器使用较少的元件数量和较小尺寸的元件,如较小的变压器和较小的电容器,以处理更高的功率密度而不增加太多的成本。功率密度的增加会引起散热和电磁干扰问题,使用较小的部件或较少的部件数可能会影响充电器的性能。因此,目前市场上最好的充电器功率密度小于0.5w/cc。

技术实现思路

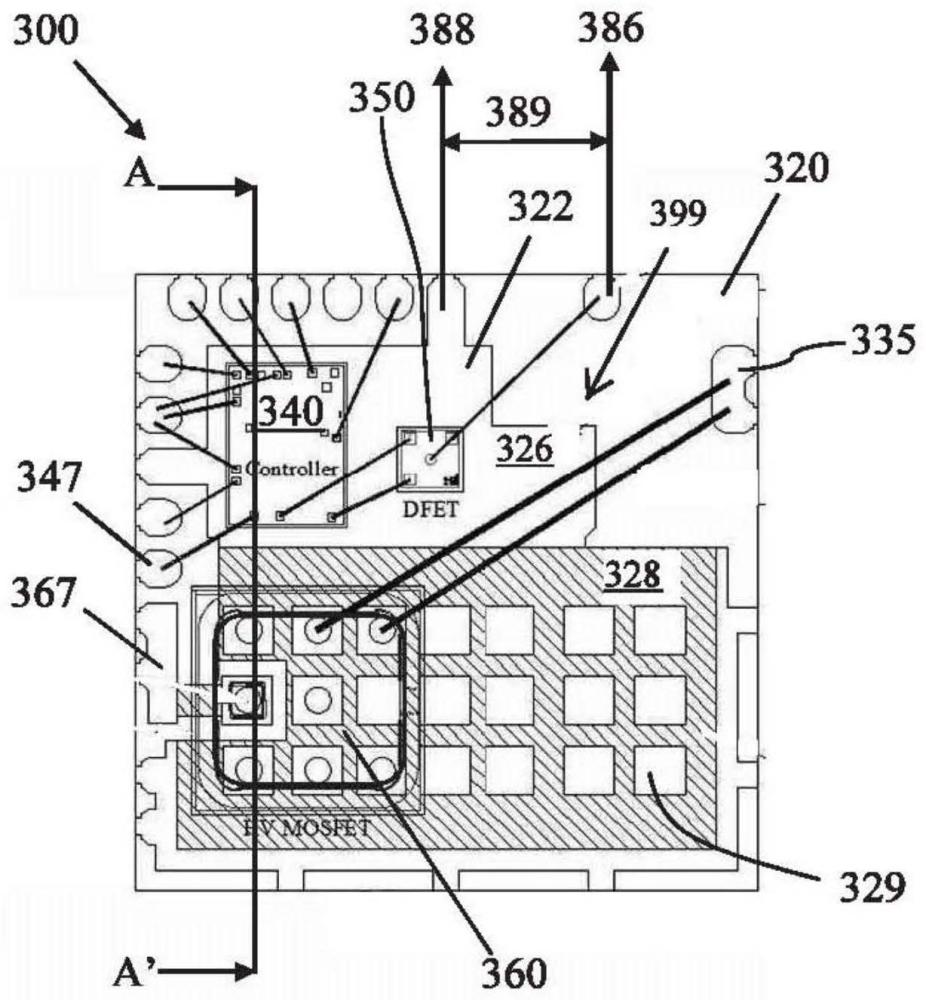

1、本发明提供了一种功率密度超过0.5w/cc的充电器,采用新颖的系统电路控制,将主开关和控制集成电路(ic)共同封装在单一芯片基座上,并使用四层印刷电路板(pcb)。因此,减少了电磁干扰,提高了热性能,实现了快速开启。

2、为了实现上述目的,本发明公开了一种交流/直流充电器,包括外壳、第一印刷电路板、第二印刷电路板、第三印刷电路板、第一插脚和第二插脚。所述第一印刷电路板包括初级侧电路,所述第二印刷电路板包括次级侧电路,所述第三印刷电路板垂直于第一印刷电路板和第二印刷电路板。第一印刷电路板和第二印刷电路板各包括高压半导体封装,第三个印刷电路板上布置有隔离耦合器。

3、本发明公开的高压半导体封装,包括:

4、一个引线框架,所述的引线框架包括

5、一个芯片基座,其包括源极接触区;

6、与所述芯片基座分离的栅极接触区;以及

7、与所述芯片基座和所述栅极接触区分离的漏极引线;

8、一个高压金属氧化物半导体场效应晶体管(mosfet)芯片,其包括

9、设置在高压mosfet芯片的顶面上的源极;

10、设置在高压mosfet芯片的顶面上的栅极;以及

11、设置在高压mosfet芯片的底面上的漏极,芯片底面与顶面相对;以及成型封装;

12、其中,高压mosfet芯片安置在所述引线框架上,高压mosfet芯片的顶面朝向所述引线框架,

13、其中,所述高压mosfet芯片的源极连接到所述芯片基座的源极接触区;

14、其中,所述高压mosfet芯片的栅极连接到所述栅极接触区;

15、其中,高压mosfet芯片的漏极与所述漏极引线电连接;

16、其中,所述成型封装包裹所述高压mosfet芯片和所述引线框架的大部分;

17、其中,所述芯片基座的至少一个底面从所述成型封装的底面暴露;

18、其中,所述芯片基座和所述漏极引线之间的最小间距不小于维持500伏或更高电压的预定爬电距离。

19、优选地,所述预定爬电距离为1.1mm。

20、优选地,所述芯片基座的源极接触区包括一个顶面,所述顶面包括一组凹槽。

21、优选地,所述凹槽阵列的深度在所述芯片基座厚度的百分之四十五至百分之五十五之间。

22、优选地,所述高压mosfet芯片的顶面覆盖有一个预成型材料,所述预成型材料包含连接所述高压mosfet芯片的源极和所述芯片基座之间的第一焊料凸点以及连接所述高压mosfet芯片的栅极与栅极接触区之间的第二焊料凸点。

23、优选地,所述的高压半导体封装还包括设置在芯片基座的dfet区域上的高压耗尽型场效应晶体管dfet芯片。

24、优选地,所述高压dfet芯片包括与所述引线框架的高压引线电连接的第一电极。

25、优选地,所述高压引线与连接到所述芯片基座的相邻引线之间的水平距离至少为1.1mm。

26、优选地,所述高压引线和所述漏极引线布置在靠近所述引线框架一个角落的相对侧。

27、优选地,所述的高压半导体封装还包括设置在芯片基座的ic区域上的集成电路ic芯片。

28、优选地,所述高压dfet芯片包括与所述引线框架的高压引线电连接的第一电极;其中所述高压引线和所述漏极引线布置在靠近所述引线框架的角的相对侧。

29、优选地,所述芯片基座的暴露的底面从源接触区连续延伸到所述dfet区和所述ic区。

30、优选地,所述芯片基座在靠近高压引线和漏极引线的拐角处具有逆l形切除区。

31、优选地,所述芯片基座的暴露底面的表面积至少为高压半导体封装底面的百分之八十。

32、优选地,所述高压半导体封装还包括设置在芯片基座的ic区域上的集成电路ic芯片。

33、优选地,所述集成电路ic芯片包括电连接到所述栅极接触区域的栅极驱动输出电极。

34、优选地,所述集成电路芯片包括栅极驱动输出电极,所述栅极驱动输出电极电连接到与栅极接触区分离的引线框架的栅极驱动引线。

35、本发明还公开了一个隔离耦合元件,包括:

36、一个多层印刷电路板pcb,其包括

37、上层;

38、下层;

39、一个初级线圈,其包括设置在上层外围区域上的第一匝数个导电迹线;

40、以及

41、一个次级线圈;

42、其中,所述次级线圈的第一部分包括设置在所述上层的内部区域上的第二匝数个导电迹线;

43、其中,所述次级线圈的第二部分包括布置在所述下层的第三匝数个导电迹线;

44、其中,所述隔离耦合元件的互感在100khz时大于50nh。

45、优选地,第一个导电迹线匝数与第二个导电迹线匝数加上第三个导电迹线匝数的匝数比为3:10。

46、优选地,所述的隔离耦合元件还包括顶层和底层;

47、其中所述上层和所述下层位于所述顶层和所述底层之间;

48、其中,设置在所述底层以提供外部连接的多个接触焊盘;和

49、其中,隔离耦合元件的尺寸不超过9.5mm×5.5mm×1.8mm。

50、本发明具有以下优势:

51、本发明的高压半导体封装利用mosfet倒装芯片封装技术,将mosfet晶体管和控制ic共同封装在单个芯片基座上。它提供了一个大面积的源电极,从封装的底面暴露出来,以提高热耗散,从而降低变压器一次侧和二次侧的电磁干扰。

- 还没有人留言评论。精彩留言会获得点赞!