一种放电电路、电源控制电路及放电控制方法与流程

本申请涉及显示,提供了一种放电电路、电源控制电路及放电控制方法。

背景技术:

1、在现有的超大尺寸显示产品中,由于负载原因下电时序无法满足设计要求,导致下电后面内电荷无法释放完全,出现电荷残留相关不良。

技术实现思路

1、本申请实施例提供一种放电电路、电源控制电路及放电控制方法,用以对供电电压信号端的电荷进行充分释放,提升产品的可靠性。

2、本申请提供的具体技术方案如下:

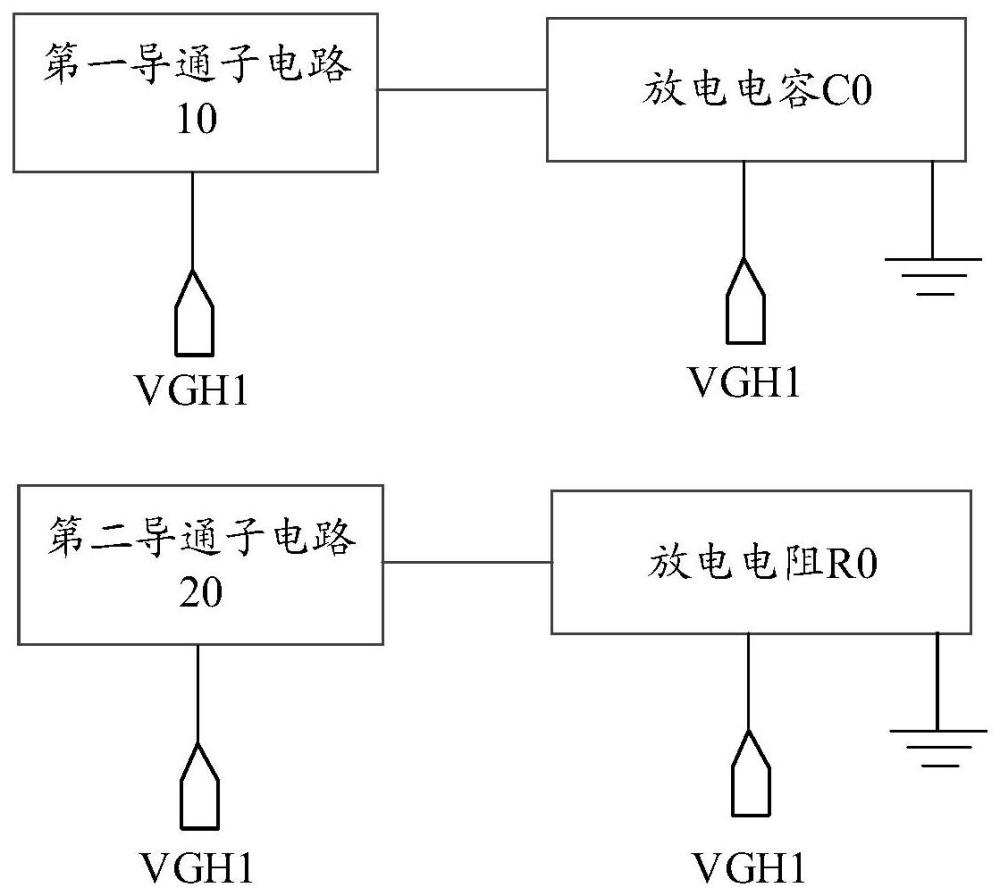

3、第一方面,本申请实施例提供了一种放电电路,包括:第一导通子电路、第二导通子电路、放电电容和放电电阻;

4、第一导通子电路与供电电压信号端和放电电容的第一端耦接,被配置为响应于供电电压信号端的电压大于或者等于电压阈值,将供电电压信号端与放电电容连通,使供电电压信号端上的电荷通过放电电容进行泄放,其中,放电电容的第二端接地;

5、第二导通子电路与供电电压信号端和放电电阻的第一端耦接,被配置为响应于供电电压信号端的电压小于电压阈值,将供电电压信号端与放电电阻连通,使供电电压信号端上的电荷通过放电电阻进行泄放,其中,放电电阻的第二端接地。

6、可选地,第一导通子电路包括:第一导通控制单元和第一晶体管;

7、第一导通控制单元与供电电压信号端和第一晶体管耦接,被配置为响应于供电电压信号端的电压大于或者等于电压阈值时,控制第一晶体管导通;

8、第一晶体管的控制端与第一导通控制单元耦接,第一晶体管的第一端与放电电容的第一端耦接,第一晶体管的第二端与供电电压信号端耦接。

9、可选地,第一导通控制单元还被配置为响应于供电电压信号端的电压大于或者等于电压阈值,对供电电压信号端上的电荷进行泄放。

10、可选地,第一晶体管为p型晶体管,第一导通控制单元包括:第二晶体管、第一电阻、第二电阻和第三电阻;

11、第二晶体管的控制端与供电电压信号端耦接,第二晶体管的第一端与第一电阻的第一端耦接,第二晶体管的第二端与第二电阻的第一端耦接;

12、第一电阻的第二端接地;

13、第二电阻的第二端与第三电阻的第一端耦接,第三电阻的第二端与供电电压信号端耦接。

14、可选地,第一晶体管为n型晶体管,第一导通控制单元包括:第二晶体管、第一电阻、第二电阻和第三电阻;

15、第二晶体管的控制端与供电电压信号端耦接,第二晶体管的第一端与第一电阻的第一端耦接,第二晶体管的第二端与第二电阻的第一端耦接;

16、第一电阻的第二端接地;

17、第二电阻的第二端与供电电压信号端耦接,第三电阻的第一端与第二电阻的第一端耦接,第三电阻的第二端与第一晶体管的第一端耦接。

18、可选地,放电电容包括多个放电子电容;

19、多个放电子电容的第一端与第一导通子电路耦接;

20、多个放电子电容的第二端接地。

21、可选地,第二导通子电路包括:第二导通控制单元和第三晶体管;

22、第二导通控制单元与供电电压信号端和第三晶体管耦接,被配置为响应于供电电压信号端的电压小于电压阈值,控制第三晶体管导通;

23、第三晶体管的控制端与第二导通控制单元耦接,第三晶体管的第一端与放电电阻的第一端耦接,第三晶体管的第二端与供电电压信号端耦接。

24、可选地,第二导通控制单元还被配置为响应于供电电压信号端的电压小于电压阈值,对供电电压信号端上的电荷进行泄放。

25、可选地,第三晶体管为p型晶体管,第二导通控制单元包括:第四晶体管、第四电阻、第五电阻和第六电阻;

26、第四晶体管的控制端与供电电压信号端耦接,第四晶体管的第一端与第四电阻的第一端耦接,第四晶体管的第二端与第五电阻的第一端耦接;

27、第四电阻的第二端接地;

28、第五电阻的第二端与第六电阻的第一端耦接,第六电阻的第二端与供电电压信号端耦接。

29、可选地,第三晶体管为n型晶体管,第二导通控制单元包括:第四晶体管、第四电阻、第五电阻和第六电阻;

30、第四晶体管的控制端与供电电压信号端耦接,第四晶体管的第一端与第四电阻的第一端耦接,第四晶体管的第二端与第五电阻的第一端耦接;

31、第四电阻的第二端接地;

32、第五电阻的第二端与供电电压信号端耦接,第六电阻的第一端与第五电阻的第一端耦接,第六电阻的第二端与第三晶体管的第二端耦接。

33、第二方面,本申请实施例还提供了一种电源控制电路,包括:电源管理电路和上述任一项的放电电路;

34、电源管理电路与放电电路的供电电压信号端耦接,被配置为向供电电压信号端输出电压。

35、第三方面,本申请实施例还提供了一种上述任一项的放电电路的放电控制方法,包括:

36、第一导通子电路响应于供电电压信号端的电压大于或者等于电压阈值,将供电电压信号端与放电电容连通,使供电电压信号端上的电荷通过放电电容进行泄放,其中,放电电容的第二端接地;

37、第二导通子电路响应于供电电压信号端的电压小于电压阈值,将供电电压信号端与放电电阻连通,使供电电压信号端上的电荷通过放电电阻进行泄放,其中,放电电阻的第二端接地。

38、本申请有益效果如下:

39、综上所述,本申请实施例中提供了一种放电电路、电源控制电路及放电控制方法,该放电电路包括:第一导通子电路、第二导通子电路、放电电容和放电电阻,第一导通子电路与供电电压信号端和放电电容的第一端耦接,被配置为响应于供电电压信号端的电压大于或者等于电压阈值,将供电电压信号端与放电电容连通,使供电电压信号端上的电荷通过放电电容进行泄放,放电电容的第二端接地,第二导通子电路与供电电压信号端和放电电阻的第一端耦接,被配置为响应于供电电压信号端的电压小于电压阈值,将供电电压信号端与放电电阻连通,使供电电压信号端上的电荷通过放电电阻进行泄放,放电电阻的第二端接地,上述采用放电电容和放电电阻对供电电压信号端进行分阶段放电的方案,能够对供电电压信号端的电荷进行充分释放,减少了电荷释放不充分导致的产品不良,提升了产品的可靠性。

40、本申请的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本申请而了解。本申请的目的和其他优点可通过在所写的说明书、权利要求书、以及附图中所特别指出的结构来实现和获得。

技术特征:

1.一种放电电路,其特征在于,包括:第一导通子电路、第二导通子电路、放电电容和放电电阻;

2.如权利要求1所述的放电电路,其特征在于,所述第一导通子电路包括:第一导通控制单元和第一晶体管;

3.如权利要求2所述的放电电路,其特征在于,所述第一导通控制单元还被配置为响应于所述供电电压信号端的电压大于或者等于电压阈值,对所述供电电压信号端上的电荷进行泄放。

4.如权利要求2所述的放电电路,其特征在于,所述第一晶体管为p型晶体管,所述第一导通控制单元包括:第二晶体管、第一电阻、第二电阻和第三电阻;

5.如权利要求2所述的放电电路,其特征在于,所述第一晶体管为n型晶体管,所述第一导通控制单元包括:第二晶体管、第一电阻、第二电阻和第三电阻;

6.如权利要求1~5任一项所述的放电电路,其特征在于,所述放电电容包括多个放电子电容;

7.如权利要求1~5任一项所述的放电电路,其特征在于,所述第二导通子电路包括:第二导通控制单元和第三晶体管;

8.如权利要求7所述的放电电路,其特征在于,所述第二导通控制单元还被配置为响应于所述供电电压信号端的电压小于电压阈值,对所述供电电压信号端上的电荷进行泄放。

9.如权利要求7所述的放电电路,其特征在于,所述第三晶体管为p型晶体管,所述第二导通控制单元包括:第四晶体管、第四电阻、第五电阻和第六电阻;

10.如权利要求7所述的放电电路,其特征在于,所述第三晶体管为n型晶体管,所述第二导通控制单元包括:第四晶体管、第四电阻、第五电阻和第六电阻;

11.一种电源控制电路,其特征在于,包括:电源管理电路和如权利要求1~10任一项所述的放电电路;

12.一种如权利要求1-10任一项所述的放电电路的放电控制方法,其特征在于,包括:

技术总结

本申请涉及显示技术领域,公开了一种放电电路、电源控制电路及放电控制方法,放电电路包括:第一导通子电路与供电电压信号端和放电电容的第一端耦接,被配置为响应于供电电压信号端的电压大于或者等于电压阈值,将供电电压信号端与放电电容连通,使供电电压信号端上的电荷通过放电电容进行泄放,放电电容的第二端接地,第二导通子电路与供电电压信号端和放电电阻的第一端耦接,被配置为响应于供电电压信号端的电压小于电压阈值,将供电电压信号端与放电电阻连通,使供电电压信号端上的电荷通过放电电阻进行泄放,放电电阻的第二端接地,上述用放电电容和放电电阻对供电电压信号端进行分阶段放电的方案,能对供电电压信号端的电荷进行充分释放。

技术研发人员:包玉峰,郑黎明,张一凡,何恒索,孙筱烨,马川

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!