一种静电防护电路、SOC芯片及电子设备的制作方法

本技术涉及电子电路的,具体而言,涉及一种静电防护电路、soc芯片及电子设备。

背景技术:

1、esd(electrostatic discharge,静电释放)事件会出现在芯片制造、封装、测试、运输等过程中。随着晶体管尺寸减小,芯片的规模越来越大,会导致esd的可靠性降低。因此,不影响系统正常工作,并且可靠的esd防护电路变得越来越重要。

2、目前,通常通过hbm(human body model,人体模型)电路、cdm(charged devicemodel,充电器件模型)电路等作为esd防护电路(静电防护电路),用于阻滞由总线输入到连接于总线上的设备的esd电流。但是,在总线多设备(多个设备与总线连接)通信,且总线有电的情况下,现有的esd防护电路会导致总线与掉电设备之间存在漏电通路,影响与总线连接的其他设备之间的正常通信。

技术实现思路

1、本技术提供一种静电防护电路、soc芯片及电子设备,以解决现有技术中在总线多设备(多个设备与总线连接)通信,且总线有电的情况下,esd防护电路会导致总线与掉电设备之间存在漏电通路,影响与总线连接的其他设备之间的正常通信的问题。

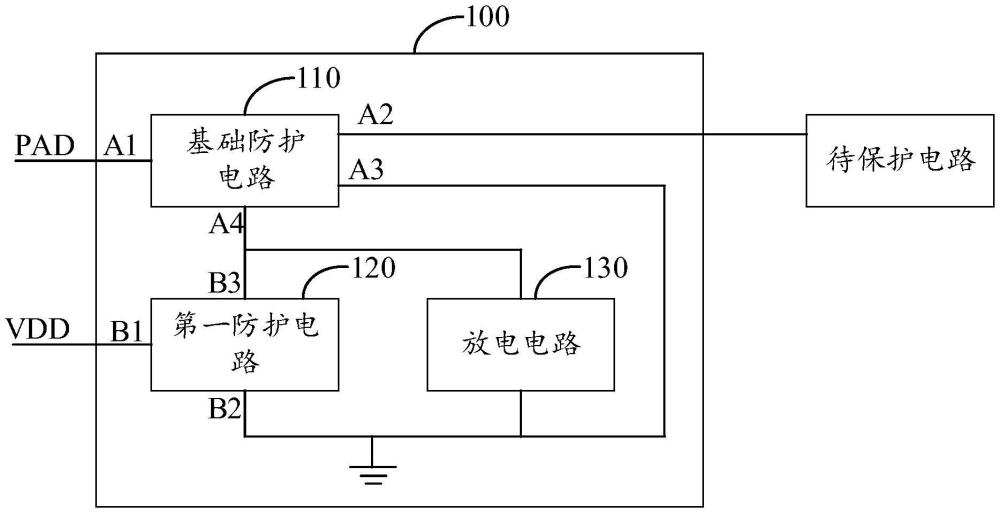

2、第一方面,本技术提供一种静电防护电路,包括:基础防护电路、第一防护电路、放电电路,所述基础防护电路的第一端被配置为与总线连接,所述基础防护电路的第二端被配置为与待保护电路连接,所述基础防护电路的第三端接地,所述基础防护电路用于阻滞由所述总线输入到所述待保护电路的esd电流;所述第一防护电路的第一端被配置为连接外部电源,所述第一防护电路的第二端接地,所述第一防护电路的第三端与所述基础防护电路的第四端连接;所述第一防护电路的第三端还通过所述放电电路接地;所述基础防护电路、所述第一防护电路和所述放电电路配合,用于将所述第一防护电路的第三端充电至与所述外部电源相同的电压。

3、本技术实施例中,由于第一防护电路的第三端充电至与外部电源相同的电压,因此,即使总线多设备通信,且总线有电的情况下,由于第一防护电路的第三端充电至与外部电源相同的电压,使得第一防护电路的第三端与总线之间不存在电势差,因此,总线与掉电设备之间不会出现漏电通路,也就不会影响与总线连接的其他设备之间的正常通信。

4、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述静电防护电路还被配置为:利用所述基础防护电路、所述第一防护电路和所述放电电路中的至少两个配合来释放因esd现象产生的esd电流。

5、本技术实施例中,通过基础防护电路、第一防护电路和放电电路进行配合,可以提高释放esd电流的能力,且使得该静电防护电路能针对多种位置发生的esd现象进行防护,使得本方案提供的静电防护电路可以应用于更多的场景中。

6、结合上述第一方面提供的技术方案,在一些可能的实施方式中,在所述基础防护电路的第一端发生esd现象产生第一esd电流的情况下,所述基础防护电路被配置为将所述第一esd电流从所述基础防护电路与所述总线连接的一端流向所述基础防护电路的第四端;所述放电电路被配置为将所述第一esd电流从所述基础防护电路的第四端流向所述放电电路的接地端。

7、本技术实施例中,在基础防护电路的第一端发生esd现象的情况下,通过基础防护电路和放电电路配合,即可使第一esd电流流向接地端,完成对第一esd电流的释放。

8、结合上述第一方面提供的技术方案,在一些可能的实施方式中,若所述放电电路的接地端空接,所述第一防护电路,还被配置为将所述第一esd电流从所述接地端流向所述第一防护电路的第一端。

9、本技术实施例中,当放电电路的接地端空接时,由于第一esd电流无法从接地端释放,因此,第一防护电路将将第一esd电流流向第一防护电路的第一端,以使第一esd电流流出静电防护电路,完成对第一esd电流的释放。

10、结合上述第一方面提供的技术方案,在一些可能的实施方式中,在所述第一防护电路的第一端发生esd现象产生第二esd电流的情况下,所述第一防护电路被配置为将所述第二esd电流从所述第一防护电路的第一端流向所述第一防护电路的第三端;所述放电电路被配置为将所述第二esd电流从所述基础防护电路的第四端流向所述放电电路的接地端。

11、本技术实施例中,在第一防护电路的第一端发生esd现象的情况下,通过第一防护电路和放电电路配合,即可使第二esd电流流向接地端,完成对第二esd电流的释放。

12、结合上述第一方面提供的技术方案,在一些可能的实施方式中,若所述放电电路的接地端空接,所述基础防护电路,被配置为将所述第二esd电流从所述接地端流向所述基础防护电路的第一端。

13、本技术实施例中,当放电电路的接地端空接时,由于第二esd电流无法从接地端释放,因此,基础防护电路将将第二esd电流流向基础防护电路的第一端,以使第二esd电流流出静电防护电路,完成对第二esd电流的释放。

14、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述第一防护电路,包括:第一晶体管、第二晶体管,所述第一晶体管的第一端被配置为与所述外部电源连接,所述第一晶体管的第二端与所述基础防护电路的第四端连接,所述第一晶体管的第二端还通过所述放电电路接地;所述第二晶体管的第一端与所述第一晶体管的第一端连接,所述第二晶体管的第二端接地。

15、本技术实施例中,通过第一晶体管和第二晶体管即可实现第一防护电路,降低了防护电路的电路复杂度。

16、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述放电电路,包括:放电晶体管,所述第一防护电路的第三端通过所述放电晶体管接地,所述放电晶体管的使能端被配置为接收控制信号,所述控制信号用于控制所述放电晶体管的导通或关断,且在发生esd现象的情况下,控制所述放电晶体管导通。

17、本技术实施例中,放电电路包括放电晶体管,从而可以实现在发生esd现象的情况下,放电晶体管导通,以便于通过该放电晶体管将esd电流导向接地端。

18、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述放电电路,还包括:电源检测电路,所述电源检测电路的第一端与所述第一防护电路的第三端连接,所述电源检测电路的第二端接地,所述电源检测电路的第三端与所述放电晶体管的使能端连接,所述电源检测电路用于生成所述控制信号。

19、本技术实施例中,由于放电电路还包括电源检测电路,进而可以通过该电源检测电路识别是否出现esd现象,从而可以通过电源检测电路控制放电晶体管的导通状态。

20、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述电源检测电路,包括:电阻电容电路、反向电路,所述电阻电容电路的第一端与所述第一防护电路的第三端连接,所述电阻电容电路的第二端接地,所述电阻电容电路被配置为响应所述第一防护电路的第三端输出的电压的变化,调整所述电阻电容电路第三端的输出电压;所述电阻电容电路的第三端通过所述反向电路与所述放电晶体管的使能端连接,所述反向电路被配置为将所述电阻电容电路第三端的输出电压反向,得到所述控制信号。

21、本技术实施例中,通过电阻电容电路可以检测到第一防护电路的第三端的电压变化,从而可以识别是否出现esd现象时。进而在出现esd现象(第一防护电路的第三端出现大于外接电源的电压)时,通过反向电路控制放电晶体管导通。通过电阻电容电路、反向电路即可实现电源检测电路的功能,降低了电路复杂度。

22、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述电阻电容电路包括:第一电阻、第一电容;在所述放电晶体管为pmos管的情况下,所述第一电容的第一端与所述第一防护电路的第三端连接,所述第一电容的第二端通过所述第一电阻接地,所述第一电容的第二端还通过所述反向电路与所述放电晶体管的使能端连接;在所述放电晶体管为nmos管的情况下,所述第一电阻的第一端与所述第一防护电路的第三端连接,所述第一电阻的第二端通过所述第一电容接地,所述第一电阻的第二端还通过所述反向电路与所述放电晶体管的使能端连接。

23、本技术实施例中,由于pmos管和nmos管的导通条件不同,因此,电阻电容电路需要根据放电晶体管的导通类型选择不同的连接方式。

24、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述放电晶体管为pmos管,所述反向电路,包括:第一pmos管、第一nmos管,所述第一pmos管的源极与所述第一防护电路的第三端连接,所述第一pmos管的栅极与所述电阻电容电路的第三端连接;所述第一nmos管的漏极分别与所述第一pmos管的漏极和所述放电晶体管的栅极连接,所述第一nmos管的源极接地,所述第一nmos管的栅极与所述电阻电容电路的第三端连接。

25、结合上述第一方面提供的技术方案,在一些可能的实施方式中,若所述放电晶体管为nmos管,所述反向电路,包括:第二pmos管、第二电阻,所述第二pmos管的源极与所述第一防护电路的第三端连接,所述第二pmos管的栅极与所述电阻电容电路的第三端连接,所述第二pmos管的漏极与所述放电晶体管的栅极连接;所述第二pmos管的漏极通过所述第二电阻接地。

26、结合上述第一方面提供的技术方案,在一些可能的实施方式中,所述基础防护电路包括:第二防护电路、充电接触防护电路,所述第二防护电路的第一端被配置为与总线连接,所述第二防护电路的第二端接地,所述第二防护电路的第三端与所述第一防护电路的第三端连接;所述充电接触防护电路的第一端被配置为与所述总线连接,所述充电接触防护电路的第二端接地,所述充电接触防护电路的第三端被配置为与待保护电路连接,所述充电接触防护电路的第四端与所述第一防护电路的第三端连接。

27、第二方面,本技术提供一种soc(system on chip,系统级芯片)芯片,包括:总线、多个待保护电路和如上述第一方面和/或结合上述第一方面任一可能的实施方式提供的静电防护电路,每个所述待保护电路均通过一个所述静电防护电路与所述总线连接。

28、第三方面,本技术提供一种电子设备,包括:如上述第二方面提供的soc芯片。

- 还没有人留言评论。精彩留言会获得点赞!