一种双电源供电电路和功率传输协议芯片的制作方法

本发明实施方式涉及电子,特别是涉及一种双电源供电电路和功率传输协议芯片。

背景技术:

1、随着usb pd快充技术的普及,pd快充协议芯片的功能需求越来越高。pd快充协议芯片是一种用于支持快速充电的芯片,它可以实现高效的电源管理和数据传输。pd快充协议芯片定义了一种标准的通信协议,使得充电器和充电设备之间可以进行快速、安全、可靠的通信,从而实现快速充电。

2、但是pd快充协议芯片正常工作时自身也需要电源,通常pd快充协议芯片的取电可以来自于总线电压vbus或者电池供电vin,总线电压vbus供电最大可以到20v,电池供电vin最大到5.5v,在两者都有电的情况下,通常总线电压vin的优先级更高。此外,在总线电压vbus和电池供电vin其中一个掉电时,还有可能出现另一个电源的电流倒灌至掉电电源中,导致电源损坏。

技术实现思路

1、本发明实施方式主要解决的技术问题是提供一种双电源供电电路和功率传输协议芯片,能够实现当同时有外部电压源和接口电压源供电时,接口电压源优先供电;外部电压源有电,接口电压源没电时,选择外部电压源供电;外部电压源没电,接口电压源有电时,选择接口电压源供电;并且防止在仅有一个电压源供电时该电压倒灌至另一电压源。

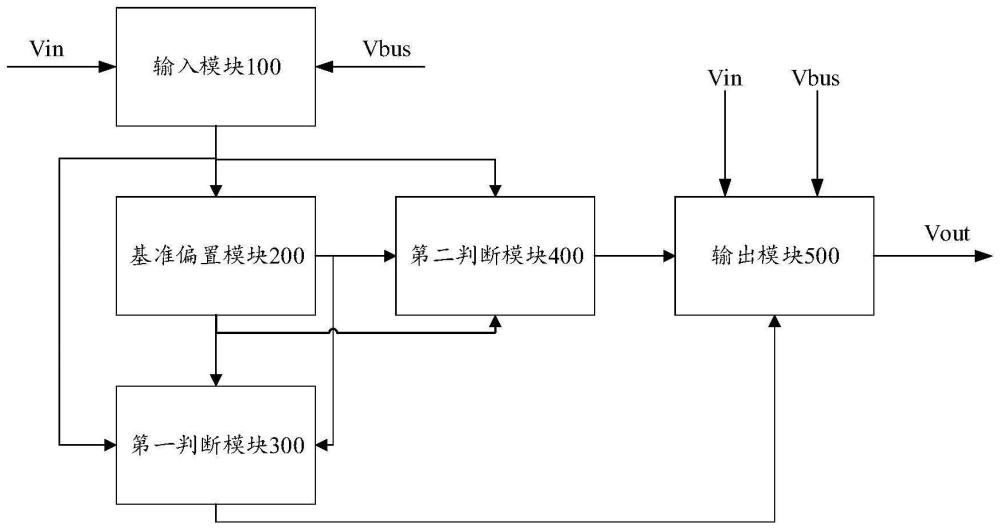

2、为解决上述技术问题,本发明实施方式采用的一个技术方案是:提供一种双电源供电电路,包括:被配置为响应于外部电压或接口电压输出第一电压的输入模块;被配置为响应于所述第一电压输出基准电压和偏置电流的基准偏置模块;被配置为响应于所述外部电压、所述第一电压、所述基准电压和所述偏置电流输出第一判断信号的第一判断模块;被配置为响应于所述接口电压、所述第一电压、所述基准电压和所述偏置电流输出第二判断信号的第二判断模块;被配置为响应于所述第一判断信号将所述外部电压转换为充电电压,或响应于所述第二判断信号将所述接口电压转换为所述充电电压的输出模块,当同时接收到所述第一判断信号和所述第二判断信号时,所述输出模块仅将所述外部电压转换为所述充电电压。

3、在一些实施例中,所述输入模块包括:被配置为响应于所述外部电压输出所述第一电压的第一输入模块;被配置为响应于所述接口电压输出所述第一电压的第二输入模块。

4、在一些实施例中,所述第一输入模块包括第一晶体管、第二晶体管和第一偏置单元,所述第一晶体管的漏极引入所述外部电压,所述第一晶体管的源极连接所述第二晶体管的源极,所述第二晶体管的漏极连接所述基准偏置模块的输入端;所述第一偏置单元响应于所述外部电压输出第一偏置电压至所述第一晶体管的栅极和所述第二晶体管的栅极,以导通所述第一晶体管和所述第二晶体管。

5、在一些实施例中,所述第二输入模块包括第三晶体管、第四晶体管和第二偏置单元,所述第三晶体管的漏极引入所述接口电压,所述第三晶体管的源极连接所述第四晶体管的源极,所述第四晶体管的漏极连接所述基准偏置模块的输入端;所述第二偏置单元响应于所述接口电压输出第二偏置电压至所述第三晶体管的栅极和所述第四晶体管的栅极,以导通所述第三晶体管和所述第四晶体管。

6、在一些实施例中,所述第一偏置单元包括第一电阻、第二电阻、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管、第十晶体管、第十一晶体管、第十二晶体管、第十三晶体管和第十四晶体管,所述第五晶体管的源极引入所述外部电压,所述第六晶体管的源极和所述第二电阻的第一端连接所述第五晶体管的源极,所述第五晶体管的栅极连接所述第六晶体管的栅极、所述第五晶体管的漏极和所述第七晶体管的源极,所述第六晶体管的漏极连接所述第八晶体管的源极;所述第七晶体管的栅极连接所述第七晶体管的漏极和所述第十晶体管的漏极,所述第十晶体管的栅极连接所述第二电阻的第二端和所述第九晶体管的漏极,所述第十晶体管的源极连接所述第九晶体管的栅极和所述第一电阻的第一端,所述第九晶体管的源极和所述第一电阻的第二端接地;所述第八晶体管的漏极连接所述第一晶体管的栅极、所述第二晶体管的栅极和所述第十一晶体管的漏极和所述第十一晶体管的栅极,所述第十一晶体管的源极连接所述第十二晶体管的漏极和所述第十二晶体管的栅极,所述第十二晶体管的源极连接所述第十三晶体管的漏极和所述第十三晶体管的栅极,所述第十三晶体管的源极连接所述第十四晶体管的漏极和所述第十四晶体管的栅极,所述第十四晶体管的源极接地。

7、在一些实施例中,所述第二偏置单元包括第三电阻、第四电阻、第十五晶体管、第十六晶体管、第十七晶体管、第十八晶体管、第十九晶体管、第二十晶体管、第二十一晶体管、第二十二晶体管、第二十三晶体管和第二十四晶体管,所述第十五晶体管的源极引入所述接口电压,所述第十六晶体管的源极和所述第四电阻的第一端连接所述第十五晶体管的源极,所述第十五晶体管的栅极连接所述第十六晶体管的栅极、所述第十五晶体管的漏极和所述第十七晶体管的源极,所述第十六晶体管的漏极连接所述第十八晶体管的源极;所述第十七晶体管的栅极连接所述第十七晶体管的漏极和所述第二十晶体管的漏极,所述第二十晶体管的栅极连接所述第四电阻的第二端和所述第十九晶体管的漏极,所述第二十晶体管的源极连接所述第十九晶体管的栅极和所述第三电阻的第一端,所述第十九晶体管的源极和所述第三电阻的第二端接地;所述第十八晶体管的漏极连接所述第三晶体管的栅极、所述第四晶体管的栅极和所述第二十一晶体管的漏极和所述第二十一晶体管的栅极,所述第二十一晶体管的源极连接所述第二十二晶体管的漏极和所述第二十二晶体管的栅极,所述第二十二晶体管的源极连接所述第二十三晶体管的漏极和所述第二十三晶体管的栅极,所述第二十三晶体管的源极连接所述第二十四晶体管的漏极和所述第二十四晶体管的栅极,所述第二十四晶体管的源极接地。

8、在一些实施例中,所述基准偏置模块包括:被配置为响应于所述第一电压输出所述基准电压的基准单元;被配置为响应于所述基准电压和所述第一电压输出所述偏置电流的偏置单元。

9、在一些实施例中,所述基准单元包括第五电阻、第六电阻、第七电阻、第八电阻、第二十五晶体管、第二十六晶体管、第二十七晶体管、第二十八晶体管和第一运算放大器,所述第二十五晶体管的源极连接第二十六晶体管的源极和所述输入模块的输出端,所述第二十五晶体管的栅极连接第二十六晶体管的栅极、所述第二十五晶体管的漏极和所述第一运算放大器的输出端;所述第二十六晶体管的漏极连接所述第八电阻的第一端,以输出所述基准电压,所述第八电阻的第二端连接所述第六电阻的第一端和所述第七电阻的第一端,所述第六电阻的第二端连接所述第一运算放大器的反相输入端和所述二十七晶体管的发射极;所述第七电阻的第二端连接所述第五电阻的第一端和所述第一运算放大器的同相输入端,所述第五电阻的第二端连接所述第二十八晶体管的发射极,所述第二十七晶体管的基极、所述第二十七晶体管的集电极、所述第二十八晶体管的基极和所述第二十八晶体管的集电极接地。

10、在一些实施例中,所述偏置单元包括第九电阻、第二十九晶体管、第三十晶体管、第三十一晶体管和第二运算放大器,所述第二运算放大器的同相输入端连接所述基准单元的输出端,所述第二运算放大器的反相输入端连接所述第三十一晶体管的源极和所述第九电阻的第一端,所述第二运算放大器的电源输入端连接所述第二十九晶体管的源极、所述第三十晶体管的源极和所述输入模块的输出端;所述第二运算放大器的输出端连接所述第三十一晶体管的栅极,所述第二十九晶体管的栅极连接所述第三十晶体管的栅极、所述第二十九晶体管的漏极和所述第三十一晶体管的漏极,所述第三十晶体管的漏极输出所述偏置电流,所述第九电阻的第二端接地。

11、在一些实施例中,所述第一判断模块包括第一比较器、第十电阻和第十一电阻,所述第十电阻的第一端引入所述外部电压,所述第十电阻的第二端连接所述第十一电阻的第一端和所述第一比较器的同相输入端,所述第十电阻的第二端接地;所述第一比较器的反相输入端连接所述基准偏置模块的基准电压输出端,所述第一比较器的偏置电流端连接所述基准偏置模块的偏置电流输出端,所述第一比较器的电源输入端连接所述输入模块的输出端,所述第一比较器的输出端输出所述第一判断信号。

12、在一些实施例中,所述第二判断模块包括第二比较器、第十二电阻和第十三电阻,所述第十二电阻的第一端引入所述接口电压,所述第十二电阻的第二端连接所述第十三电阻的第一端和所述第二比较器的同相输入端,所述第十三电阻的第二端接地;所述第二比较器的反相输入端连接所述基准偏置模块的基准电压输出端,所述第二比较器的偏置电流端连接所述基准偏置模块的偏置电流输出端,所述第二比较器的电源输入端连接所述输入模块的输出端,所述第二比较器的输出端输出所述第二判断信号。

13、在一些实施例中,所述输出模块包括:被配置为响应于所述第一判断信号、所述基准电压和所述偏置电流将所述外部电压转换为第一输出电压的第一稳压单元;被配置为响应于所述第一判断信号和所述第二判断信号输出使能信号的信号输出单元,当且仅当只存在第二判断信号时,所述信号输出单元输出所述使能信号;被配置为响应于所述使能信号、所述基准电压和所述偏置电流将所述接口电压转换为第二输出电压的第二稳压单元;被配置为响应于所述第一输出电压或所述第二输出电压输出充电电压的输出单元。

14、在一些实施例中,所述第一稳压单元包括第三十二晶体管、第十四电阻、第十五电阻和第三运算放大器,所述第三十二晶体管的源极引入所述外部电压,所述第三十二晶体管的栅极连接所述第三运算放大器的输出端,所述第三十二晶体管的漏极连接第十四电阻的第一端,并输出所述第一输出电压;所述第三运算放大器的同相输入端连接所述基准偏置模块的基准电压输出端,所述第三运算放大器的偏置电流端连接所述基准偏置模块的偏置电流输出端,所述第三运算放大器的反相输入端连接所述第十四电阻的第二端和所述第十五电阻的第一端,所述第十五电阻的第二端接地。

15、在一些实施例中,所述信号输出单元包括反相器和乘法器,所述反相器的输入端连接所述第一判断模块的输出端,所述反相器的输出端连接所述乘法器的第一输入端,所述乘法器的第二输入端连接所述第二判断模块的输出端,所述乘法器的输出端输出所述使能信号。

16、在一些实施例中,所述第二稳压单元包括第三十三晶体管、第十六电阻、第十七电阻和第四运算放大器,所述第三十三晶体管的源极引入所述接口电压,所述第三十三晶体管的栅极连接所述第四运算放大器的输出端,所述第三十三晶体管的漏极连接所述第十六电阻的第一端,并输出所述第二输出电压;所述第四运算放大器的同相输入端连接所述基准偏置模块的基准电压输出端,所述第四运算放大器的偏置电流端连接所述基准偏置模块的偏置电流输出端,所述第四运算放大器的反相输入端连接所述第十六电阻的第二端和所述第十七电阻的第一端,所述第十七电阻的第二端接地。

17、在一些实施例中,所述输出单元包括第三十四晶体管、第三十五晶体管和输出电容,所述第三十四晶体管的漏极连接所述第一稳压单元的输出端和所述第三十五晶体管的栅极,所述第三十五晶体管的漏极连接所述第二稳压单元的输出端和所述第三十四晶体管的栅极,所述第三十四晶体管的源极连接所述第三十五晶体管的源极和所述输出电容的第一端,并输出所述充电电压,所述输出电容的第二端接地。

18、为解决上述技术问题,本发明实施方式采用的另一个技术方案是:提供一种功率传输协议芯片,包括:如上所述的双电源供电电路。

19、本发明实施方式的有益效果是:区别于现有技术的情况,本发明实施方式能够实现在同时有外部电压源和接口电压源供电时,优先选择外部电压源供电;外部电压源有电,接口电压源没电时,选择外部电压源供电;外部电压源没电,接口电压源有电时,选择接口电压源供电;并且在仅有一个电压源供电时防止该电压倒灌至另一电压源。

- 还没有人留言评论。精彩留言会获得点赞!