LDPC码字的编码方法、编码系统及存储介质

ldpc码字的编码方法、编码系统及存储介质

技术领域

1.本发明涉及通信编码技术领域,具体地,涉及ldpc码字的编码方法、编码系统及存储介质。

背景技术:

2.自从shannon在其1948年发表的论文中提出了香农信道编码定理之后,众多信道编码领域的学者们一心极力寻找、设计合适的纠错码,以期望可以达到shannon 极限的性能。于是在1963年,gallager第一次提出了低密度奇偶校验码(low dens ity parity check,ldpc),并且将其基于迭代原理的译码方法推演出来,同时证明了这种译码方法的时间复杂度随码长线性增长。但由于当时集成电路技术的短板,加之未经优化的迭代译码算法复杂度仍然较高,人们并没有把ldpc码重视并应用起来,导致ldpc码被遗忘了接近30年。直到1993年,一个里程碑式的研究成果——turbo码的出现,引发了学者们对同样基于迭代原理译码的ldpc 码重新考量。mackay和spielman随后于90年代中期分别发现了基于随机图和扩展图构造具备稀疏特性ldpc码的方法,由这些方法构造出的ldpc码字具备瀑布区逼近香农限的优秀性能。luby和mackay等学者又论证了ldpc码译码复杂度随码长线性增长和逼近香农限的特性。关于ldpc码研究成果的不断涌现,加之集成电路技术的长足发展,使得工业界和理论界对ldpc码的研究兴趣再次达到高潮。

3.传统的ldpc编码不受任何结构约束,对度分布设计的较大自由度使得这种编码方法更容易获得性能较好的码字,但是它的致命缺点就是编码复杂度极高,不适合实际应用。qc、qc-ira、qc-ira-raptor等结构化的码字降低了随机码字在编码乃至译码方面的复杂度,从而被广泛应用于实际系统中:5g;ieee802.11n无线局域网标准;ieee802.11e无线广域网标准;欧洲第二代数字广播电视传输标准dvb2 系列;北美ccsds的近地、深空通信系统;中国数字电视地面传输标准(dttb)等等。

技术实现要素:

4.针对现有技术中的缺陷,本发明的目的是提供一种ldpc码字的编码方法、编码系统及存储介质。

5.根据本发明提供的一种ldpc码字的编码方法,包括以下步骤:

6.校验位初始化步骤:初始化校验位,所述校验位包括:内校验位和外校验位;

7.信息位累加步骤:根据编码码表将信息位累加到内、外校验位上;

8.内校验位更新步骤:对内校验位进行自增,得到新的内校验位;

9.外校验位更新步骤:根据编码码表将内校验位累加到外校验位上,得到新的外校验位。

10.优选地,其特征在于,

11.所述ldpc码字的校验矩阵h为m行n列,n=k+m,n表示ldpc码字的码长, m表示校验位长度,k表示ldpc码字的信息位长度,m=m1+m2,m1表示内校验位长度,m2表示外校验位长

度;

12.m行按照m1和m2的长度,n列按照k、m1和m2的长度,将校验矩阵h划分为 2行3列的六个子矩阵,子矩阵均由大小为q

×

q的循环子块组成,所述循环子块为全零矩阵、单位矩阵或者单位矩阵向右循环偏移得到的准循环子块,其中,组成第1行第2 个子矩阵的循环子块均为单位矩阵,第1行第3个子矩阵为全零矩阵,第2行第3个子矩阵为单位矩阵。

13.优选地,所述校验位初始化步骤:

14.对码率为k/n的ldpc码字的校验位(p0,p1,

…

,p

m-1

)进行初始化,即令 p0=p1=p2=

…

=p

m-1

=0,其中为内校验位,为外校验位。

15.优选地,所述信息位累加步骤:

16.设信息位为(s0,s1,

…

,s

k-1

),对于任意整数k,0≤k<k,令将信息位s

k

累加到校验位p

q(i,j,l)

上,即:使p

q(i,j,l)

的值变为p

q(i,j,l)

+s

k

,j=0,1,

…

,w(i)-1,其中w(i)为码表第i+1行的元素个数,l=0,1,

…

,q-1,q(i,j,l)的值如下计算可得:

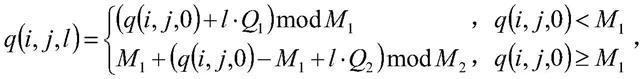

17.q(i,j,0)为ldpc码字的码表中第i+1行第j+1列元素,则对任意整数l,0<l<q,其中

18.优选地,所述内校验位更新步骤:

19.p0不变,对于所有整数n,0<n<m1,依次令p

n

自增p

n-1

;

20.所述外校验位更新步骤:

21.对于任意整数k,0≤k<m1,令将p

k

累加到p

q(i,j,l)

上,即:

22.p

q(i,j,l)

=p

q(i,j,l)

+p

k

,j=0,1,

…

,w(i)-1

23.根据本发明提供的一种ldpc码字的编码系统,包括以下模块:

24.校验位初始化模块:初始化校验位,所述校验位包括:内校验位和外校验位;

25.信息位累加模块:根据编码码表将信息位累加到内、外校验位上;

26.内校验位更新模块:对内校验位进行自增,得到新的内校验位;

27.外校验位更新模块:根据编码码表将内校验位累加到外校验位上,得到新的外校验位。

28.优选地,其特征在于,

29.所述ldpc码字的校验矩阵h为m行n列,n=k+m,n表示ldpc码字的码长, m表示校验位长度,k表示ldpc码字的信息位长度,m=m1+m2,m1表示内校验位长度,m2表示外校验位长度;

30.m行按照m1和m2的长度,n列按照k、m1和m2的长度,将校验矩阵h划分为 2行3列的六个子矩阵,子矩阵均由大小为q

×

q的循环子块组成,所述循环子块为全零矩阵、单位矩阵或者单位矩阵向右循环偏移得到的准循环子块,其中,组成第1行第2 个子矩阵的循环子块均为单位矩阵,第1行第3个子矩阵为全零矩阵,第2行第3个子矩阵为单位矩阵。

31.优选地,所述校验位初始化模块:

32.对码率为k/n的ldpc码字的校验位(p0,p1,

…

,p

m-1

)进行初始化,即令 p0=p1=p2=

…

=p

m-1

=0,其中为内校验位,为外校验位。

33.优选地,所述信息位累加模块:

34.设信息位为(s0,s1,

…

,s

k-1

),对于任意整数k,0≤k<k,令将信息位s

k

累加到校验位p

q(i,j,l)

上,即:使p

q(i,j,l)

的值变为p

q(i,j,l)

+s

k

,j=0,1,

…

,w(i)-1,其中w(i)为码表第i+1行的元素个数,l=0,1,

…

,q-1,q(i,j,l)的值如下计算可得:

35.q(i,j,0)为ldpc码字的码表中第i+1行第j+1列元素,则对任意整数l,0<l<q,其中

36.所述内校验位更新模块:

37.p0不变,对于所有整数n,0<n<m1,依次令p

n

自增p

n-1

;

38.所述外校验位更新模块:

39.对于任意整数k,0≤k<m1,令将p

k

累加到p

q(i,j,l)

上,即:

40.p

q(i,j,l)

=p

q(i,j,l)

+p

k

,j=0,1,

…

,w(i)-1

41.根据本发明提供的一种存储有计算机程序的计算机可读存储介质,其特征在于,所述计算机程序被处理器执行时实现上述中任一项所述的ldpc码字的编码方法的步骤。

42.与现有技术相比,本发明具有如下的有益效果:

43.本发明提供的ldpc码字的编码方法、编码系统,采用将校验位分为内、外校验位并分别进行编码的方法,相比现有技术,产生了意料不到的ldpc码字性能上的提升;ldpc码字的校验矩阵h为qc-ira-raptor-like结构,并且为该ldpc码字在某个特定码率下设计了编码码表。与现有技术相比,该编码方法具有编码简便,性能良好的特点。

具体实施方式

44.下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。

45.根据本发明提供的一种ldpc码字的编码方法,包括以下步骤:

46.校验位初始化步骤:初始化校验位,所述校验位包括:内校验位和外校验位;

47.信息位累加步骤:根据编码码表将信息位累加到内、外校验位上;

48.内校验位更新步骤:对内校验位进行自增,得到新的内校验位;

49.外校验位更新步骤:根据编码码表将内校验位累加到外校验位上,得到新的外校验位。

50.具体地,其特征在于:

51.所述ldpc码字的校验矩阵h为m行n列,n=k+m,n表示ldpc码字的码长, m表示校验

位长度,k表示ldpc码字的信息位长度,m=m1+m2,m1表示内校验位长度,m2表示外校验位长度;

52.m行按照m1和m2的长度,n列按照k、m1和m2的长度,将校验矩阵h划分为 2行3列的六个子矩阵,子矩阵均由大小为q

×

q的循环子块组成,所述循环子块为全零矩阵、单位矩阵或者单位矩阵向右循环偏移得到的准循环子块,其中,组成第1行第2 个子矩阵的循环子块均为单位矩阵,第1行第3个子矩阵为全零矩阵,第2行第3个子矩阵为单位矩阵。

53.具体地,所述校验位初始化步骤:

54.对码率为k/n的ldpc码字的校验位(p0,p1,

…

,p

m-1

)进行初始化,即令 p0=p1=p2=

…

=p

m-1

=0,其中为内校验位,为外校验位。

55.具体地,所述信息位累加步骤:

56.设信息位为(s0,s1,

…

,s

k-1

),对于任意整数k,0≤k<k,令将信息位s

k

累加到校验位p

q(i,j,l)

上,即:使p

q(i,j,l)

的值变为p

q(i,j,l)

+s

k

,j=0,1,

…

,w(i)-1,其中w(i)为码表第i+1行的元素个数,l=0,1,

…

,q-1,q(i,j,l)的值如下计算可得:

57.设q(i,j,0)为ldpc码字的码表中第i+1行第j+1列元素,则对任意整数l,0<l<q,其中

58.具体地,所述内校验位更新步骤:

59.p0不变,对于所有整数n,0<n<m1,依次令p

n

自增p

n-1

;

60.所述外校验位更新步骤:

61.对于任意整数k,0≤k<m1,令将p

k

累加到p

q(i,j,l)

上,即:

62.p

q(i,j,l)

=p

q(i,j,l)

+p

k

,j=0,1,

…

,w(i)-1

63.根据本发明提供的一种ldpc码字的编码系统,包括以下模块:

64.校验位初始化模块:初始化校验位,所述校验位包括:内校验位和外校验位;

65.信息位累加模块:根据编码码表将信息位累加到内、外校验位上;

66.内校验位更新模块:对内校验位进行自增,得到新的内校验位;

67.外校验位更新模块:根据编码码表将内校验位累加到外校验位上,得到新的外校验位。

68.具体地,其特征在于,

69.所述ldpc码字的校验矩阵h为m行n列,n=k+m,n表示ldpc码字的码长, m表示校验位长度,k表示ldpc码字的信息位长度,m=m1+m2,m1表示内校验位长度,m2表示外校验位长度;

70.m行按照m1和m2的长度,n列按照k、m1和m2的长度,将校验矩阵h划分为 2行3列的六个子矩阵,子矩阵均由大小为q

×

q的循环子块组成,所述循环子块为全零矩阵、单位矩阵或者单位矩阵向右循环偏移得到的准循环子块,其中,组成第1行第2 个子矩阵的循环子块均为单位矩阵,第1行第3个子矩阵为全零矩阵,第2行第3个子矩阵为单位矩阵。

71.具体地,所述校验位初始化模块:

72.对码率为k/n的ldpc码字的校验位(p0,p1,

…

,p

m-1

)进行初始化,即令 p0=p1=p2=

…

=p

m-1

=0,其中为内校验位,为外校验位。

73.具体地,所述信息位累加模块:

74.设信息位为(s0,s1,

…

,s

k-1

),对于任意整数k,0≤k<k,令将信息位s

k

累加到校验位p

q(i,j,l)

上,即:使p

q(i,j,l)

的值变为p

q(i,j,l)

+s

k

,j=0,1,

…

,w(i)-1,其中w(i)为码表第i+1行的元素个数,l=0,1,

…

,q-1,q(i,j,l)的值如下计算可得:

75.q(i,j,0)为ldpc码字的码表中第i+1行第j+1列元素,则对任意整数l,0<l<q,其中

76.所述内校验位更新模块:

77.p0不变,对于所有整数n,0<n<m1,依次令p

n

自增p

n-1

;

78.所述外校验位更新模块:

79.对于任意整数k,0≤k<m1,令将p

k

累加到p

q(i,j,l)

上,即:

80.p

q(i,j,l)

=p

q(i,j,l)

+p

k

,j=0,1,

…

,w(i)-1

81.根据本发明提供的一种存储有计算机程序的计算机可读存储介质,所述计算机程序被处理器执行时实现上述中任一项所述的ldpc码字的编码方法的步骤。

82.下面通过优选例,对本发明进行更为具体地说明。

83.优选例1:

84.下面结合实施例进一步说明本发明的技术方案。

85.本发明提供了一种ldpc码的编码方法,以及对应的编码码表,并对相应的码字结构和编码方法进行详细说明。

86.一种ldpc码字的编码方法,码字结构为qc-ira-raptor-like结构,校验矩阵h中包含m个行和n个列,n个列中包含k个信息位和m个校验位。其中:所述k为ldpc 码字的信息位长,所述n为ldpc码字的码字长,且n=k+m。

87.qc-ira-raptor-like ldpc码的具体结构如下所示:

[0088][0089]

对qc-ira-raptor-like结构做出如下说明:

[0090]

h表示校验矩阵,h矩阵由六个矩阵组成,a、p、z、c、d和i。这六个矩阵均是由整数个

大小为q

×

q的循环子块组成,该循环子块可为全零阵、单位阵、或者单位阵向右循环偏移得到的准循环子块。所述校验矩阵h每一行包括j个循环子矩阵,每一列包括l个循环子矩阵,其中每个子矩阵的大小为q

×

q。

[0091]

矩阵a的大小为m1×

k,结构为:

[0092][0093]

其中每个子块h

j,l

的大小为q

×

q,满足如下关系1≤j≤j

a

,1≤l≤l

a

,j

a

·

q=m1, l

a

·

q=k。

[0094]

矩阵c的大小为m2×

k,结构为:

[0095][0096]

其中每个子块h

j,l

的大小为q

×

q,满足如下关系1≤j≤j

c

,1≤l≤l

c

,j

c

·

q=m2, l

c

·

q=k。

[0097]

矩阵d的大小为m2×

m1,结构为:

[0098][0099]

其中每个子块h

j,l

的大小为q

×

q,满足如下关系1≤j≤j

d

,1≤l≤l

d

,j

d

·

q=m2, l

d

·

q=m1。

[0100]

矩阵p的大小为m1×

m1,结构为:

[0101][0102]

其中每个子块均为大小为q

×

q的单位矩阵。矩阵i为m2×

m2的单位矩阵,矩阵z为 m1×

m2的全零矩阵。

[0103]

一个具体的实施例中,码字码率为3/15,信息位长度k为12288,码长n为61440,子块大小为256*256。因此使用(i0,i1,

…

,i

12287

)代表信息位,(p0,p1,

…

,p

49151

)代表校验位,进

而获得最终码字(i0,i1,

…

,i

12287

,p0,p1,

…

,p

49151

)。

[0104]

针对这个具体的实施例的母码,编码方法如下:

[0105]

步骤一、对校验位进行初始化。即令p0=p1=p2=

…

=p

49151

=0。

[0106]

步骤二、根据附录i码率为3/15、码长为61440的ldpc码字的编码码表,将信息位循环累加到校验位上。即对于任意k,0≤k<49152,令将s

k

累加到p

q(i,j,l)

上,即p

q(i,0,j)

=p

q(i,0,j)

+s

k

;p

q(i,1,j)

=p

q(i,1,j)

+s

k

;p

q(i,2,j)

=p

q(i,2,j)

+s

k

;...; p

q(i,w(i)-1,j)

=p

q(i,w(i)-1,j)

+s

k

。

[0107]

其中,q(i,j,0)为第j+1次读取码表中第i+1行的元素,码表见附录i,对任意 l,0<l<256,以上所有的累加计算都在gf(2)中进行。

[0108]

步骤三、对于所有区间(0,1536)中的整数n,有更新后的p

n

=更新前的p

n

+p

n-1

。

[0109]

步骤四、根据附录i码率为3/15、码长为61440的ldpc码字的编码码表,将内校验位循环累加到外校验位上。对于任意k,0≤k<49152,令i=48+[k/256],l=k mod 256。将p

k

累加到p

q(i,j,l)

上,即p

q(i,0,j)

=p

q(i,0,j)

+p

k

;p

q(i,1,j)

=p

q(i,1,j)

+p

k

; p

q(i,2,j)

=p

q(i,2,j)

+p

k

;...;p

q(i,w(i)-1,j)

=p

q(i,w(i)-1,j)

+p

k

。

[0110]

其中,q(i,j,0)为第j+1次读取码表中第i+1行的元素,码表见附录i,对任意 l,0<l<256,以上所有的累加计算都在gf(2)中进行。

[0111]

码率为3/15、码长为61440的ldpc码字的编码码表如下所示:

[0112]

[0113][0114][0115]

与现有技术相比,采用将校验位分为内、外校验位并分别进行编码的方法,ldpc 码字的校验矩阵h为qc-ira-raptor-like结构,并且为该ldpc码字在某个特定码率下设计

了编码码表,本发明具有编码简便,性能良好的优点。

[0116]

优选例2:

[0117]

依据上述目的,实施本发明的一种ldpc码字的编码方法,其特征在于,包括以下步骤:

[0118]

步骤s1:初始化校验位;

[0119]

步骤s2:根据编码码表将信息位累加到内、外校验位上;

[0120]

步骤s3:对内校验位进行自增,得到新的内校验位;

[0121]

步骤s4:根据编码码表将内校验位累加到外校验位上,得到新的外校验位;

[0122]

其中,所述校验位包括内校验位和外校验位。

[0123]

可选的,所述ldpc码字的校验矩阵h为m行n列,n=k+m,n表示ldpc码字的码长,m表示校验位长度,k表示信息位长度,m=m1+m2,m1表示内校验位长度,m2表示外校验位长度;

[0124]

m行按照m1和m2的长度,n列按照k、m1和m2的长度,将校验矩阵h划分为 2行3列的6个子矩阵,其中,第1行第3个子矩阵为全零矩阵,第1行第2个和第2 行第3个子矩阵为单位矩阵,剩余的子矩阵为均由大小为q

×

q的循环子块组成,所述循环子块为全零矩阵、单位矩阵或者单位矩阵向右循环偏移得到的准循环子块。

[0125]

可选的,在所述步骤s1中:对码率为k/n的ldpc码字的校验位(p0,p1,

…

,p

m-1

)进行初始化,即令p0=p1=p2=

…

=p

m-1

=0,其中,m=n-k,m表示校验位长度,n 表示ldpc码字的码长,k表示ldpc码字的信息位长度;

[0126]

校验矩阵h中包含m个行和n个列,n个列中包含k个信息位和m个校验位,m 个校验位又包含m1个内校验位和m2个外校验位;所述校验矩阵h每一行包括l个循环子矩阵,每一列包括j个循环子矩阵,其中每个子矩阵的大小为q

×

q;j

×

q=m, l

×

q=n;设

[0127]

在所述步骤s2中:根据ldpc码字的编码码表,将信息位(s0,s1,

…

,s

k-1

)累加到校验位(p0,p1,

…

,p

m-1

)上;

[0128]

在所述步骤s3中:对内校验位进行累加;

[0129]

在所述步骤s4中:根据ldpc码字的编码码表,将内校验位累加到外校验位上。

[0130]

可选的,设q(i,j,0)为ldpc码字的码表中第i+1行第j+1列元素,则对任意l,0<l<q,其中

[0131]

所述步骤s2为:

[0132]

对于任意k,0≤k<k,令将s

k

累加到p

q(i,j,l)

上,即:

[0133]

p

q(i,j,l)

=p

q(i,j,l)

+s

k

,j=0,1,

…

,w(i)-1;

[0134]

其中w(i)为码表第i+1行的元素个数;

[0135]

所述步骤s3为:

[0136]

p0不变,对于所有n,0<n<m1,依次令p

n

自增p

n-1

;

[0137]

所述步骤s4为:

[0138]

对于任意k,0≤k<m1,令将p

k

累加到p

q(i,j,l)

上,即:

[0139]

p

q(i,j,l)

=p

q(i,j,l)

+p

k

,j=0,1,

…

,w(i)-1

[0140]

其中w(i)为码表第i+1行的元素个数;

[0141]

其中,p

n

、p

k

表示校验位,s

k

表示信息位。

[0142]

可选的,所述ldpc码字的码率为3/15,n=61400,m1=1536,m2=47616,q=256, q1=6,q2=166。

[0143]

可选的,每个子矩阵的大小为256*256。

[0144]

依据上述目的,实施本发明的一种ldpc码字的编码系统,采用前述的ldpc码字的编码方法进行编码,其特征在于,包括:

[0145]

校验位进行初始化模块:对校验位进行初始化;

[0146]

信息位累加模块:根据编码码表将信息位累加到校验位上;

[0147]

校验位自增模块:对内校验位进行自增;

[0148]

校验位累加模块:根据编码码表将内校验位累加到外校验位上。

[0149]

依据上述目的,实施本发明的一种计算机可读存储介质,其特征在于,其处理器用于执行权利要求前述任一项所述的ldpc码字的编码方法。

[0150]

本领域技术人员知道,除了以纯计算机可读程序代码方式实现本发明提供的系统、装置及其各个模块以外,完全可以通过将方法步骤进行逻辑编程来使得本发明提供的系统、装置及其各个模块以逻辑门、开关、专用集成电路、可编程逻辑控制器以及嵌入式微控制器等的形式来实现相同程序。所以,本发明提供的系统、装置及其各个模块可以被认为是一种硬件部件,而对其内包括的用于实现各种程序的模块也可以视为硬件部件内的结构;也可以将用于实现各种功能的模块视为既可以是实现方法的软件程序又可以是硬件部件内的结构。

[0151]

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本申请的实施例和实施例中的特征可以任意相互组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1