振荡电路及自启动控制电路的制作方法

振荡电路及自启动控制电路

【技术领域】

1.本发明系有关一种振荡器,特别是关于一种适用于振荡电路的自启动控制电路。

背景技术:

2.振荡器为一种产生周期振荡信号的电子电路,主要作为协调电子系统当中各种电路的基准。

3.振荡器(例如压控振荡器)可用于振荡电路,例如锁频回路(frequency-locked loop,pll)或锁相回路(phase-locked loop,pll)。振荡器在某些时刻会无法振荡,因此需要一些机制以启动或唤醒振荡器,使其重新开始振荡。

技术实现要素:

4.鉴于上述,本发明实施例的目的之一在于提出一种适用于振荡电路的自启动控制电路,用于自启动振荡电路的振荡器。

5.根据本发明实施例,适用于振荡电路的自启动控制电路包含状态电路及启动电路。状态电路根据振荡电路的压控振荡器的控制电压的电平而产生重置信号。启动电路根据重置信号以产生致能信号,据以启动压控振荡器。

【附图说明】

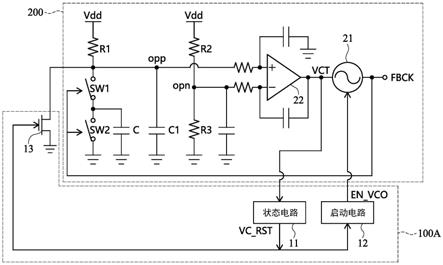

6.图1a显示本发明第一实施例的适用于锁频回路振荡电路的自启动控制电路的电路图。

7.图1b例示自启动控制电路与锁频回路振荡电路的相关信号的时序图。

8.图1c例示图1a的振荡器的电路图。

9.图2a显示本发明实施例的图1a的状态电路的示意图。

10.图2b显示本发明实施例的图1a的启动电路的方框图。

11.图3例示未使用自启动控制电路的锁频回路振荡电路的相关信号的时序图。

12.图4显示本发明第二实施例的适用于锁相回路振荡电路的自启动控制电路的电路图。

13.【符号说明】

14.100a:自启动控制电路

15.100b:自启动控制电路

16.11:状态电路

17.111:比较电路

18.12:启动电路

19.121:计数器

20.122:脉冲发生器

21.13:强制开关

22.200:锁频回路振荡电路

23.21:压控振荡器

24.22:比较器

25.400:锁相回路振荡电路

26.41:分频器

27.42:相位频率检测器

28.43:电荷泵

29.44:低通滤波器

30.fbck:振荡输出

31.vct:控制电压

32.opp:正输入

33.opn:负输入

34.vdd:电源电压

35.r1:第一电阻器

36.r2:第二电阻器

37.r3:第三电阻器

38.c1:电容器

39.c:电容器

40.sw1:第一开关

41.sw2:第二开关

42.sw:开关

43.vc_rst:重置信号

44.en_vco:致能信号

45.vref_h:第一参考电压

46.vref_l:第二参考电压

47.t1~t5:时间

48.out:输出信号

49.ref:参考信号

【具体实施方式】

50.图1a显示本发明第一实施例的适用于锁频回路(fll)振荡电路200的自启动控制电路100a的电路图,图1b例示自启动控制电路100a与锁频回路振荡电路200的相关信号的时序图。

51.锁频回路振荡电路200可包含压控振荡器(vco)21,用于产生振荡输出fbck,其振荡频率受控于控制电压vct。锁频回路振荡电路200可包含比较器22(例如运算放大器与电容器,连接如图所示),其比较(电连接至正输入节点“+”的)正输入opp与(电连接至负输入节点

“-”

的)负输入opn,据以产生控制电压vct。正输入opp的节点可通过第一电阻器r1而电连接至电源电压vdd,并通过电容器c1而电接地。正输入opp的节点可通过第一开关sw1而电连接至电容器c,该电容器c通过第二开关sw2而电接地,其中第一开关sw1与第二开关sw2串

接且操作于相反状态(亦即,一开关为导通则另一开关为断开)。负输入opn的节点连接至分压器,其由第二电阻器r2与第三电阻器r3所组成,连接如图所示。

52.在本实施例中,自启动控制电路100a可包含状态电路11,其决定控制电压vct的电平或状态,据以产生重置信号vc_rst。其中,当控制电压vct高于预设第一参考电压vref_h时,重置信号vc_rst处于第一状态(例如高电平);当控制电压vct低于预设第二参考电压vref_l时,重置信号vc_rst处于第二状态(例如低电平)。图2a显示本发明实施例的图1a的状态电路11的示意图。在本实施例中,状态电路11可包含比较电路111,其通过比较控制电压vct与第一参考电压vref_h、第二参考电压vref_l以产生重置信号vc_rst,其中第一参考电压vref_h大于第二参考电压vref_l。如图1b所例示,在时间t1或t3,当控制电压vct高于预设第一参考电压vref_h时,重置信号vc_rst变为高电平(亦即,第一状态);在时间t2或t4,当控制电压vct低于预设第二参考电压vref_l时,重置信号vc_rst变为低电平(亦即,第二状态)。在一实施例中,如图1b所例示,比较电路111可含有迟滞(hysteresis),用于防止不需要的频繁切换。

53.本实施例的自启动控制电路100a可包含启动电路12,其根据重置信号vc_rst以产生致能信号en_vco,据以启动压控振荡器21。图2b显示本发明实施例的图1a的启动电路12的方框图。在本实施例中,启动电路12可包含计数器121,其存储重置信号vc_rst的特定状态转换(例如从第一状态转换为第二状态)所发生次数。如图1b所例示,在时间t2,计数器121存储数字“1”,代表重置信号vc_rst第一次从第一状态转换为第二状态;在时间t4,计数器121存储数字“2”,代表重置信号vc_rst第二次从第一状态转换为第二状态。

54.在本实施例中,启动电路12可包含脉冲发生器122,当重置信号vc_rst的特定状态转换(例如从第一状态转换为第二状态)所发生次数小于或等于预设计数值时,脉冲发生器122产生预设宽度的致能信号en_vco。如图1b所例示,在时间t2或t4,当重置信号vc_rst从第一状态转换为第二状态且计数器121所存储的数字小于或等于二(亦即,预设计数值)时,脉冲发生器122产生致能信号en_vco。

55.图1c例示图1a的压控振荡器21的电路图。在本实施例中,压控振荡器21可包含多个串联的反向器211,分别受控于电流源212,该电流源212受控于控制电压vct。压控振荡器21可包含开关sw,其包含p型金属氧化物半导体(mos)晶体管,其栅极受控于致能信号en_vco,其源极连接至电源电压vdd,其漏极连接至其中一反向器211(例如图示的第一个反向器)的输入节点。当致能信号en_vco变为低电平时,连接该开关sw的反向器211的输入节点被拉至高电平(例如vdd),因此使得压控振荡器21产生振荡。

56.本实施例的自启动控制电路100a可还包含强制开关13,用于将振荡电路(在本实施例中为锁频回路振荡电路200)的内部节点接地,因而降低控制电压vct。在本实施例中,强制开关13可包含金属氧化物半导体(mos)晶体管(例如n型金属氧化物半导体晶体管),连接于地与正输入opp的节点的间,当重置信号vc_rst处于第一状态(例如高电平)时,强制开关13可将正输入opp的节点接地。

57.在操作自启动控制电路100a与锁频回路振荡电路200时,时间t5之前无振荡发生。当控制电压vct高于第一参考电压vref_h时,重置信号vc_rst(于t1~t2或t3~t4期间)变为高电平,导通强制开关13,以将正输入opp的节点强制放电,因而降低控制电压vct。借此,可避免因太高的控制电压vct造成压控振荡器21的锁死。如图1b所例示,当计数器212所存

储数字达到二(亦即,预设计数值)之后,压控振荡器21在时间t5启动振荡以输出稳定的振荡输出fbck。

58.图3例示未使用自启动控制电路100a的锁频回路振荡电路200的相关信号的时序图。在这个例子中,正输入opp与控制电压vct维持高电平,会锁死压控振荡器21且没有振荡产生。其中,由于振荡输出fbck不再摆动,使得第一开关sw1与第二开关sw停止切换。电源电压vdd通过第一电阻器r1持续对电容器c1充电,进一步增加正输入opp而使得压控振荡器21的锁死更为严重。

59.图4显示本发明第二实施例的适用于锁相回路(pll)振荡电路400的自启动控制电路100b的电路图。锁相回路振荡电路400可包含压控振荡器21,用于产生输出信号out,其振荡频率受控于控制电压vct。锁相回路振荡电路400可包含分频器41,用于将输出信号out的振荡频率分频,以产生振荡输出fbck。锁相回路振荡电路400可包含相位频率检测器(pfd)42,用于比较参考信号ref与振荡输出fbck,将其结果馈至电荷泵(cp)43,因而产生控制电压vct给压控振荡器21。锁相回路振荡电路400可还包含低通滤波器44,其通过控制电压vct当中低于截止频率的成分且衰减控制电压vct当中高于截止频率的成分。

60.在本实施例中,自启动控制电路100b可包含状态电路11,其决定控制电压vct的电平或状态,据以产生重置信号vc_rst。本实施例的自启动控制电路100b可包含启动电路12,其根据重置信号vc_rst以产生致能信号en_vco,据以启动压控振荡器21。本实施例的自启动控制电路100b可还包含强制开关13(例如n型金属氧化物半导体晶体管),用于将振荡电路(在本实施例中为锁相回路振荡电路400)的内部节点接地。在本实施例中,当重置信号vc_rst处于第一状态(例如高电平)时,强制开关13可将控制电压vct的节点接地。自启动控制电路100b的状态电路11、启动电路12及强制开关13类似于自启动控制电路100a的相应组成,其细节不予赘述。

61.在操作自启动控制电路100b与锁相回路振荡电路400时,当振荡输出fbck的频率高于参考信号ref的频率时,电荷泵43进行放电,因而降低控制电压vct与输出信号out的振荡频率。当振荡输出fbck的频率低于参考信号ref的频率时,电荷泵43进行充电,因而提高控制电压vct与输出信号out的振荡频率。当压控振荡器21无振荡时,电荷泵43持续充电以提升控制电压vct,会锁死压控振荡器21且没有振荡产生。通过自启动控制电路100b可避免压控振荡器21因太高的控制电压vct造成压控振荡器21的锁死,且可启动压控振荡器21,其操作类似于前一实施例的自启动控制电路100a,细节不予赘述。

62.以上所述仅为本发明的较佳实施例而已,并非用于限定本发明的权利保护范围;凡其它未脱离发明所揭示的精神下所完成的等效改变或修饰,均应包含在下述的权利要求范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1