具迟滞功能的比较电路与比较模块的制作方法

1.本发明涉及一种具迟滞功能的比较电路与比较模块,且特别是有关兼顾迟滞模式与高增益模式需求的具迟滞功能的比较电路与比较模块。

背景技术:

2.比较电路的用途相当广泛,例如,比较电路可用于模拟与数字转换器(analog to digital converter)、时钟回复电路(clock-recovery circuits)、窗口检测器(window detector),以及施密特触发器(schmitt trigger)等。比较电路接收输入电压vin与参考电压vref后产生输出信号vo,且输出信号vo的电压代表输入电压vin与参考电压vref的大小关系。例如,若输入电压vin大于参考电压vref,则输出信号vo为高电平;以及,若输入电压vin小于参考电压vref,则输出信号vo为低电平。

3.基本的比较电路容易因为输入电压vin受干扰的缘故,导致输出信号vo产生抖动。为此,进一步发展出具迟滞功能的比较电路。具迟滞功能的比较电路具有抗干扰能力强,灵敏度低的特性。因此,具迟滞功能的比较电路在输入电压vin产生微小变动时,输出信号vo并不会立即产生变动,因此具有较佳的抗干扰能力。然而,现有技术的具迟滞功能的比较电路,其迟滞电压vhys的幅度受到参考电压vref的影响。一旦参考电压vref降低,则其迟滞电压vhys也随着降低。连带的,比较电路的准确度受到影响。

技术实现要素:

4.本发明涉及一种比较电路与比较模块,可操作于迟滞模式与高增益模式。在迟滞模式下,比较电路与比较模块可提供不受参考电压变动影响的迟滞电压。通过对晶体管尺寸的选择,可进一步提升比较电路与比较模块在高增益模式下的增益。

5.根据本发明的第一方面,提出一种具迟滞功能的比较电路。比较电路包含:输入电路、外接电路以及耦合模块。输入电路包含:第一输入晶体管与第二输入晶体管。第一输入晶体管接收参考电压,第二输入晶体管接收比较电压。外接电路包含:第一外接晶体管与第二外接晶体管。第一外接晶体管经第一节点而电连接于第一输入晶体管,第二外接晶体管经第二节点而电连接于第二输入晶体管。耦合模块包含:第一电流放大率电路与第二电流放大率电路。第一电流放大率电路,包含:第一耦合晶体管与第二耦合晶体管。第一耦合晶体管具有第一端、第二端与控制端。第一耦合晶体管的第二端电连接于第一节点,且第一耦合晶体管的控制端选择性电连接于第一节点与第二节点中的一者。第二耦合晶体管具有第一端、第二端与控制端。第二耦合晶体管的第二端电连接于第二节点,且第二耦合晶体管的控制端选择性电连接于第一节点与第二节点中的一者。第二电流放大率电路包含:第三耦合晶体管与第四耦合晶体管。第三耦合晶体管具有第一端、第二端与控制端。第三耦合晶体管的第二端选择性电连接于第一节点与第二节点中的一者,且第三耦合晶体管的控制端电连接于第二节点。第四耦合晶体管具有第一端、第二端与控制端。第四耦合晶体管的第二端选择性电连接于第一节点与第二节点中的一者,且第四耦合晶体管的控制端电连接于第一

节点。

6.根据本发明的第二方面,提出一种具迟滞功能的比较模块,包含彼此电连接的第一电阻、第二电阻,以及比较电路。第一电阻接收输入电压。第二电阻接收接地电压。其中,比较电压根据输入电压、第一电阻的电阻值,与第二电阻的电阻值而决定。比较电路包含:输入电路、外接电路以及耦合模块。输入电路包含:第一输入晶体管与第二输入晶体管。第一输入晶体管接收参考电压,第二输入晶体管接收比较电压。外接电路包含:第一外接晶体管与第二外接晶体管。第一外接晶体管经第一节点而电连接于第一输入晶体管,第二外接晶体管经第二节点而电连接于第二输入晶体管。耦合模块包含:第一电流放大率电路与第二电流放大率电路。第一电流放大率电路包含:第一耦合晶体管与第二耦合晶体管。第一耦合晶体管具有第一端、第二端与控制端。第一耦合晶体管的第二端电连接于第一节点,且第一耦合晶体管的控制端选择性电连接于第一节点与第二节点中的一者。第二耦合晶体管具有第一端、第二端与控制端。第二耦合晶体管的第二端电连接于第二节点,且第二耦合晶体管的控制端选择性电连接于第一节点与第二节点中的一者。高电流放大率电路包含:第三耦合晶体管与第四耦合晶体管。第三耦合晶体管具有第一端、第二端与控制端。第三耦合晶体管的第二端选择性电连接于第一节点与第二节点中的一者,且第三耦合晶体管的控制端电连接于第二节点。第四耦合晶体管具有第一端、第二端与控制端。第四耦合晶体管的第二端选择性电连接于第一节点与第二节点中的一者,且第四耦合晶体管的控制端电连接于第一节点。

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

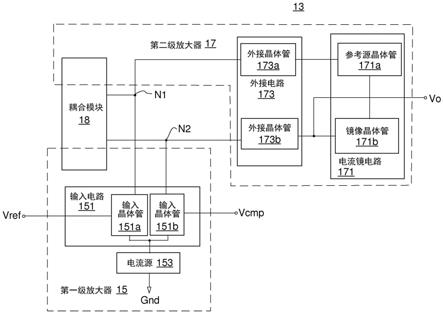

8.图1,其是根据本发明构想的比较模块的示意图。

9.图2a,其是图1的比较电路随着比较电压vcmp的不同,对应产生输出信号vo的示意图。

10.图2b,其是图1的比较模块随着输入电压vin的不同,对应产生输出信号vo的示意图。

11.图3,其是根据本发明构想的比较电路的实施例的方框图。

12.图4,其是根据本发明实施例的比较电路的内部电路的示意图。

13.图5a,其是比较电路在迟滞模式(mode1)下,比较电压vcmp与输出信号vo的关系的示意图。

14.图5b,其是比较电路在高增益模式(mode2)下,比较电压vcmp与输出信号vo的关系的示意图。

15.图6a,其是以传输闸实现开关s1~s4的示意图。

16.图6b,其是耦合模块的内部电路在迟滞模式(mode1)时的连接关系。

17.图7a、图7b,其是比较电路在迟滞模式(mode1)时的电流流向的示意图。

18.图8a,其是以传输闸实现开关s5~s8的示意图。

19.图8b,其是耦合模块的内部电路在高增益模式(mode2)时的连接关系。

20.图9,其是比较电路在高增益模式(mode2)时的电流流向的示意图。

21.图10,其是耦合模块所包含的晶体管的示意图。

22.图11,其是依据比较电路所处的模式不同,动态地调整耦合模块内的晶体管的连接方式的示意图。

具体实施方式

23.请参见图1,其是根据本发明构想的比较模块的示意图。比较模块10包含电阻r1、r2,以及比较电路13。其中假设比较电路13具有迟滞电压vhys。

24.电阻r1的一端电连接于输入电压vin,另一端电连接于比较节点ncmp。电阻r2的一端电连接于比较节点ncmp,另一端电连接于接地电压gnd。为便于说明,本文将比较节点ncmp的电压定义为比较电压vcmp,以及直接以r1、r2分别代表电阻r1、r2的电阻值。

25.比较电路13的反向输入端(inverting terminal)接收参考电压vref、非反向输入端(non-inverting terminal)接收比较电压vcmp后,产生输出信号vo。另,比较电路10还可包含反向器11a、11b。反向器11a的输入端电连接于比较电路13的输出端。反向器11b的输入端电连接于反向器11a的输出端,且反向器11a、11b的输出端均电连接于比较电路13。反向器11a、11b的输出端输出反馈至比较电路13的控制信号sct、sctn。其中,控制信号sctn的相位与输出信号vo的相位同向,控制信号sct的相位与输出信号vo的相位反向。

26.比较电路13接收参考电压vref与比较电压vcmp。其中,参考电压vref的大小可根据应用的不同而改变。针对同一种应用下,则参考电压vref的大小为一预设值。另一方面,比较电压vcmp的大小则随着输入电压vin而变化。由于在图1中,电阻r1、r2彼此串联,且电阻r1接收输入电压vin。比较电压vcmp可根据输入电压vin与电阻值r1、r2,搭配分压公式计算得出。即,比较电压vcmp=[r2/(r1+r2)]*vin。

[0027]

请参见图2a,其是图1的比较电路随着比较电压vcmp的不同,对应产生输出信号vo的示意图。在此附图中,纵轴为输出信号vo,横轴为比较电压vcmp。

[0028]

当比较电路13所接收的比较电压vcmp等于参考电压vref时,比较电路13所产生的输出信号vo的电平将发生变化。例如,由低电平变成高电平,或是由高电平变成低电平。此时的比较电压vcmp的电压值称为反转点。在图2中,共绘式两个反转点,分别代表向上反转电压vinvu与向下反转电压vinvd。

[0029]

首先说明比较电压vcmp由0v开始持续增加时,输出信号vo的变化方式。假设比较电压vcmp一开始等于0v时,此时输出信号vo为低电平。当比较电压vcmp持续增加但仍小于向上反转电压vinvu时,输出信号vo均维持为低电平。当比较电压vcmp持续增加至等于向上反转电压vinvu时,输出信号vo将瞬间由低电平转换为高电平。若比较电压vcmp持续增加并仍大于向上反转电压vinvu时,输出信号vo均维持为高电平。

[0030]

接着说明比较电压vcmp由向上反转电压vinvu逐渐减少时,输出信号vo的变化方式。假设比较电压vcmp一开始等于向上反转电压vinvu,此时输出信号vo为高电平。当比较电压vcmp持续下降至接近但仍略大于向下反转电压vinvd时,输出信号vo均维持为高电平。当比较电压vcmp持续降低至向下反转电压vinvd时,输出信号vo将瞬间由高电平转换为低电平。其后,当比较电压vcmp持续降低的过程中,输出信号vo维持在低电平。向上反转电压vinvu与向下反转电压vinvd之间的差值定义为迟滞电压vhys。

[0031]

根据前述说明可以得知,当输出信号vo产生变化时,比较电路13的输入端所接收

的参考电压vref与比较电压vcmp相等,其中比较电压vcmp=[r2/(r1+r2)]*vin。亦即,此时可以得出式(1)。

[0032]

vref=vcmp=[r2/(r1+r2)]*vin..............式(1)

[0033]

将式(1)进一步加以转换后,可以得知,在比较电压vcmp处于反转点时,式(2)成立。

[0034]

vin=vref*[(r1+r2)/r2]................式(2)

[0035]

由式(2)可以得出使输出信号vo产生反转时的输入电压vin=vref*[(r1+r2)/r2]。据此,图1所示的比较模块10的输入电压vin的翻转点(vref*[(r1+r2)/r2])取决于参考电压vref与电阻r1、r2的电阻值。

[0036]

请参见图2b,其是图1的比较模块随着输入电压vin的不同,对应产生输出信号vo的示意图。由于比较电压vcmp可根据输入电压vin与电阻r1、r2的电阻值而可表示为vcmp=[r2/(r1+r2)]*vin。经过转换后,相当于输入电压vin可表示为分压系数(r1+r2)/r2与输入电压vcmp相乘的结果,即,vin=(r1+r2)/r2*vcmp。因此,图2b所示的各个数值(迟滞电压vhys_in、向上反转电压vinvu_in、向下反转电压vinvd_in),可通过将图2a所示的比较电路13的各个数值(迟滞电压vhys、向上反转电压vinvu、向下反转电压vinvd)乘上分压系数(r1+r2)/r2后得出。

[0037]

比较电路13的运行可分为两种模式,一为迟滞模式(hysteresis mode),一为高增益模式(high gain mode)。为便于说明,本文将迟滞模式定义为mode1,以及将高增益模式定义为mode2。在迟滞模式(mode1)下,比较电路13需要能对输入电压vcmp的电压变化提供良好的抗噪声能力;在高增益模式(mode2)下,比较电路13需要提供高增益,使输出信号vo可快速反应输入电压vcmp与参考电压vref之间的压差。

[0038]

请参见图3,其是根据本发明构想的比较电路的实施例的方框图。比较电路13包含:输入电路151、电流源153、耦合模块18、外接电路173,以及电流镜电路(current mirror circuit)171。此外,比较电路13可进一步划分为第一级放大器15与第二级放大器17。第一级放大器15提供第一级增益为a

vn1

,第二级放大器17提供第二级增益a

vn2

。

[0039]

第一级放大器15包含输入电路151、电流源153,以及耦合模块18中的一部分。其中,输入电路151进一步包含输入晶体管151a、151b。第一级放大器15经由输入晶体管151a接收参考电压vref,以及通过输入晶体管151b接收比较电压vcmp。电流源153提供流经输入电路151的总和电流。第一级放大器15在节点n1、n2产生第一级放大信号。

[0040]

第二级放大器17包含外接电路173、电流镜电路171,以及耦合模块18中的一部分。其中,外接电路173进一步包含外接晶体管173a、173b。外接晶体管173a电连接于节点n1,外接晶体管173b电连接于节点n2。电流镜电路171进一步包含参考源晶体管171a与镜像晶体管171b。其中,参考源晶体管171a电连接于外接晶体管173a,镜像晶体管171b电连接于外接晶体管173b。第二级放大器17自节点n1、n2接收第一级放大信号后,进一步提供第二级增益a

vn2

并产生第二级放大信号(相当于输出信号vo)。

[0041]

请参见图4,其是根据本发明实施例的比较电路的内部电路的示意图。请同时参见图3与图4。

[0042]

输入电路151包含晶体管mn1(输入晶体管151a)、mn2(输入晶体管151b)。晶体管mn1的栅极接收参考电压vref,晶体管mn2的栅极接收比较电压vcmp。晶体管mn1、mn2的漏极

分别通过节点n1、n2而分别电连接于耦合模块18,且晶体管mn1、mn2的源极均电连接于电流源153。

[0043]

电流源153包含晶体管mn5,其源极电连接于接地电压gnd、漏极电连接于晶体管mn1、mn2的源极;且其栅极持续接收偏压vpb。因偏压vpb持续导通晶体管mn5的缘故,晶体管mn5持续产生总和电流i

mn5

。

[0044]

在电流镜电路171中,晶体管mn3作为提供参考电流(imn3)的参考源晶体管171a,晶体管mn4则作为对应参考电流(imn3)而产生镜像电流(imn4)的镜像晶体管171b。晶体管mn3的漏极与栅极相连,并共同连接至晶体管mn4的栅极。晶体管mn3、mn4的源极均电连接于接地电压gnd。晶体管mn3的漏极电连接于外接晶体管173a,且晶体管mn4的漏极电连接于外接晶体管173b。

[0045]

晶体管mp1、mp2分别作为外接晶体管173a、173b使用。晶体管mp1、mp2的源极均电连接于供应电压vdd。晶体管mp1的漏极电连接于晶体管mp3的漏极;栅极电连接于节点n1。晶体管mp2的漏极电连接于晶体管mp4的漏极;栅极电连接于节点n2。在此附图中,假设晶体管mp1~mp6为pmos晶体管,以及假设晶体管mn1~mn5为nmos晶体管。实际应用时,晶体管的种类并不以此实施例为限。

[0046]

由图4可以看出,耦合模块18包含晶体管mp3~mp6以及开关s1~s8。在本文中,晶体管mp3~mp6的源极均电连接于供应电压vdd。另,因晶体管mp3~mp6的栅极与漏极的耦合方式可能改变,可将其称为耦合晶体管。请参见表1,其是开关s1~s8的连接方式列表。

[0047]

表1

[0048]

开关与开关相连的节点与开关相连的晶体管s1n1晶体管mp5的漏极s2n2晶体管mp6的漏极s3n1晶体管mp3的栅极s4n2晶体管mp4的栅极s5n2晶体管mp5的漏极s6n1晶体管mp6的漏极s7n2晶体管mp3的栅极s8n1晶体管mp4的栅极

[0049]

接着按照晶体管mp3~mp6的顺序分别说明,随着开关s1~s8的切换,晶体管mp3~mp6与节点n1、n2之间形成的连接关系。请同时参见图4与表1。

[0050]

晶体管mp3的栅极同时电连接于开关s3、s7。若开关s3导通,晶体管mp3的栅极将电连接于节点n1;若开关s7导通,晶体管mp3的栅极将电连接于节点n2。由于开关s3、s7轮流导通,晶体管mp3的栅极并不会同时连接至节点n1、n2。另,晶体管mp3的漏极直接电连接于节点n1。

[0051]

晶体管mp4的栅极同时电连接于开关s8、s4。若开关s8导通,晶体管mp4的栅极将电连接于节点n1;若开关s4导通,晶体管mp4的栅极将电连接于节点n2。由于开关s8、s4轮流导通,晶体管mp4的栅极并不会同时连接至节点n1、n2。另,晶体管mp4的漏极直接电连接于节点n2。

[0052]

晶体管mp5的栅极直接电连接于节点n1。另,晶体管mp5的漏极同时电连接于开关

s1、s5。若开关s1导通,晶体管mp5的漏极将电连接于节点n1;若开关s5导通,晶体管mp5的漏极将电连接于节点n2。由于开关s1、s5轮流导通,晶体管mp5的漏极并不会同时连接至节点n1、n2。

[0053]

晶体管mp6的栅极直接电连接于节点n1。另,晶体管mp6的漏极同时电连接于开关s6、s2。若开关s6导通,晶体管mp6的漏极将电连接于节点n1;若开关s2导通,晶体管mp6的漏极将电连接于节点n2。由于开关s6、s2轮流导通,晶体管mp6的栅极并不会同时连接至节点n1、n2。

[0054]

根据前述描述,晶体管mp3~mp6的连接方式可分为两种类型:第一种类型为栅极的电连接方式固定,但漏极根据模式不同而改变所连接的节点(即,晶体管mp5、mp6);第二种类型为漏极的电连接方式固定,但栅极根据模式不同而所连接的节点(即,晶体管mp3、mp4)。在本文中,可根据电流放大率的不同,将晶体管mp5、mp6定义为高电流放大率晶体管,以及,将晶体管mp3、mp4定义为低电流放大率晶体管。并且,将晶体管mp5、mp6的组合定义为高电流放大率电路,将晶体管mp3、mp4的组合定义为低电流放大率电路。

[0055]

根据本发明构想的实施例,开关s1~s8可分为两个部分,其中一部分(包含开关s1~s4)由控制信号sct控制,另一部分(包含开关s5~s8)由控制信号sctn控制。表2为开关s1~s8在何种模式下导通,以及与其对应的控制信号的列表。

[0056]

表2

[0057][0058]

如图1所示,输出信号vo经过反向器11a后产生控制信号sct,且控制信号sct经过反向器11b后产生控制信号sctn。因此,控制信号sct与输出信号vo反向,且控制信号sctn与输出信号vo同向。

[0059]

由于输出信号vo在迟滞模式(mode1)为低电平,控制信号sct、sctn在迟滞模式(mode1)分别为高电平与低电平。连带的,由控制信号sct所控制的开关s1~s4将在迟滞模式(mode1)导通,且由控制信号sctn所控制的开关s5~s8将在迟滞模式(mode1)断开。也因此,开关s1将导通节点n1与晶体管mp5的漏极;开关s2将导通节点n2与晶体管mp6的漏极;开关s3将导通节点n1与晶体管mp3的栅极;以及,开关s4将导通节点n2与晶体管mp4的栅极。

[0060]

另一方面,由于输出信号vo在高增益模式(mode2)为高电平,控制信号sct、sctn在高增益模式(mode2)分别为低电平与高为准。连带的,由控制信号sct所控制的开关s1~s4将在高增益模式(mode2)断开,且由控制信号sctn所控制的开关s5~s8将在高增益模式(mode2)导通。也因此,开关s5将导通节点n2与晶体管mp5的漏极;开关s6将导通节点n1与晶体管mp6的漏极;开关s7将导通n2与晶体管mp3的栅极;以及,开关s8将导通节点n1与晶体管mp4的栅极。

[0061]

为便于说明,在本文中,针对与各晶体管mn1~mn5、mp1~mp相关的符号,均以下标和小写字母代表。例如,将流经晶体管mp1的电流表示为i

mp1

,将晶体管mp6的电流放大率表示为β

mp6

;将晶体管mp3的通道宽度表示为w

mp3

;以及,将晶体管mp3的通道长度表示为l

mp3

等。关于其他与各个晶体管相关的特性的表示方式亦可类推得出,此处不予详述。

[0062]

请参见图5a,其是比较电路在迟滞模式(mode1)下,比较电压vcmp与输出信号vo的关系的示意图。图5a以线条l1代表比较电路13在迟滞模式(mode1)的电路行为,即,比较电压vcmp自0v增加至向上反转电压vinvu的过程。线条l1相当于比较电压vcmp虽有小幅变动,但变动范围仍小的情况。比较电路13在迟滞模式(mode1)需有较佳的抗噪声能力。线条l1进一步包含线段l1a、l1b、l1c,关于这些线段l1a、l1b、l1c的说明,请参见下文。

[0063]

请参见图5b,其是比较电路在高增益模式(mode2)下,比较电压vcmp与输出信号vo的关系的示意图。图5b以线条l2代表比较电路在高增益模式(mode2)的电路行为,即,比较电压vcmp自向上反转电压vinvu下降至等于向下反转电压vinvd的过程。线条l2相当于比较电压vcmp的变化须能实时反应于输出信号vo的情况,即,比较电路13须能让产生的输出信号vo迅速反应其输入端的比较电压vcmp与参考电压vref的电压差的情况。比较电路13在高增益模式(mode2)需提供较高的增益。

[0064]

由图5a可以看出,在迟滞模式(mode1)时,比较电路13需要维持输出信号vo的稳定,不希望因为比较电压vcmp的些微变化使输出信号vo产生波动。另一方面,由图5b可以看出,在高增益模式(mode2)时,比较电路13需要输出信号vo能快速反应在输入端的信号变化。

[0065]

根据本发明构想的实施例,比较电路13中的耦合模块18具有弹性化的设计。在这种弹性化设计的架构下,可随着迟滞模式(mode1)与高增益模式(mode2)的不同,对开关s1~s8进行切换。随着开关s1~s8的切换,晶体管mp3~mp6与节点n1、n2的连接关系也将改变,进而使第一级放大器15、第二级放大器17的配置随着模式的改变而变动。

[0066]

接着,以图6a、图6b、图7a、图7b说明比较电路13在迟滞模式(mode1)的操作。请参见图6a,其是以传输闸(transmission gate)实现开关s1~s4的示意图。用于实现开关s1~s4的传输闸包含pmos晶体管p1与nmos晶体管n1,其中nmos晶体管n1的栅极接收控制信号sct、pmos晶体管p1的栅极接收控制信号sctn。

[0067]

请同时参见图5a与图6a。由图5a可以看出,输出信号vo在迟滞模式(mode1)时为低电平。因此,在迟滞模式(mode1)时,控制信号sct为高电平且控制信号sctn为低电平。在此同时,图6a所示的nmos晶体管n1的栅极为高电平的控制信号sct,且pmos晶体管p1的栅极为低电平的控制信号sctn,故开关s1~s4将导通。

[0068]

另请参见图5b与图6a,由图5b可以看出,输出信号vo在高增益模式(mode2)时为高电平。因此,在高增益模式(mode2)时,控制信号sct为低电平且控制信号sctn为高电平。在此同时,图6a所示的nmos晶体管n1的栅极为低电平的控制信号sct,且pmos晶体管p1的栅极为高电平的控制信号sctn,故开关s1~s4将断开。

[0069]

请参见图6b,其是耦合模块的内部电路在迟滞模式(mode1)时的连接关系。如图4的说明,在迟滞模式(mode1)时,开关s1~s4为导通;开关s5~s8为断开。为更清楚呈现晶体管之间的连接关系,图6b并未绘式处于断开状态的开关s5~s8。表3进一步汇整晶体管mp3~mp6的端点在迟滞模式(mode1)时的连接关系。

[0070]

表3

[0071][0072]

请同时参见图6b与表3。在迟滞模式(mode1)时,晶体管mp3的源极电连接于供应电压vdd、漏极电连接于节点n1,与门极因开关s3导通而电连接于节点n1;晶体管mp4的源极电连接于供应电压vdd、漏极电连接于节点n2,且栅极因开关s4导通而电连接于节点n2;晶体管mp5的源极电连接于供应电压vdd、漏极因开关s1导通而电连接于节点n2,且栅极电连接于节点n2;晶体管mp6的源极电连接于供应电压vdd、漏极因开关s2导通而电连接于节点n2,且栅极电连接于节点n1。

[0073]

请参见图7a、图7b,其是比较电路在迟滞模式(mode1)时的电流流向的示意图。比较电路13在迟滞模式(mode1)时,耦合模块18中的开关s1~s8与晶体管mp3~mp6的连接方式如图6b所示。为便于说明,在图7a、图7b中,已进一步省略图6b中的开关s1~s4,并调整晶体管的位置,使元件之间的连线关系较为简洁。

[0074]

请同时参见图5a的线段l1a与图7a。图5a的线段l1a对应于比较电压vmp小于临界电压vth的情形。首先说明栅极与节点n1相连的晶体管(mp3、mp1、mp6)的状态。此时,晶体管mn1因栅极持续接收参考电压vref的缘故而导通,产生流经晶体管mn1的电流i

mn1

。此时,因为电流i

mn1

的缘故,使节点n1的电压降低,进而使晶体管mp3、mp1、mp6导通。

[0075]

接着说明栅极与节点n2相连的晶体管(mp5、mp4、mp2)的状态。此时,经由晶体管mn2经由栅极所接收的比较电压vcmp相当小,仍不足以导通晶体管mn2。因此,晶体管mn2处于断开状态。连带的,晶体管mp5、mp4、mp2的栅极也因与节点n2相连而为浮接状态。因此,晶体管mp5、mp4、mp2将断开。

[0076]

此时,晶体管mp6虽然因栅极接收节点n1的低电压而导通,但因晶体管mp6的漏极连接至处于浮接状态的节点n2,故尚无电流流经晶体管mp6。因此,在图7a中,流经晶体管mn5的总和电流i

mn5

全部来自流经晶体管mn1的电流i

mn1

。

[0077]

当比较电压vcmp逐渐增加至vcmp=vref-vgs

mn1

+vt

mn2

时,晶体管mn2开始导通。据此,可将图7a中的临界电压vth定义为,vth=vref-vgs

mn1

+vt

mn2

。

[0078]

请同时参见图5a的线段l1b与图7b。比较电压vcmp由临界电压vth增加至接近但仍小于向上反转电压vinvu。

[0079]

首先说明栅极与节点n1相连的晶体管(mp3、mp1、mp6)的状态。此时,晶体管mn1因栅极持续接收参考电压vref的缘故而导通,产生流经晶体管mn1的电流i

mn1

。此时,因为电流i

mn1

的缘故,使节点n1的电压降低,进而使晶体管mp3、mp1、mp6导通。此时,流经晶体管mn1的电流i

mn1

等于流经晶体管mp3的电流i

mp3

。

[0080]

接着说明栅极与节点n2相连的晶体管(mp5、mp4、mp2)的状态。此时,经由晶体管

mn2的栅极所接收的比较电压vcmp已足以导通晶体管mn2。因此,晶体管mn2处于导通状态。此时,流经晶体管mp6的电流i

mp6

将使节点n2的电压升高,并使晶体管mp5、mp4、mp2维持断开。此时,流经晶体管mp6的电流i

mp6

将进一步流经晶体管mn2,形成电流i

mn2

。即,i

mp6

=i

mn2

。

[0081]

因此,在图7b中,流经晶体管mn5的总和电流i

mn5

部分来自流经晶体管mn1的电流i

mn1

,部分来自流经晶体管mn2的电流i

mn2

。且,因为晶体管mp5断开的缘故,流经晶体管mn1的电流i

mn1

等于流经晶体管mp3的电流i

mp3

(即,i

mn1

=i

mp3

);因为晶体管mp4断开的缘故,流经晶体管mn2的电流i

mn2

等于流经晶体管mp6的电流i

mp6

(即,i

mn2

=i

mp6

)。其中,流经晶体管mp6的电流i

mp6

与流经晶体管mp3的电流i

mp3

之间的关系,可根据晶体管mp6的电流放大率β

mp6

、晶体管mp3的β

mp3

表示为,i

mp6

<(β

mp6

/β

mp3

)*i

mp3

。

[0082]

请同时参见图5a的线段l1c与图7b。当比较电压vcmp等于向上反转电压vinvu时,流经晶体管mp6的电流i

mp6

进一步增加,且流经晶体管mp3的电流i

mp6

与流经晶体管mp6的电流i

mp3

的关系为,i

mp6

=(β

mp6

/β

mp3

)*i

mp3

。

[0083]

与线段l1c对应的电流关系可整理如式(3)~式(6)。

[0084]

i

mn1

=i

mp3

...................................式(3)

[0085]

i

mn2

=i

mp6

....................................式(4)

[0086]

i

mp6

=(β

mp6

/β

mp3

)*i

mp3

=[(w

mp6

/l

mp6

)/(w

mp3

/l

mp3

)]*i

mp3

.....式(5)

[0087]

i

mn2

=i

mn5-i

mn1

...............................式(6)

[0088]

在图7b中,参考电压vref可表示为晶体管mn1的栅极与源极的压差(vgs

mn1

),以及晶体管mn5的漏极与源极之间的压差(vds

mn5

)的总和,如式(7)所示。

[0089]

vref=vgs

mn1

+vds

mn5

..........................式(7)

[0090]

另一方面,在图7b中,比较电压vcmp可表示为晶体管mn2的栅极与源极的压差(vgs

mn2

),以及晶体管mn5的漏极与源极之间的压差(vds

mn5

)的总和,如式(8)所示。

[0091]

vcmp=vgs

mn2

+vds

mn5

.........................式(8)

[0092]

再者,于向上反转点时,比较电压vcmp相当于参考电压vref与迟滞电压vhys的总和,如式(9)所示。

[0093]

vcmp=vref+vhys...........................式(9)

[0094]

根据式(8)与式(9),可进一步推导出式(10)。

[0095]

vcmp=vref+vhys=vgs

mn2

+vds

mn5

................式(10)

[0096]

接着,利用式(10),可将迟滞电压vhys表示为,晶体管mn2的栅极与源极之间的压差(vgs

mn2

),以及晶体管mn1的栅极与源极之间的压差(vgs

mn1

)彼此的差值,如式(11)所示。

[0097]

vhys=vgs

mn2

+vds

mn5-v

ref

[0098]

=vgs

mn2

+vds

mn5-(vgs

smn1

+vds

mn5

)

[0099]

=vgs

mn2-vgs

mn1

.............................式(11)

[0100]

根据晶体管的电流公式,流经晶体管mn2的电流i

mn2

可根据晶体管mn2的栅极与源极之间的压差vgs

mn2

,以及与晶体管mn2的电流放大率β

mn2

而表示为

[0101]

[0102]

同样的,流经晶体管mn1的电流i

mn1

可根据晶体管mn1的栅极与源极之间的压差vgs

mn1

,以及与晶体管mn1的电流放大率β

mn1

而表示为,

[0103][0104][0105]

根据式(12)、式(13),可以进一步整理式(11)并将迟滞电压vhys表示为式(14)。

[0106][0107]

由式(14)可以看出,比较电路13的迟滞电压vhys仅与晶体管mn1的电流放大率β

mn1

、晶体管mn2的电流放大率β

mn2

,流经晶体管mn1的电流i

mn1

,以及流经晶体管mn2的电流i

mn2

相关。据此,迟滞电压vhys并不因参考电压vref的大小所影响。

[0108]

根据前述说明可以得知,在迟滞模式(mode1)下,晶体管mp5、mp4、mp2维持断开,晶体管mn1、mp4、mp1、mn3、mn4、mn5维持导通。另,晶体管mn2在比较电压vcmp小于临界电压vth(即,vcmp<vth)时为断开,但是当比较电压vcmp大于或等于临界电压vth(即,vcmp≥vth)时,晶体管mn2将导通。

[0109]

接着,以图8a、图8b、图9说明比较电路13在高增益模式(mode2)的操作。请参见图8a,其是以传输闸实现开关s5~s8的示意图。用于实现开关s5~s8的传输闸包含pmos晶体管p2与nmos晶体管n2,其中nmos晶体管n2的栅极接收控制信号sctn、pmos晶体管p2的栅极接收控制信号sct。

[0110]

请同时参见图5a与图8a。由图5a可以看出,输出信号vo在迟滞模式(mode1)时为低电平。因此,在迟滞模式(mode1)时,控制信号sct为高电平且控制信号sctn为低电平。在此同时,图8a所示的nmos晶体管n2的栅极为低电平的控制信号sctn,且pmos晶体管p2的栅极为高电平的控制信号sct,故开关s5~s8将断开。

[0111]

另请参见图5b与图8a,由图5b可以看出,输出信号vo在高增益模式(mode2)时为高电平。因此,在高增益模式(mode2)时,控制信号sct为低电平且控制信号sctn为高电平。在此同时,图8a所示的nmos晶体管n2的栅极为高电平的控制信号sctn,且pmos晶体管p2的栅极为低电平的控制信号sct,故开关s5~s8将导通。

[0112]

请参见图8b,其是耦合模块的内部电路在高增益模式(mode2)时的连接关系。如前所述,在高增益模式(mode2)时,开关s1~s4为断开;开关s5~s8为导通。为更清楚呈现晶体管之间的连接关系,图8b并未示出处于断开状态的开关s1~s4。表4进一步汇整晶体管mp3~mp6的端点在高增益模式(mode2)时的连接关系。

[0113]

表4

[0114][0115]

请同时参见图8b与表4。在高增益模式(mode2)时,晶体管mp3的源极电连接于供应电压vdd、漏极电连接于节点n1,与门极因开关s7导通而电连接于节点n2;晶体管mp4的源极电连接于供应电压vdd、漏极电连接于节点n2,且栅极因开关s8导通而电连接于节点n1;晶体管mp5的源极电连接于供应电压vdd、漏极因开关s5导通而电连接于节点n2,且栅极电连接于节点n2;晶体管mp6的源极电连接于供应电压vdd、漏极因开关s6导通而电连接于节点n1,且栅极电连接于节点n1。

[0116]

请参见图9,其是比较电路在高增益模式(mode2)时的电流流向的示意图。比较电路13在高增益模式(mode2)时,耦合模块18中的开关s1~s8与晶体管mp3~mp6的连接方式如图6b所示。为便于说明,在图9中,已进一步省略图8b中的开关s5~s8,并调整晶体管的位置,使元件之间的连线关系较为简洁。此时,晶体管mp3、mp4均为导通,并产生流经晶体管mp3的电流i

mp3

、流经晶体管mp4的电流i

mp4

。

[0117]

承上所述,在图9中,电流之间具有以下关系。流经晶体管mn1的电流i

mn1

为流经晶体管mp3的电流i

mp3

与流经晶体管mp6的电流i

mp6

的总和(即,i

mn1

=i

mp3

+i

mp6

);流经晶体管mn2的电流i

mn2

为流经晶体管mp4的电流i

mp4

与流经晶体管mp5的电流i

mp5

的总和(即,i

mn2

=i

mp4

+i

mp5

);以及,流经晶体管mn5的总和电流i

mn5

为流经晶体管mn1的电流i

mn1

与流经晶体管mn2的电流i

mn2

的总和(即,i

mn5

=i

mn1

+i

mn2

)。

[0118]

在图9中,晶体管mp5、mp6、mp1、mp2、mn3、mn4,共同形成根据节点n1、n2的电压而产生输出信号vo的第二级放大器17。由第二级放大器17所提供的第二级增益a

vn2

,可以根据晶体管mp2的互导(transconductance)gm

mp2

、晶体管mp2的源极和漏极间的电导(电阻倒数)gds

mp2

与晶体管mn4的源极和漏极间的电导gds

mn4

表示如下。

[0119][0120]

另,晶体管mn1、mn2、mp3、mp4共同形成根据参考电压vref与比较电压vcmp而决定节点n1、n2的电压的第一级放大器15。第一级放大器15所提供的第一级增益a

vn1

可以根据晶体管mn2的互导gm

mn2

、晶体管mp5的互导gm

mp5

、晶体管mp4的互导gm

mp4

表示如下。

[0121][0122]

[0123]

又,晶体管的互导的比率等于电流放大率的比率,即,因此,式(16)的第一级增益a

vn1

可进一步表示为式(17)。

[0124][0125]

依据式(17)的第一级增益a

vn1

,与式(15)的第二级增益a

vn2

,可进一步计算比较电路13在高增益模式(mode2)时的增益a

vn

。如式(18)所示,比较电路13在高增益模式(mode2)时的增益a

vn

可表示为第一级增益a

vn1

与第二级增益a

vn2

的乘积。

[0126][0127]

由式(18)看出,本公开的比较电路架构相当于,在计算增益a

vn

时,额外引进一个增益系数通过选择合适的电流放大率β

mp4

、β

mp5

,可以增加增益系数c的数值,进而提升增益的效果。例如,若选择电流放大率β

mp4

、β

mp5

之间的比率(β

mp4

/β

mp

)为β

mp4

/β

mp5

=3/4,则增益系数c=4。连带的,增益a

vn

可进一步增加四倍。

[0128]

根据图9的说明可以得知,若晶体管mp4的电流放大率β

mp4

小于晶体管mp5的电流放大率β

mp5

(即,β

mp4

<β

mp5

)时,可以提升比较电路13的增益a

vn

。即,若在第一级放大器15使用具有较小的电流放大率的晶体管mp3、mp4,以及在第二级放大器17使用具有较大的电流放大率的晶体管mp5、mp6,便可提升比较电路13在高增益模式(mode2)下的增益a

vn

。

[0129]

请参见表5,其是汇整耦合模块18内的晶体管,因应不同操作模式而改变其端点的连接方式比较表。关于表5的详细内容,已于前文说明,此处不再详述。

[0130]

表5

[0131][0132]

请参见图10,其是耦合模块所包含的晶体管的示意图。在图10中,耦合模块18包含开关电路185、高电流放大率电路18a与低电流放大率电路18b。其中,开关电路185包含开关s1~s8;高电流放大率电路18a包含晶体管mp5、mp6;以及,低电流放大率电路18b包含晶体管mp3、mp4。根据本发明构想的实施例,晶体管mp3、mp4、mp5、mp6的电流放大率β

mp3

、β

mp4

、β

mp5

、β

mp6

之间,具有以下关系:β

mp6

=β

mp5

>β

mp4

=β

mp3

。

[0133]

在图10中,虚线代表在迟滞模式(mode1)下的连接关系。因开关s1~s4于迟滞模式(mode1)下导通的缘故,开关s1~s4亦以虚线方框标示。另一方面,图10以实线代表在高增益模式(mode2)下的连接关系。因开关s5~s8于高增益模式(mode2)下导通的缘故,开关s5~s8以实线方框标示。

[0134]

请同时参见图6b与图10。在迟滞模式(mode1)下,节点n1经开关s1与晶体管mp5的漏极相连,以及经开关s3与晶体管mp3的栅极相连。另一方面,节点n2经开关s2与晶体管mp6的漏极相连,以及经开关s4与晶体管mp4的栅极相连。

[0135]

请同时参见图7b与图10。在高增益模式(mode2)下,节点n1经开关s6与晶体管mp6的漏极相连,以及经开关s8与晶体管mp4的栅极相连。另一方面,节点n2经开关s5与晶体管mp5的漏极相连,以及经开关s7与晶体管mp3的栅极相连。

[0136]

据此,可进一步归纳,晶体管mp5、mp6的栅极的电连接方式固定,而漏极则根据模式不同而电连接于节点n2、n1中的一者。例如,在迟滞模式(mode1)下,与节点n1相连的晶体管mp5的漏极,将于高增益模式(mode2)下,改为与节点n2相连。又如,在迟滞模式(mode1)下,与节点n2相连的晶体管mp6的漏极,将于高增益模式(mode2)下,改为与节点n1相连。

[0137]

另一方面,晶体管mp3、mp4的漏极的电连接方式固定,而栅极则根据模式不同而电连接于节点n2、n1中的一者。例如,在迟滞模式(mode1)下,与节点n1相连的晶体管mp3的栅极,将于高增益模式(mode2)下,改为与节点n2相连。又如,在迟滞模式(mode1)下,与节点n2

相连的晶体管mp4的栅极,将于高增益模式(mode2)下,改为与节点n1相连。

[0138]

如图3所示,耦合模块18的一部分属于第一级放大器15,另一部分属于第二级放大器17。另,根据图10所示,耦合模块18包含开关电路185、高电流放大率电路18a与低电流放大率电路18b。在本文中,耦合模块18内的元件(开关s1~s8、晶体管mp3~mp6)与第一级放大器15和第二级放大器17之间的对应关系并非固定,而会随着比较电路13所处的操作模式而改变。接着,本文以图11说明在耦合模块18中的元件(开关s1~s8、晶体管mp3~mp6),与第一级放大器15和第二级放大器17之间的对应关系。

[0139]

请参见图11,其是依据比较电路所处的模式不同,动态地调整耦合模块内的晶体管的示意图。图11的上方为耦合模块18在迟滞模式(mode1)下的晶体管配置方式,其中晶体管mp3~mp6的排列方式,相当于图7a、图7b中,经简化后的晶体管的连线关系的相对位置。图11的下方为耦合模块18在高增益模式(mode2)下的晶体管配置。其中晶体管mp3~mp6的排列方式,相当于图8中,经简化后的晶体管的连线关系的相对位置。

[0140]

表6汇整高电流放大率电路18a与低电流放大率电路18b如何因应比较电路13的模式不同,使晶体管以彼此跨接方式耦合,或与晶体管mp1、mp2形成外接电流镜的情形。

[0141]

表6

[0142][0143]

在迟滞模式(mode1)下,高电流放大率电路18a中的晶体管mp5、mp6以跨接方式相连。在此同时,低电流放大率电路18b中的晶体管mp3、mp4分别与晶体管mp1、mp2形成外接电流镜21a、21b。因此,在迟滞模式(mode1)中,高电流放大率电路18a属于第一级放大器15,低电流放大率电路18b属于第二级放大器17。

[0144]

在高增益模式(mode2)下,低电流放大率电路18b中的晶体管mp3、mp4以跨接方式相连。在此同时,高电流放大率电路18a中的晶体管mp5、mp6分别与晶体管mp2、mp1形成外接电流镜22b、22a。因此,在高增益模式(mode2)中,低电流放大率电路18b属于第一级放大器15,高电流放大率电路18a属于第二级放大器17。

[0145]

由前述说明可以得知,本公开的比较电路13具有对称的电路结构。因此,对电路布局而言,采用本公开架构的比较电路13可减少不匹配的情况。连带的,本公开实施例的比较电路13的架构可在维持相同功耗与面积的同时,兼顾并提高迟滞与增益的效果。

[0146]

综上所述,本公开于比较电路中设置开关电路。开关电路可以根据比较电路所处的模式不同动态改变晶体管的连接方式。由于开关电路可因应模式的不同改变晶体管的连接关系,比较电路可根据模式的不同,选用相对适当方式设定第一级放大器与第二级放大

器的配置。

[0147]

本发明的比较电路在迟滞模式(mode1)下,迟滞电压vhys仅与晶体管mn1、mn2、mp3、mp6的尺寸,以及与流经晶体管mn1的电流i

mn1

、流经晶体管mn2的电流i

mn2

相关,并不会受到参考电压vref的大小所影响。此外,本发明的比较电路在高增益模式(mode2)下,可提供较高的增益。

[0148]

综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中的技术人员,在不脱离本发明的精神和范围内,当可作各种的变动与润饰。因此,本发明的保护范围当视后附的权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1