具有休眠模式的发光二极管模组及发光二极管灯串的制作方法

1.本发明有关一种发光二极体模组及发光二极体灯串,尤指一种具有休眠模式之的发光二极体模组及发光二极体灯串。

背景技术:

2.由于发光二极管(light-emitting diode, led)具有发光效率高、低耗电量、寿命长、响应速度快、可靠度高等的优点,因此,发光二极管已广泛地以灯条(light bar)或灯串(light string)的串联、并联或串并联的连接方式,应用于照明用灯具或装饰用发光,例如圣诞树灯饰、运动鞋发光特效等。

3.以节庆灯饰为例,完整的发光二极管灯串基本上包含多个发光二极管模组(内部通常具有多个灯)与驱动发光二极管模组的控制模组。控制模组与发光二极管模组电性连接,并且通过对该灯提供所需电力以及具有发光命令的发光驱动信号,以点控的方式或者同步的方式控制,实现发光二极管灯具多样化的灯光输出效果与变化。

4.随着技术的进步,具有发光命令的发光驱动信号可通过载波的方式,将发光驱动信号搭载于电力线上,可实现以相同的电路架构提供电力与资料传输的功能,以简化布线设计、缩小电路体积,且有利于控制线路的设计。但是由于发光二极管模组中的模拟电路处于工作时的电力消耗较大,导致无法降低发光二极管灯串整体的电力消耗,又由于此载波技术需要第二电压当做信号电压。

5.因此,如何设计出一种具有休眠模式的发光二极管模组及发光二极管灯串,利用省去外部信号电压的最精简线路及降低耗电来达到电力线上载波并传输信号的方式,且在发光二极管模组不需要工作时关断,以节省发光二极管模组及发光二极管灯串整体的耗电量,乃为本案创作人所欲行研究的一大课题。

技术实现要素:

6.为了解决上述问题,本发明提供一种具有休眠模式的发光二极管模组,以克服现有技术的问题。因此,本发明具有休眠模式的发光二极管模组,包括:侦测电路,通过电源线接收发光驱动信号。驱动电路,接收发光驱动信号,且耦接侦测电路,驱动电路包括:控制单元,耦接侦测电路。及至少一发光二极管,耦接控制单元。其中,控制单元根据发光驱动信号获得并储存发光命令,且根据发光命令控制发光二极管的发光行为;在驱动电路通过侦测电路所提供的第一侦测信号得知发光驱动信号下降至小于第一阈值,驱动电路进行发光驱动信号的信号辨识,且在发光驱动信号已完成信号辨识时,驱动电路由工作模式进入休眠模式;在发光驱动信号下降至小于第二阈值时,驱动电路降低发光驱动信号的放电速度。

7.于一实施例中,在驱动电路通过第二侦测信号得知发光驱动信号上升至大于等于第二阈值,驱动电路由休眠模式返回至工作模式。

8.于一实施例中,侦测电路包括:分压电路,接收发光驱动信号。第一比较器,接收第一参考电压,且耦接分压电路。及第二比较器,接收第二参考电压,且耦接分压电路。其中,

第一比较器根据第一参考电压与对应发光驱动信号的分压值而提供第一侦测信号,且第二比较器根据第二参考电压与对应发光驱动信号的分压值而提供第二侦测信号。

9.于一实施例中,侦测电路包括:第一电阻,一端接收发光驱动信号,另一端接收第一参考电压。第一开关,包括输入端、输出端及控制端,输入端接收发光驱动信号,控制端耦接第一电阻的另一端。及分压电路,耦接第一开关的输出端与控制单元。其中,分压电路将第一开关的输出端的电压分压而提供第一侦测信号与第二侦测信号。

10.于一实施例中,驱动电路还包括:振荡器,接收发光驱动信号,且耦接控制单元。其中,在工作模式时,振荡器根据发光驱动信号提供时脉信号至控制单元;在休眠模式时,控制单元所提供的休眠信号关断振荡器,使振荡器不提供时脉信号至控制单元,同时也关闭模拟线路。

11.于一实施例中,振荡器包括:第一反相器,包括输入端、输出端及电源端,输入端耦接第二电阻的一端与第一电容的一端,输出端耦接第二电阻的另一端,且电源端接收发光驱动信号与休眠信号。及第二反向器,包括输入端、输出端及电源端,输入端耦接第一反相器与第二电阻的另一端,输出端耦接第一电容的另一端与控制单元,且电源端接收发光驱动信号与休眠信号。

12.于一实施例中,驱动电路包括:锁存电路,接收发光驱动信号与第一侦测信号。其中,在锁存电路根据第一侦测信号得知发光驱动信号小于第一阈值的时间大于等于持续时间时,锁存电路所提供的锁存信号使得控制单元将经辨识后的发光驱动信号储存为发光命令。

13.于一实施例中,控制单元包括:逻辑电路,耦接侦测电路。及暂存器,耦接逻辑电路。其中锁存电路由逻辑闸构成,且整合于逻辑电路中;在发光驱动信号小于第一阈值的时间大于等于持续时间时,逻辑闸所提供的锁存信号使得逻辑电路通知暂存器将经辨识后的发光驱动信号储存为发光命令。

14.于一实施例中,锁存电路包括:第二开关,包括输入端、输出端及控制端,输出端耦接电源线与第二电容的一端,输入端耦接第二电容的另一端、第三电阻的一端及控制单元,且控制端接收第一侦测信号。及第三开关,包括输入端、输出端及控制端,输入端耦接第二电阻的另一端,输出端耦接接地点,且控制端接收第一侦测信号。

15.于一实施例中,锁存电路包括:第二开关,包括输入端、输出端及控制端,输出端耦接电源线,输入端耦接第三电阻的一端,且控制端接收第一侦测信号。及第三开关,包括输入端、输出端及控制端,输入端耦接第二电阻的另一端、第二电容的一端及控制单元,输出端耦接第二电容的另一端与接地点,且控制端接收第一侦测信号。

16.于一实施例中,驱动电路包括:放电电路,接收第二侦测信号,且耦接电源线。其中,放电电路通过第二侦测信号得知发光驱动信号小于第二阈值时,放电电路降低发光驱动信号的放电速度。

17.于一实施例中,放电电路包括:放电开关,包括输入端、输出端及控制端,输入端耦接电源线,输出端耦接接地点,且控制端接收第二侦测信号。

18.为了解决上述问题,本发明提供一种具有休眠模式的发光二极管灯串,以克服现有技术的问题。因此,本发明具有休眠模式的发光二极管灯串,包括:电源线,接收直流工作电压。及控制模组,耦接电源线,且包括:功率开关,耦接该电源线。及控制器,耦接功率开

关。及至少一发光二极管模组,至少一发光二极管模组通过电源线耦接控制模组,且通过电源线接收控制模组传递的发光驱动信号与直流工作电压;其中,控制器控制功率开关导通时,直流工作电压通过电源线形成对至少一发光二极管模组供电的供电回路;当控制器欲产生属于至少一发光二极管模组中的发光二极管模组的发光驱动信号时,控制器根据发光命令持续切换功率开关的导通与截止,使电源线的直流工作电压形成多个脉波以组合成发光驱动信号,且通过电源线传送至发光二极管模组。

19.本发明的主要目的及功效在于,在驱动电路处于休眠模式时,驱动电路不工作(即主要关断振荡器以及由振荡器所提供的时脉信号所控制的电路及模拟线路,以关断驱动电路主要的耗电元件),进而达到节省发光二极管模组耗电量的功效。

附图说明

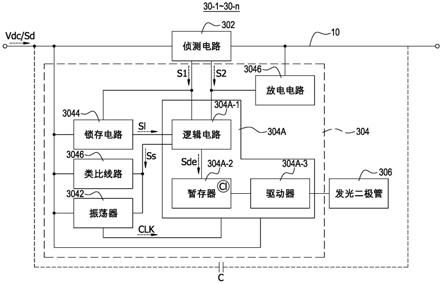

20.图1a为本发明具有休眠模式的发光二极管灯串第一实施例的电路方块图;图1b为本发明具有休眠模式的发光二极管灯串第二实施例的电路方块图;图1c为本发明发光驱动信号的波形示意图;图2a为本发明具有休眠模式的发光二极管模组的电路方块图;图2b为本发明发光驱动信号的其中之一脉波波形示意图;图2c为本发明逻辑电路启动休眠模式的逻辑示意图;图3a为本发明侦测电路第一实施例的电路示意图;图3b为本发明侦测电路第二实施例的电路示意图;图4为本发明振荡器的电路示意图;图5a为本发明锁存电路第一实施例的电路示意图;图5b为本发明锁存电路第二实施例的电路示意图;图5c为本发明锁存电路第三实施例的电路示意图;及图6为本发明放电电路的电路示意图。

21.符号说明:100、100

’…

发光二极管灯串;10

…

电源线;20

…

控制模组;sw

…

功率开关;202

…

控制器;30-1~30-n

…

发光二极管模组;302、302

’…

侦测电路;302a

…

分压电路;ra、rb

…

分压电阻;302b

…

第一比较器;302c

…

第二比较器;(+)

…

第一输入端;(-)

…

第二输入端;o

…

输出端;

r1

…

第一电阻;q1

…

第一开关;304

…

驱动电路;3042

…

振荡器;in1

…

第一反相器;in2

…

第二反相器;r2

…

第二电阻;c1

…

第一电容;3044、3044’、 3044

’’…

锁存电路;q2

…

第二开关;q3

…

第三开关;c2

…

第二电容;r3

…

第三电阻;3046

…

放电电路;q4

…

放电开关;r4

…

第四电阻;304a

…

控制单元;304a-1

…

逻辑电路;and

…

及闸;304a-2

…

暂存器;304a-3

…

驱动器;b

…

缓冲闸;306

…

发光二极管;c

…

储能电容;40

…

整流器;x

…

输入端;y

…

输出端;z

…

控制端;p

…

电源端;vac

…

输入电源;vdc

…

直流工作电压;vm

…

最低工作电压;vref1

…

第一参考电压;vref2

…

第二参考电压;sd

…

发光驱动信号;sde

…

经辨识后的发光驱动信号;pu

…

脉波;ssw

…

开关信号;s1

…

第一侦测信号;

s2

…

第二侦测信号;clk

…

时脉信号;ss

…

休眠信号;sl

…

锁存信号;se

…

完成信号;cl

…

发光命令;clo

…

外部发光命令;v1

…

第一阈值;v2

…

第二阈值;th

…

持续时间;t0~t4

…

时间;a

…

节点。

具体实施方式

22.下面结合附图和具体实施例对本发明作进一步说明,以使本领域的技术人员可以更好的理解本发明并能予以实施,但所举实施例不作为对本发明的限定。

23.有关本发明的技术内容及详细说明,配合图式说明如下:请参阅图1a为本发明具有休眠模式的发光二极管灯串第一实施例的电路方块图。发光二极管灯串100包括电源线10、控制模组20、至少一发光二极管模组30-1~30-n及整流器40,整流器40耦接电源线10,且接收输入电源vac,以将输入电源vac整流为直流工作电压vdc。控制模组20接收直流工作电压vdc,且控制至少一发光二极管模组30-1~30-n的发光行为。其中,发光行为例如但不限于色彩变化、亮灭(暗)方式、亮灭频率

…

等等的行为。控制模组20耦接电源线10,且通过电源线10耦接发光二极管模组30-1~30-n。发光二极管模组30-1~30-n以串联或并联的方式耦接(本实施例以串联的方式示意),且通过电源线10接收由控制模组20传递的发光驱动信号sd与直流工作电压vdc。其中,直流工作电压vdc可由前级加装直流转换器(图未示)而获得,或者直流工作电压vdc可通过发光二极管灯串100安装蓄电池而获得。

24.具体而言,控制模组20包括功率开关sw与控制器202,功率开关sw的输入端x与输出端y耦接电源线10,且功率开关sw的控制端z耦接控制器202。控制器202通过电源线10接收直流工作电压vdc,且提供开关信号ssw控制功率开关sw的导通与截止。控制器202控制功率开关sw导通时,直流工作电压vdc通过电源线10形成对发光二极管模组30-1~30-n供电的供电回路。当控制器202欲产生属于发光二极管模组30-1~30-n中的某个发光二极管模组30-1(假设为第一个发光二极管模组) 的发光驱动信号sd时,控制器根据属于发光二极管模组30-1的发光命令持续切换功率开关sw的导通与截止,使电源线10上的直流工作电压vdc形成多个脉波以组合成属于发光二极管模组30-1发光驱动信号sd,且通过电源线10传送至发光二极管模组30-1。

25.控制器202可通过有线(wired)或无线(wireless)的方式,除本身已内置的发光命令亦可从外部接收外部发光命令clo,使得控制器202可根据发光命令或外部发光命令clo的内容控制功率开关sw的导通与截止而产生发光驱动信号sd,以通过发光驱动信号sd对发

光二极管模组30-1~30-n进行发光控制。举例来说,使用者可通过操作电脑的方式,以有线的方式将外部发光命令clo传送至控制器202,使控制器202根据外部发光命令clo进行发光控制。或者,使用者可通过操作手机或穿戴式装置的方式,以无线的方式将外部发光命令clo传送至控制器202,使控制器202根据外部发光命令clo进行发光控制。然不以上述传送外部发光命令clo的方式以及操作的使用者装置限制本发明。

26.以控制器202欲根据传输属于发光二极管模组30-1的发光命令而对应地传输属于发光二极管模组30-1的发光驱动信号sd为例,控制器202可通过控制功率开关sw切换而产生命令传输的通知信号。发光二极管模组30-1~30-n收到此通知信号时,即进行命令接收的阶段。然后,控制器202通过控制功率开关sw的导通与截止而将属于发光二极管模组30-1的发光命令转换为发光驱动信号sd。其发光驱动信号sd的脉波可以以”0”和”1”形式的地址资料加上led灯的亮度”11”、颜色”10”构成发光驱动信号sd。发光驱动信号sd例如但不限于包括10个脉波,且地址资料对应第一个发光二极管模组30-1的地址。发光二极管模组30-1~30-n收到地址资料时,发光二极管模组30-1即得知接续传递的发光驱动信号sd属于自我的发光驱动信号sd,以将此发光驱动信号sd进行信号辨识。待9个脉波辨识完成后,控制器202通过控制功率开关sw切换而产生命令传输完成的通知信号(即最后一个脉波),发光二极管模组30-1即根据此通知信号产生锁存信号而将9个脉波所对应的发光命令储存,且根据所储存的发光命令产生发光行为。值得一提,发光二极管模组30-1具有多种的的控制方式,但其精神大致上同于上述的控制方式,且发光二极管模组30-2~30-n的控制方式亦同于发光二极管模组30-1,在此不再加以赘述。

27.请参阅图1b为本发明具有休眠模式的发光二极管灯串第二实施例的电路方块图,复配合参阅图1a。本实施例的发光二极管灯串100’与图1a的发光二极管灯串100差异在于,发光二极管灯串100’并未包括整流器40,且发光二极管模组30-1~30-n以并联的方式耦接。发光二极管灯串100的控制模组20接收由外部提供的直流工作电压vdc,且控制至少一发光二极管模组30-1~30-n的发光行为。值得一提,于本发明的一实施例中,发光二极管灯串100’未提及的元件、元件的耦接关系及控制方式同于图1a,在此不再加以赘述。

28.请参阅图1c为本发明发光驱动信号的波形示意图,复配合参阅图1a~图1b。本实施例的发光驱动信号sd以10个周期的脉波示意,在控制器202控制功率开关sw导通时,直流工作电压vdc通过电源线10形成对发光二极管模组30-1~30-n供电的供电回路。当控制器202欲产生发光驱动信号sd时,控制器根据发光命令持续切换功率开关sw的导通与截止,使电源线10上的直流工作电压vdc因切换而形成10个周期的脉波pu组合成的发光驱动信号sd,且通过电源线10传送至发光二极管模组30-1。其中,最后一个脉波pu在低准位的时间较长,当发光二极管模组30-1侦测到脉波pu在低准位的时间较长时,此脉波pu即为命令传输完成的通知信号。即最后一个脉波pu在低准位的时间超过了前9个脉波在低准位时的持续时间th。此时,发光二极管模组30-1~30-n即根据此通知信号产生锁存信号而将9个脉波pu所对应的发光命令储存,且根据所储存的发光命令产生发光行为。

29.请参阅图2a为本发明具有休眠模式的发光二极管模组的电路方块图、图2b为本发明发光驱动信号的其中之一脉波波形示意图,复配合参阅图1a~图1b,且反复参阅图2a、图2b。每个发光二极管模组30-1~30-n均包括侦测电路302、驱动电路304及至少一发光二极管306(本实施例以三个发光二极管306做为示意性的范例),且驱动电路304耦接侦测电路302

与发光二极管306。侦测电路302通过电源线10接收直流工作电压vdc或发光驱动信号sd,且根据发光驱动信号sd而提供第一侦测信号s1与第二侦测信号s2至驱动电路304。驱动电路304通过电源线10接收直流工作电压vdc或发光驱动信号sd,在驱动电路304接收直流工作电压vdc时,驱动电路304运作在工作模式。此时,驱动电路304内的控制单元304a根据发光命令cl控制发光二极管306的发光行为,发光命令cl通过控制器202先前提供的发光驱动信号sd而获得。于本发明的一实施例中,发光二极管模组30-1~30-n中的侦测电路302、驱动电路304可为封装在一起的控制器,但不以此为限。换言之,可依照实际需求将整个发光二极管模组30-1~30-n封装在一起,或发光二极管模组30-1~30-n内部的元件可独立设置。

30.在驱动电路304接收发光驱动信号sd时,驱动电路304根据第一侦测信号s1与第二侦测信号s2调整运作的模式。具体而言,如图2b所示,功率开关sw在时间t0时关断,使得发光驱动信号sd开始下降。在驱动电路304通过第一侦测信号s1得知发光驱动信号sd下降至小于第一阈值v1时(时间t1),驱动电路304进行发光驱动信号sd的信号辨识。此时,驱动电路304仍然运作在工作模式,且发光驱动信号sd的信号辨识在时间t2时完成。在发光驱动信号sd完成后(及时间t2之后),驱动电路304由工作模式进入休眠模式。在驱动电路304通过第二侦测信号s2得知发光驱动信号sd下降至小于第二阈值v2时(时间t3),驱动电路304降低该发光驱动信号sd的放电速度(意即,电压下降的斜率改变)。最后,在时间t4时,脉波的电压由小于第二阈值v2上升至大于第一阈值v1,使得驱动电路304由休眠模式返回至工作模式。此时,驱动电路304被唤醒而进入工作模式。因此可以得知,在发光驱动信号sd辨识完成至脉波的电压由小于第二阈值v2上升至大于第一阈值v1时,驱动电路304即处于休眠模式,除此之外驱动电路304均处于工作模式。

31.进一步而言,如图2a所示,驱动电路304包括振荡器3042、锁存电路3044、放电电路3046及控制单元304a,且控制单元304a包括逻辑电路304a-1、暂存器304a-2及驱动器304a-3。在驱动电路304处于工作模式时,上述的元件均通过接收直流工作电压vdc或发光驱动信号sd而运作。由于振荡器3042所产生的时脉信号clk与控制单元304a的运作息息相关,且振荡器3042又是驱动电路304处于工作模式时主要的耗电元件,因此本发明的主要目的及功效在于,在驱动电路304处于休眠模式时,驱动电路304不工作(即主要关断振荡器3042,以关断驱动电路304主要的耗电元件)及模拟线路。且由于振荡器3042的关断,使得控制单元304a中部分通过时脉信号clk所运作的电路(例如但不限于驱动器304a-3,逻辑电路304a-1与暂存器304a-2的部分线路)同时被关断,以达到节省发光二极管模组30-1~30-n耗电量。值得一提,由于锁存电路3044的运作并未使用时脉信号clk,因此在振荡器3042被关断时,锁存电路3044仍然可在休眠模式时根据第一侦测信号s1提供锁存信号sl。此外,逻辑电路304a-1乃为数字被动元件,因此即便在驱动电路304处于休眠模式时,只要发光驱动信号sd脉波的电压由小于第二阈值v2上升至大于第一阈值v1而使得第二侦测信号s2产生变化时,被动的逻辑电路304a-1仍然可通过信号的输出而唤醒驱动电路304内的所有元件。

32.复参阅图2a,控制单元304a接收直流工作电压vdc或发光驱动信号sd作为运作时所需的电源。逻辑电路304a-1耦接侦测电路302,且根据第一侦测信号s1进行发光驱动信号sd的信号辨识,以及根据第二侦测信号s2提供休眠信号ss至振荡器3042。暂存器304a-2耦接逻辑电路304a-1,且在逻辑电路304a-1收到锁存信号sl时,逻辑电路304a-1将经辨识后的发光驱动信号sde提供至暂存器304a-2,使暂存器304a-2将其储存为发光命令cl。驱动器

304a-3耦接暂存器304a-2与发光二极管306,且暂存器304a-2根据发光命令cl控制驱动器304a-3驱动发光二极管306,使发光二极管306产生发光行为。值得一提,本发明的控制单元304a将发光驱动信号sd中的多个脉波一次性地提供至暂存器304a-2储存,使得暂存器304a-2可一次性地储存完整的发光命令cl,而并非收到一次脉波即根据单一脉波调整发光二极管306的发光行为,以避免发光命令cl容易错误而使发光二极管306产生错误的发光行为的状况。

33.振荡器3042接收直流工作电压vdc或发光驱动信号sd,且耦接控制单元304a与控制单元304a中的逻辑电路304a-1。在工作模式时,振荡器3042根据直流工作电压vdc或发光驱动信号sd提供时脉信号clk至控制单元304a,使控制单元304a中,部分需要时脉信号clk的元件(图未示)根据时脉信号clk而运作。在休眠模式时,逻辑电路304a-1根据第二侦测信号s2而提供的休眠信号ss会使得振荡器3042被关断而不再提供时脉信号clk至控制单元304a。借此于休眠模式时,消耗电力较高的振荡器3042与部分通过时脉信号clk而运作的元件停止运作,以节省发光二极管模组30-1~30-n的耗电量。在休眠模式返回工作模式时,第二侦测信号s2会产生变化,使得逻辑电路304a-1根据第二侦测信号s2的变化而调整休眠信号ss,进而通过所提供的休眠信号ss而唤醒振荡器3042。值得一提,于本发明的一实施例中,在休眠模式时,逻辑电路304a-1根据第二侦测信号s2而提供的休眠信号ss除了关断振荡器3042之外,同时也可关断驱动电路304中,其他的模拟线路(图未示),待由休眠模式回到工作模式时,再启动其他的模拟线路(图未示)。例如但不限于,休眠信号ss可控制部分的信号侦测电路、保护电路等休眠或工作。借此,可更为节省发光二极管模组30-1~30-n耗电量。

34.锁存电路3044接收直流工作电压vdc或发光驱动信号sd,且根据第一侦测信号s1而提供锁存信号sl至逻辑电路304a-1。具体而言,锁存电路3044利用时间的长短控制所提供的锁存信号sl。在发光驱动信号sd中的脉波宽度过短时,锁存电路3044所提供锁存信号sl会使得逻辑电路304a-1不会将发光命令cl提供至暂存器304a-2。在发光驱动信号sd中的脉波宽度够长时,代表发光驱动信号sd小于第一阈值v1的时间大于等于持续时间。此时,锁存电路3044所提供的锁存信号sl会使得逻辑电路304a-1根据锁存信号sl通知暂存器304a-2将经辨识后的发光驱动信号sde提供至暂存器304a-2储存为发光命令cl。

35.放电电路3046耦接侦测电路302与电源线10,且根据第二侦测信号s2得知发光驱动信号sd小于第二阈值v2时,放电电路3046降低发光驱动信号sd的放电速度。具体而言,由于某些控制单元304a不具有断电记忆的功能。意即,直流工作电压vdc或发光驱动信号sd的电压值过低后,控制单元304a内部记忆的资料被清除(例如但不限于发光命令cl),因此发光驱动信号sd在低准位时的电压值必须要保持在最低工作电压vm以上(如图2b所示),以避免控制单元304a因电压过低而重置(reset)。其中,放电电路3046最主要为尽可能地将发光驱动信号sd的放电速度降到最低,以不至于使发光驱动信号sd的电压值下降过快,进而较容易地撑过最后一个脉波pu在低准位的时间(因为最后一个脉波pu在低准位的时间较长)。本发明利用放电电路3046在发光驱动信号sd小于第二阈值v2时降低发光驱动信号sd的放电速度,可避免上述发光驱动信号sd放电过快而使电压值低于最低工作电压vm的功效。

36.发光二极管模组30-1~30-n还包括模拟线路3046,模拟线路3046接收直流工作电压vdc或发光驱动信号sd作为电力来源,且耦接控制单元304a。发光二极管模组30-1~30-n

为具有烧录功能的灯串,因此各发光二极管模组30-1~30-n具有各自对发光资料、地址资料进行烧录处理的数字与模拟线路,例如负责发光控制的发光控制单元、负责地址信号处理的地址信号处理单元以及负责地址烧录的地址烧录单元(图未示)。在休眠模式时,控制单元304a所提供的休眠信号ss除了关断振荡器3042外,同时也关断模拟线路3046,以节省发光二极管模组30-1~30-n耗电量。

37.发光二极管模组30-1~30-n还包括储能电容c,储能电容c耦接发光二极管模组30-1~30-n的输入端与输出端之间,且用以在直流工作电压vdc或发光驱动信号sd由发光二极管模组30-1~30-n的输入端传递至输出端(通过电源线10)时,稳定发光二极管模组30-1~30-n两端(即输入端与输出端)的电压,以降低发光二极管模组30-1~30-n因两端的电压浮动而造成发光二极管模组30-1~30-n控制错误的不稳定性。值得一提,于本发明的一实施例中,储能电容c仅为稳定发光二极管模组30-1~30-n两端的电压之用,其非为发光二极管模组30-1~30-n的必要元件,因此以虚线表示。

38.请参阅图2c为本发明逻辑电路启动休眠模式的逻辑示意图,复配合参阅图1a~图2b。逻辑电路304a-1例如但不限于,可通过简单的逻辑闸启动驱动电路304的休眠模式。如图2c所示,及闸and的一输入端接收发光驱动信号sd的信号辨识完的完成信号se,其辨识完成与否,可通过逻辑电路304a-1根据第一侦测信号s1的输入而自行操作获得。及闸and的另一输入端接收第二侦测信号s2,且在完成信号se与第二侦测信号s2均为1的时候,及闸and提供1的休眠信号ss至振荡器3042,使振荡器3042被关断。当及闸and的其中之一输入端不为1的时候,及闸and提供0的休眠信号ss至振荡器3042,使振荡器3042被唤醒。

39.请参阅图3a为本发明侦测电路第一实施例的电路示意图,复配合参阅图1a~图2b。侦测电路302包括分压电路302a、第一比较器302b及第二比较器302c,且分压电路包括分压电阻ra、rb。其中,电路连接方式仅为示意之用,非以限制本发明,只要能够根据发光驱动信号sd的变化而提供第一侦测信号s1与第二侦测信号s2的侦测电路302,均应包含于本发明的范畴中。分压电阻ra的一端接收直流工作电压vdc或发光驱动信号sd,分压电阻ra的另一端耦接分压电阻rb的一端,且分压电阻rb的另一端耦接接地点。第一比较器302b与第二比较器302c分别包括第一输入端(+)、第二输入端(-)及输出端o,且第一比较器302b与第二比较器302c的第一输入端(+)耦接分压电阻ra与rb之间。第一比较器302b的第二输入端(-)耦接第一参考电压vref1,且第二比较器302c的第二输入端(-)耦接第二参考电压vref2。直流工作电压vdc或发光驱动信号sd通过分压电阻ra、rb分压后,于分压电阻ra、rb之间的节点a产生分压值。第一比较器302b根据第一参考电压vref1与对应发光驱动信号sd的分压值而于第一比较器302b的输出端o提供第一侦测信号s1,且第二比较器302c根据第二参考电压vref2与对应发光驱动信号sd的分压值而于第二比较器302c的输出端o提供第二侦测信号s2。其中,第一参考电压vref1的电压值大于第二参考电压vref2的电压值。

40.当发光驱动信号sd的电压值大于第一参考电压vref1与第二参考电压vref2时,第一比较器302b与第二比较器302c为高准位输出,使得驱动电路304处于工作模式。当发光驱动信号sd的电压值介于第一参考电压vref1与第二参考电压vref2之间时,第一比较器302b为低准位输出,且第二比较器302c为高准位输出。此时,驱动电路304进行发光驱动信号sd的信号辨识。当发光驱动信号sd辨识完成后(发光驱动信号sd的电压值介于第一参考电压vref1与第二参考电压vref2之间),驱动电路304由工作模式进入休眠模式。当发光驱动信

号sd的电压值小于第一参考电压vref1与第二参考电压vref2时,第一比较器302b与第二比较器302c为低准位输出,使得驱动电路304降低发光驱动信号sd的放电速度。值得一提,由于直流工作电压vdc为固定的电压值,使得经第一比较器302b比较后的第一侦测信号s1也为固定值。意即,仅有具有脉波变化的发光驱动信号sd会使得第一比较器302b所比较出的结果产生变化,第二比较器302c同理。

41.请参阅图3b为本发明侦测电路第二实施例的电路示意图,复配合参阅图1a~3a。本实施例的侦测电路302’与图3a的侦测电路302差异在于,侦测电路302’包括第一电阻r1、第一开关q1及分压电路302a,且分压电路302a包括分压电阻ra、rb。其中,电路连接方式仅为示意之用,非以限制本发明,只要能够根据发光驱动信号sd的变化而提供第一侦测信号s1与第二侦测信号s2的侦测电路302,均应包含于本发明的范畴中。第一电阻r1的一端接收直流工作电压vdc或发光驱动信号sd,且第一电阻r1的另一端接收第一参考电压vref1。第一开关q1包括输入端x、输出端y及控制端z,第一开关q1的输入端x接收直流工作电压vdc或发光驱动信号sd,控制端z耦接第一电阻r1的另一端。分压电阻ra的一端接耦接第一开关q1的输出端y,分压电阻ra的另一端耦接分压电阻rb的一端,且分压电阻rb的另一端耦接接地点。分压电阻ra与第一开关q1的输出端y之间的节点提供第一侦测信号s1,且分压电阻ra、rb之间的节点提供第二侦测信号s2。

42.当发光驱动信号sd的电压值大于第一参考电压vref1时,第一开关q1导通,第一侦测信号s1与第二侦测信号s2输出为高准位,使得驱动电路304处于工作模式。当发光驱动信号sd的电压值小于第一参考电压vref1时,第一开关q1导通,第一侦测信号s1输出为低准位,且第二侦测信号s2输出为高准位。此时,驱动电路304进行发光驱动信号sd的信号辨识。当发光驱动信号sd辨识完成后(发光驱动信号sd的电压值小于第一参考电压vref1至第一开关q1关断之间),驱动电路304由工作模式进入休眠模式。当发光驱动信号sd的电压值过低时,第一开关q1关断,第一侦测信号s1与第二侦测信号s2输出为低准位,使得驱动电路304降低发光驱动信号sd。值得一提,由于在数字的电路中,模拟转数字的信号需要使用缓冲闸来增加信号强度,因此在第一侦测信号s1与第二侦测信号s2输出的路径上可加装缓冲闸b,以提升第一侦测信号s1与第二侦测信号s2的信号强度。

43.请参阅图4为本发明振荡器的电路示意图,复配合参阅图1a~图3b。振荡器3042包括第一反相器in1、第二反相器in2、第二电阻r2及第一电容c1,其电路连接方式仅为示意之用,非以限制本发明,只要能够产生时脉信号clk的振荡器3042,均应包含于本发明的范畴中。其中,第一反相器in1,包括输入端x、输出端y及电源端p,输入端x耦接第二电阻r2的一端与第一电容c1的一端,输出端y耦接第二电阻r2的另一端,且电源端p接收发光驱动信号sd与休眠信号ss。第二反向器in2包括输入端x、输出端y及电源端p,输入端x耦接第一反相器in1与第二电阻r2的另一端,输出端y耦接第一电容c1的另一端与控制单元304a,且电源端p接收发光驱动信号sd与休眠信号ss。第一反相器in1与第二反相器in2为cmos电晶体电路反相器,可通过设计不同的电晶体尺寸,并且通过致能与禁能的控制,实现准确控制与低耗电的需求。

44.当在工作模式时,休眠信号ss使得振荡器3042中的第一反相器in1与第二反相器in2均为致能状态(如图2b,时间t3之前或t4之后),因此,振荡器3042能够以全功率的运作,提供时脉信号clk。当侦测到发光驱动信号sd下降至小于第二阈值v2(如图2b,时间t3~t4),

逻辑电路304a-1所提供的休眠信号ss控制第一反相器in1与第二反相器in2为禁能状态,以完全地关闭振荡器3042而进入休眠模式。然上述反相器的连接方式、数量、尺寸以及控制信号的控制方式仅为示意之用,非以限制本发明。

45.请参阅图5a为本发明锁存电路第一实施例的电路示意图,复配合参阅图1a~图4。锁存电路3044包括第二开关q2、第三开关q3、第二电容c2及第三电阻r3,其电路连接方式仅为示意之用,非以限制本发明,只要能够根据第一侦测信号s1的变化而提供锁存信号sl的锁存电路3044,均应包含于本发明的范畴中。具体而言,第二开关q2包括输入端x、输出端y及控制端z,第二开关q2的输出端y耦接电源线10与第二电容c2的一端,且通过电源线10接收直流工作电压vdc或发光驱动信号sd。第二开关q2的输入端x耦接第二电容c2的另一端、第三电阻r3的一端及逻辑电路304a-1,且第二开关q2的控制端z接收第一侦测信号s1。第三开关q3包括输入端x、输出端y及控制端z,第三开关q3的输入端x耦接第二电阻r2的另一端,第三开关q3的输出端y耦接接地点,且第三开关q3的控制端z接收第一侦测信号s1。

46.在侦测电路302所提供的第一侦测信s1代表发光驱动信号sd大于第一阈值v1时(如图2b,时间t1之前),第二开关q2关断,且第三开关q3导通,使得第二电容c2储能。在发光驱动信号sd由大于第一阈值v1降低至小于第一阈值v1时,第二开关q2导通,且第三开关q3关断,使得第二电容c2开始放电。在发光驱动信号sd小于第一阈值v1的时间大于等于持续时间时,第二电容c2已将内部储存的能量泄放至低于预定值。此时,第二电容c2与第二电阻r2之间节点所提供的锁存信号sl使逻辑电路304a-1通知暂存器304a-2将经辨识后的发光驱动信号sde储存为发光命令cl。值得一提,在锁存信号sl输出的路径上也可加装缓冲闸b,其功效如同图3b所述。

47.请参阅图5b为本发明锁存电路第二实施例的电路示意图,复配合参阅图1a~图5a。本实施例的锁存电路3044’与图5a的锁存电路3044差异在于,第二开关q2、第三开关q3、第二电容c2及第三电阻r3的耦接位置及控制方式。其中,电路连接方式仅为示意之用,非以限制本发明,只要能够根据第一侦测信号s1的变化而提供锁存信号sl的锁存电路3044’,均应包含于本发明的范畴中。具体而言,第二开关q2的输出端y耦接电源线10,且通过电源线10接收直流工作电压vdc或发光驱动信号sd。第二开关q2的输入端x耦接第三电阻r3的一端,且第二开关q2的控制端z接收第一侦测信号s1。第三开关q3的输入端耦接第二电阻r2的另一端、第二电容c2的一端及逻辑电路304a-1,第三开关q3的输出端y耦接第二电容c2的另一端与接地点,且第三开关q3的控制端z接收第一侦测信号s1。

48.在侦测电路302所提供的第一侦测信s1代表发光驱动信号sd大于第一阈值v1时(如图2b,时间t1之前),第二开关q2导通,且第三开关q3关断,使得第二电容c2储能。在发光驱动信号sd由大于第一阈值v1降低至小于第一阈值v1时,第二开关q2关断,且第三开关q3导通,使得第二电容c2开始放电。在发光驱动信号sd小于第一阈值v1的时间大于等于持续时间时,第二电容c2已将内部储存的能量泄放至低于预定值。此时,第二电阻r2与第二电容c2之间节点所提供的锁存信号sl使逻辑电路304a-1通知暂存器304a-2将经辨识后的发光驱动信号sde储存为发光命令cl。值得一提,在锁存信号sl输出的路径上也可加装缓冲闸b,其功效如同图3b所述。

49.请参阅图5c为本发明锁存电路第三实施例的电路示意图,复配合参阅图1a~图5b。本实施例的锁存电路3044

’’

与图5a的锁存电路3044差异在于,锁存电路3044

’’

由逻辑闸所

构成,其可通过及闸、或闸及反向闸等逻辑闸所构成,且整合于逻辑电路304a-1中。在发光驱动信号sd小于第一阈值v1的时间大于等于持续时间时,锁存电路3044

’’

的逻辑闸所提供的锁存信号sl使得逻辑电路304a-1中,及闸and的输出产生变化。逻辑电路304a-1根据此变化通知暂存器304a-2将经辨识后的发光驱动信号sde储存为发光命令cl。值得一提,及闸and的输出可能经过额外的逻辑闸(图未式)判断后(例如但不限于,保护逻辑电路等),方能输出经辨识后的发光驱动信号sde,因此及闸and的输出至经辨识后的发光驱动信号sde之间以虚线表示。

50.请参阅图6为本发明放电电路的电路示意图,复配合参阅图1a~图5c。放电电路3046包括放电开关q4,且放电开关q4输入端x、输出端y及控制端z。放电开关q4的输入端耦接电源线10,放电开关q4的输出端y耦接接地点,且放电开关q4的控制端z接收第二侦测信号s2。其中,电路连接方式仅为示意之用,非以限制本发明,只要能够根据第二侦测信号s2的变化而调整发光驱动信号sd的放电速度均应包含于本发明的范畴中。当发光驱动信号sd大于第二阈值v2时,第二侦测信号s2控制放电开关q4导通,使得发光驱动信号sd对地产生电流路径而快速地放电。当发光驱动信号sd小于第二阈值v2时,第二侦测信号s2控制放电开关q4关断,使发光驱动信号sd浮接(floating),使得发光驱动信号sd通过放电开关q4的关断而降低放电速度。值得一提,为避免放电开关q4导通时,通过放电开关q4流至接地点的电流过大,因此可在发光驱动信号sd至接地点的电流路径上安装第四电阻r4,以限制此电流路径的电流大小。

51.以上所述实施例仅是为充分说明本发明而所举的较佳的实施例,本发明的保护范围不限于此。本技术领域的技术人员在本发明基础上所作的等同替代或变换,均在本发明的保护范围之内。本发明的保护范围以权利要求书为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1