具有用于参考电压调谐的电阻式数模转换器的模数转换器的制作方法

[0001]

本发明通常涉及电路,尤其涉及模数转换器电路以及操作模数转换器的方法。

背景技术:

[0002]

逐次逼近寄存器(successive approximation register;sar)模数转换器(analog-to-digital converter;adc)通常采用电容式数模转换器(capacitive digital-to analog converter;cdac),其中,构成电容器在参考电压与地之间切换,以设置合适的输出电压。尽管理想的cdac输出精确线性的参考电压,但现实世界的cdac受外部因素例如温度影响,因此容易出错。例如,当温度变化时,由该cdac输出的该参考电压可能漂移,因此可能引入增益误差。

[0003]

时间交错adc可包括由n个相同的逐次逼近寄存器(sar)片构成的时分复用并行阵列以增加净采样速率,但该阵列中的每个单独的片实际上以较低的速率采样。各sar片包括缓冲器,例如源极跟随器,其具有一个或多个晶体管,以相对于提供给其输入的稳定参考电压提供电压降。不过,由于例如在这些不同sar片中的晶体管之间的制程变化,输出电压在这些不同sar片之间可能呈现显著的温度变化。结果是温度依赖性,尽管接收相同的参考电压,其可使不同sar片输出不同的电压。

[0004]

目前,这些不同片的电压不能被独立调节和校准。想要这样的独立调节,以提供用于补偿因与制造相关的失配而导致的增益差别的机制。而且,应当在不增加温度变化的情况下实现这些独立调节。

[0005]

因此,需要改进的模数转换器电路以及操作模数转换器的方法。

技术实现要素:

[0006]

在一个实施例中,提供一种模数转换器电路。该电路包括电阻式数模转换器(resistor digital-to-analog converter;rdac),该rdac具有与第一电流源耦接的第一参考节点,与第二电流源耦接的第二参考节点,经配置以接收第一电压的输入端口,以及与缓冲器耦接的输出端口。该rdac经配置以自该第一电压生成包括第一电压偏移的第二电压,并将该第二电压自该rdac的该输出端口供应给该缓冲器。

[0007]

在一个实施例中,提供一种操作模数转换器的方法。该方法包括向电阻式数模转换器(rdac)的输入端口分配第一电压,该rdac经校准以提供电压偏移。该方法还包括通过该rdac自该第一电压生成包括该电压偏移的第二电压,以及将该第二电压自该rdac的输出端口供应给缓冲器。

附图说明

[0008]

包含于并构成本说明书的一部分的附图示例说明本发明的各种实施例,并与上面所作的有关本发明的概括说明以及下面所作的有关所述实施例的详细说明一起用以解释本发明的这些实施例。在所述附图中,类似的附图标记表示不同视图中的类似特征。

[0009]

图1是依据本发明的实施例包括模数转换器的示例接收器电路的电路图。

[0010]

图2是依据本发明的实施例的模数转换器的电压参考电路的电路图。

[0011]

图3是sar片的实施例的电路图。

[0012]

图3a是该sar片的替代实施例的电路图。

[0013]

图4是图3的电阻式数模转换器的实施例的电路图。

[0014]

图5是图3的电容式数模转换器的实施例的电路图。

具体实施方式

[0015]

请参照图1,接收器电路10可包括模数转换器(adc)15,其经配置以采样模拟输入信号并将该模拟输入信号转换为数字输出。adc 15可配置有足够的分辨率,以提供最能代表该模拟输入信号的数字输出。例如,adc 15可经配置以针对每次转换在汇聚于数字输出之前通过多个可能的量化级的二进制搜索将连续模拟波形转换为离散的数字表示。通过时间交错的相同的逐次逼近寄存器(sar)片的过程,adc 15可经配置而以比各单独sar片的操作采样速率更快的速率处理采样数据。为此,adc 15可包括逐次逼近寄存器(sar)18的n个相同的sar片的时分复用并行阵列(time-multiplexed parallel array),以获得较高的净采样速率,尽管该阵列中的各单独sar片实际上以较低的速率采样。该阵列中sar片的数目可为三十二(32)、六十四(64)、一百二十八(128)等。

[0016]

如图1中所示,可提供模拟输入信号作为从信号源至可变增益放大器(variable-gain amplifier;vga)12的输入11。vga 12可以电子可设定电压增益提供信号调节。为避免由sar 18的增益温度变化而导致的问题,接收器电路10可通过基于温度改变vga 12的该电子可设定电压增益来补偿增益温度变化。接收器电路10可将vga 12的输出供应给以连续时间线性均衡器(continuous-time linear equalizer;ctle)14为代表形式的均衡器电路。ctle 14以均衡的形式提供信号调节,从而可恢复自vga 12所接收的信号的各种频率分量之间的平衡。交错器16可采样ctle 14的输出并向sar 18的各该n个sar片提供较低频率样本。交错器16实施时间交错,以允许adc 15通过利用sar 18的该多个片以时序方式以较快的速率处理作为输入11接收的信号。所述信号由sar 18的所述片有效量化并独立处理,且数字电路(未显示)随后将各该n个sar片的b位样本交错为一个b位流,其代表以adc 15的采样速率的b位数字代码。

[0017]

请参照图2-4并依据本发明的实施例,adc 15(图1)可包括全局参考电路20,其具有晶体管26、运算放大器34,以及分压器45。晶体管26可为p型场效应晶体管,其具有与电流源22耦接的源极28、漏极32以及栅极30。晶体管26的栅极30可与晶体管26的漏极32耦接,以使晶体管26为二极管连接。在一个实施例中,电流源22可为恒定电流源,例如1/r带隙电流参考。运算放大器34可具有非反相输入36,其与供应恒定参考电压(v

refglobal

)的恒定参考电压源24耦接。运算放大器34可具有反相输入38,其与晶体管26的源极28耦接。运算放大器34的反馈回路调节晶体管26的栅极电压。分压器45包括耦接于晶体管26的漏极32与地46之间的电阻器44。分压器45还包括与运算放大器34的输出41以及晶体管26的漏极32耦接的电阻器48。全局参考电流20经配置以生成在全局参考电路20的输出40输出的参考电压(v

mid

)。

[0018]

可将全局参考电路20的输出40并行耦接至若干逐次逼近寄存器(sar)片42(例如,sar 18的n个片(图1))的其中每一个。因此,由adc 15的全局参考电路20生成的该参考电压

(v

mid

)被并行分配给adc 15的各sar片42。不过,不提供电压作为从任意sar片42至运算放大器34的任意一个输入36、38的反馈。

[0019]

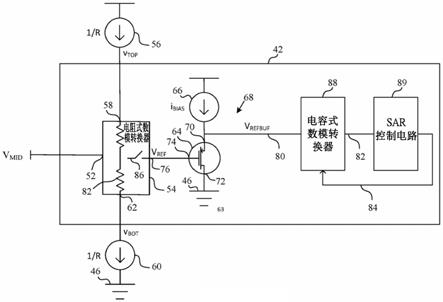

各sar片42可包括电阻式数模转换器(rdac)54以及与rdac 54耦接的缓冲器68。rdac 54包括分别具有固定电阻值并以网络设置的多个电阻器82,以及经控制以改变rdac 54的电阻值的多个开关86。在一个实施例中,电阻器82可具有名义上相等的电阻值。各sar片42的rdac 54具有中心抽头或输入端口52,其代表sar片42的输入。输入端口52与全局参考电路20的输出40耦接,且各sar片42在输入端口52接收来自全局参考电路20的输出40的该参考电压(v

mid

)。rdac 54在输入端口52可为中心抽头,以使在该电阻器串的上半部分中的设置于输入端口52与参考节点58之间的电阻器82的数目名义上等于在该电阻器串的下半部分中的设置于输入端口52与参考节点62之间的电阻器82的数目。电流源56可与各sar片42的rdac 54的参考节点58耦接,且另一个电流源60可与各sar片42的rdac 54的参考节点62耦接。电阻器82生成欧姆(ir)电压降,以使电流源56将该电阻器串的上半部分驱动至电压(v

top

)且电流源60将该电阻器串的下半部分驱动至电压(v

bot

)。在一个实施例中,电流源60可为电流源56的等同物,以使可忽略不计的且理想情况下为零的电流从sar片42流入输入端口52中。在一个实施例中,电流源56与60可为恒定电流源,例如1/r带隙电流参考源,以使各电阻器82上的电压降稳定且恒定。在一个实施例中,电流源56及60可由所有sar片42共用,在此情况下,与电流源56及60的连接是所有sar片42之间的共用节点,类似于sar片42与全局参考电路20之间的连接。

[0020]

从全局参考电路20向各sar片42提供的该参考电压(v

mid

)在被作为参考电压(v

ref

)供应给缓冲器68之前可由rdac 54调节。具体地说,rdac 54的电阻的调节可影响传输至缓冲器68的电压的变化。而且,电流源56及60对各rdac 54的偏置可提供恒定电流,以保持各rdac 54上的恒定电压降,从而可依据rdac 54的电阻值从在输入端口52所接收的参考电压(v

mid

)产生良好定义的电平偏移。在一个实施例中,各sar片42的rdac 54的开关86经配置而被独立控制,从而可将各rdac 54的输出电压单独设置为特定值。各sar片42的rdac 54的电压偏移独立于该参考电压(v

mid

)的值或幅度。

[0021]

各sar片42的缓冲器68可具有输入以及具有低输出电阻的输出,且其电平偏移在所述输出端口的输入电压。sar 18的各并行sar片42的缓冲器68可基于在其输入端口52所接收的电压在其输出端口生成模拟电压。在一个实施例中,缓冲器68可为源极跟随器缓冲器,其包括电流源66以及晶体管64。晶体管64可为p型场效应晶体管,且电流源66可与晶体管64的源极70耦接,晶体管64的漏极72可与地46耦接,且晶体管64的栅极74可与rdac 54的输出端口76耦接,以接收从rdac 54输出的参考电压(v

ref

)。

[0022]

可将参考电压(v

ref

)从rdac 54的输出端口76提供给缓冲器68的输入。在缓冲器68的输出80的电压(v

refbuf

)可为高于该参考电压(v

ref

)的栅极-源极电压降。假设从晶体管64的栅极74至源极70的电压可因温度依赖因素(例如阈值电压及迁移率)而为温度依赖,各sar片42的v

refbuf

在输出80可具有温度变化(例如,从-10℃至125℃通常为70mv)。全局参考电路20中的晶体管26的阈值电压可部分补偿各缓冲器68中的晶体管64的温度依赖性。尤其,可将晶体管26及各晶体管64类似地偏置,以使它们的输出电压的温度系数基本相同。不过,rdac 54的操作可提供独立于温度的电压调节,以允许各sar片42使用不同于该全局参考电压但具有相同的温度依赖性的参考电压。因此,补偿晶体管64的基于温度的阈值电压

偏离可与rdac 54提供的可预测delta电压步进(delta voltage step)(它不依赖于工艺角(process corner))组合。结果是在不同片42的缓冲器68的输出80的电压值(v

refbuf

)可随温度变化而保持恒定,并可在每片基础上单独调谐至特定电压。

[0023]

sar 18的各sar片42还可包括电容式数模转换器(cdac)88以及与cdac 88耦接的sar控制电路89。cdac 88(结合图5进一步说明)自缓冲器68的输出80接收该参考电压(v

refbuf

)。

[0024]

在一个替代实施例中并如图3a中所示,缓冲器68可为超级源极跟随器,其包括另一个晶体管69以及另一个电流源67。晶体管69可为n型场效应晶体管,其具有与晶体管64的漏极耦接的栅极,与地46耦接的源极,以及与输出80耦接的漏极。晶体管64的漏极与电流源67耦接。

[0025]

最佳如图4中所示,rdac 54可使用电阻器串架构(例如,串式dac),其具有串行耦接的多个电阻器82,在各电阻器82之间具有节点84。例如,多个开关86可与一个或多个电阻器82连接,以提供可选电阻以及在输出端口76的相关电压。rdac 54具有数字输入代码(例如,d0、d1、d2)与互补数字代码(例如,),以提供rdac代码,该rdac代码激活并控制开关86将选定电阻器82切换至与输出端口76的连接中。供应给rdac 54的这些数字输入代码调节开关86,以提供高于或低于该参考电压(v

mid

)的固定的且独立于温度的电压降。例如,当应用全标度代码(full-scale code)时,最上面的开关可闭合,且输出(例如,v

ref

)可进至全标度(例如,rdac 54的全标度代码可产生v

top

减去1个最低有效位的输出)。类似地,当应用零标度代码时,最下面的开关86可闭合,且输出(例如,v

ref

)可进至零标度(例如,rdac 54的零标度代码可产生v

bot

的输出)。例如,沿着该串或链的每个电阻器82可产生等于1个最低有效位的电压降。而且,可被应用于rdac 54的每个代码可具有一个电阻器-开关对。因此,随着分辨率增加,在rdac 54的设计中的电阻器82及开关86的数目可呈指数增加。各电阻器82可具有固定的电阻值,因此,各电阻器82可产生恒定的delta电压。相应地,每个rdac步进(rdac step)可为偏离输入端口52的电压的恒定电压。

[0026]

通过使用校准算法可校准sar 18的各sar片42。例如,通过供应给定的rdac代码,可将各sar片42的本地rdac 54设置为名义值,接着,通过逐个(例如,针对sar 18的1至n并行sar片42)感测各本地rdac 54的输出端口76(例如,v

ref

),可调节该参考电压(v

refglobal

),接着,可将该参考电压(v

refglobal

)设置为各本地rdac 54的输出端口76的平均值。或者,可将该参考电压(v

refglobal

)设置在名义值,并可使用单独rdac进行校准。接着,可调节该全局参考电压(v

refglobal

),以使本地rdac 54居中或者避免它们被围挡(railed)。例如,若被围挡(v

ref

等于v

top

),该参考电压(v

refbuf

)可能降低预设数目的最低有效位,或者,各本地rdac 54的输出端口76的最大值及最小值可经调节以输出自中心抽头的电压(v

mid

)的最小偏离。

[0027]

请参照图5,sar 18的各片42可包括基于电荷再分布而工作的电容式数模转换器(cdac)88。cdac 88包括电容器c1、...、c

n-3

、c

n-2

、c

n-1

及c

n

,它们通过开关s1、...、s

n-3

、s

n-2

、s

n-1

及s

n

在电压(v

refbuf

)与地之间切换。切换电容器c1、...、c

n-3

、c

n-2

、c

n-1

及c

n

以设置合适的输出电压v

out

。该cdac输出电压的步长(step size)通过电容器比例及参考电压(v

refbuf

)设置。将dac增益定义为cdac模拟输出相对数字输入的曲线的斜率。在电容器c1、...、c

n-3

、c

n-2

、c

n-1

及c

n

上的电荷再分布使电流自正参考电压(v

refbuf

)汲取或灌入。电容器c1、...、c

n-3

、c

n-2

、c

n-1

及c

n

的电容受环境温度影响,不过它对cdac步长的影响极小,因为它是电容器比例

的函数。电压(v

refbuf

)可能受温度偏移影响。由于cdac 88中的v

refbuf 80可能随温度变化,因此cdac 88的增益可能随v

refbuf

线性移动。cdac 88的增益直接影响adc 15的增益。因此,adc 15所经历的增益变化可能发生于由v

refbuf

表示的电压具有温度偏移的环境中。

[0028]

本文中引用的由近似语言例如“大约”、“大致”及“基本上”所修饰的术语不限于所指定的精确值。该近似语言可对应于用以测量该值的仪器的精度,且除非另外依赖于该仪器的精度,否则可表示所述值的+/-10%。

[0029]

与另一个特征“连接”或“耦接”的特征可与该另一个特征直接连接或耦接,或者可存在一个或多个中间特征。如果不存在中间特征,则特征可与另一个特征“直接连接”或“直接耦接”。如存在至少一个中间特征,则特征可与另一个特征“非直接连接”或“非直接耦接”。在另一个特征“上”或与其“接触”的特征可直接在该另一个特征上或与其直接接触,或者可存在一个或多个中间特征。如果不存在中间特征,则特征可直接在另一个特征“上”或与其“直接接触”。如存在至少一个中间特征,则特征可“不直接”在另一个特征“上”或与其“不直接接触”。

[0030]

对本发明的各种实施例所作的说明是出于示例目的,而非意图详尽无遗或限于所揭示的实施例。许多修改及变更对于本领域技术人员将显而易见,而不背离所述实施例的范围及精神。本文中所使用的术语经选择以最佳解释这些实施例的原理、实际应用或在市场已知技术上的技术改进,或者使本领域技术人员能够理解本文中所揭示的实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1