信号输出装置及方法与流程

1.本发明是关于信号输出技术,尤其是关于一种信号输出装置及方法。

背景技术:

2.通用串行总线(universal serial bus;usb)是连接计算机系统与外部装置的一种串行端口总线标准,也是一种输入输出接口的技术规范。由于为许多不同的外部装置的统一标准,且具有易插拔的特性,因此通用串行总线成为最主流的连接接口。

3.具有通用串行总线2.0接口的输出电路可支持不同传输速度的模式。然而,在不同速度的传输操作模式下,输出电路中的组件所据以操作的电压不同,而对组件的寄生电容的电容值大小产生影响。如果没有针对寄生电容的调整机制,则组件容易因为在不同的操作模式下,而使输出信号有电压转换速率过快或过慢,以及电压过冲(overshoot)与电压下冲(undershoot)的问题。

技术实现要素:

4.鉴于先前技术的问题,本发明的目的在于提供一种信号输出装置及方法,以改善先前技术。

5.本发明的目的在于提供一种信号输出装置及方法,藉由在两个输出端间设置金属氧化物半导体(metal-oxide-semiconductor,以下简写为mos)晶体管电容器,响应于不同速度的操作模式而产生不同大小的电容值,进而降低寄生电容造成的影响,使信号的输出表现更佳。

6.本发明包括一种信号输出装置,其一实施例包括两个输出电路、两个mos晶体管电容器以及两个电流供应电路。两个输出电路各包括:反相器以及电阻器。反相器具有输入端以及输出端。电阻器电性耦接于输出端与差分输出端之间。两个mos晶体管电容器分别以相反的方向电性耦接于两个输出电路的输出端之间。两个电流供应电路分别电性耦接于两个输出电路中的对应的输出电路的差分输出端。在第一操作模式下,两个电流供应电路被停用,两个输出电路的输入端分别接收高电平输入电压以及低电平输入电压,以在两个输出电路的输出端分别产生低电平输出电压以及高电平输出电压,进而使两个mos晶体管电容器的电容值均大于预设基准。在第二操作模式下,两个电流供应电路仅其中之一被启用以输出供应电流至对应的差分输出端,两个输出电路的输入端分别均接收高电平输入电压,以在两个输出电路的输出端分别产生低电平输出电压,进而使两个mos晶体管电容器的电容值均不大于预设基准。

7.本发明另包括一种信号输出方法,应用于信号输出装置中,其中信号输出装置包括两个输出电路、两个mos晶体管电容器以及两个电流供应电路,两个输出电路各包括具有输入端以及输出端的反相器以及电性耦接于输出端与差分输出端之间的电阻器,两个mos晶体管电容器分别以相反的方向电性耦接于两个输出电路的输出端之间,两个电流供应电路分别电性耦接于两个输出电路中的对应的输出电路的差分输出端。信号输出方法之一实

施例包括下列步骤:在第一操作模式下,使两个电流供应电路被停用;在第一操作模式下,使两个输出电路的输入端分别接收高电平输入电压以及低电平输入电压,以在两个输出电路的输出端分别产生低电平输出电压以及高电平输出电压,进而使两个mos晶体管电容器的电容值均大于预设基准;在第二操作模式下,使两个电流供应电路仅其中之一被启用以输出供应电流至对应的差分输出端;以及在第二操作模式下,使两个输出电路的输入端分别接收高电平输入电压,以在两个输出电路的输出端分别产生低电平输出电压,进而使两个mos晶体管电容器的电容值均不大于预设基准。

8.有关本案的特征、实作与功效,兹配合图式作较佳实施例详细说明如下。

附图说明

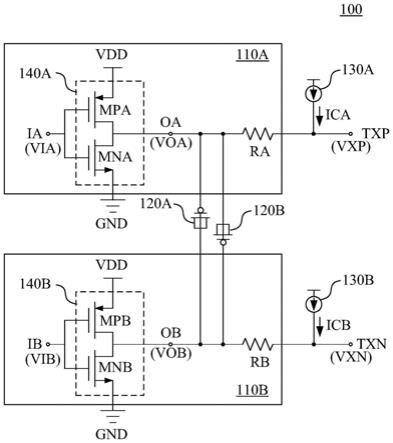

9.图1显示本发明之一实施例中,一种信号输出装置的电路图;以及

10.图2显示本发明之一实施例中,一种信号输出方法的流程图。

具体实施方式

11.本发明的目的在于提供一种信号输出装置及方法,藉由在两个输出端间设置mos晶体管电容器,响应于不同速度的操作模式而产生不同大小的电容值,进而降低寄生电容造成的影响,使信号的输出表现更佳。

12.请参照图1。图1显示本发明之一实施例中,一种信号输出装置100的电路图。于一实施例中,信号输出装置100设置于通用串行总线(universal serial bus;usb)2.0界面的收发器中。信号输出装置100包括:两个输出电路110a、110b、两个mos晶体管电容器120a、120b以及两个电流供应电路130a、130b。

13.输出电路110a、110b各包括:反相器以及电阻器。

14.以输出电路110a为例,其包括反相器140a以及电阻器ra。于一实施例中,反相器140a包括一个p型mos晶体管mpa以及一个n型mos晶体管mna。

15.p型mos晶体管mpa以及n型mos晶体管mna的源极分别电性耦接于电压源vdd以及接地端gnd。p型mos晶体管mpa以及n型mos晶体管mna的栅极互相电性耦接至输入端ia。p型mos晶体管mpa以及n型mos晶体管mna的漏极互相电性耦接至输出端oa。其中,输入端ia被配置为接收输入电压via,并在输出端oa产生输出电压voa。

16.电阻器ra电性耦接于输出端oa与差分输出端txp之间,以将输出电压voa由输出端oa输出至差分输出端txp,产生差分电压vxp。

17.以输出电路110b为例,其包括反相器140b以及电阻器rb。于一实施例中,反相器140b包括一个p型mos晶体管mpb以及一个n型mos晶体管mnb。

18.p型mos晶体管mpb以及n型mos晶体管mnb的源极分别电性耦接于电压源vdd以及接地端gnd。p型mos晶体管mpb以及n型mos晶体管mnb的栅极互相电性耦接至输入端ib。p型mos晶体管mpb以及n型mos晶体管mnb的漏极互相电性耦接至输出端ob。其中,输入端ib被配置为接收输入电压vib,并在输出端ob产生输出电压vob。

19.电阻器rb电性耦接于输出端ob与差分输出端txn之间,以将输出电压vob由输出端ob输出至差分输出端txn,产生差分电压vxn。

20.需注意的是,信号输出装置100是以差分的方式,同时输出一对差分电压vxp、vxn。

21.mos晶体管电容器120a、120b分别以相反的方向电性耦接于输出电路110a、110b的输出端oa与ob之间。举例而言,mos晶体管电容器120a以顺向电性耦接于输出端oa与ob之间,而mos晶体管电容器120b以逆向电性耦接于输出端oa与ob之间。

22.其中,mos晶体管电容器120a、120b是以mos晶体管实现,且其电容值的大小是与其两端所连接的输出端oa、ob的电压差值相关。

23.于一实施例中,当输出端oa、ob的电压差值大于mos晶体管电容器120a、120b的阈值电压(threshold voltage)时,将使mos晶体管电容器120a、120b的电容值大于一个预设基准。而当输出端oa、ob的电压差值不大于mos晶体管电容器120a、120b的阈值电压时,将使mos晶体管电容器120a、120b的电容值不大于预设基准。于一实施例中,mos晶体管电容器120a、120b的阈值电压为例如,但不限于0.7伏特。

24.电流供应电路130a、130b分别电性耦接于输出电路110a的差分输出端txp和输出电路110b的差分输出端txn。其中,电流供应电路130a、130b可由例如,但不限于电流源以及对应的开关控制电路(未绘示)实现。然而本发明并不为此所限。

25.于一实施例中,以通用串行总线(universal serial bus;usb)2.0接口运行的信号输出装置100,可操作于不同传输速度的操作模式下。更详细地说,依传输速度的不同,信号输出装置100可运行于低速(low speed)模式、全速(full speed)模式以及高速(high speed)模式。于一实施例中,低速模式为1.5mbps(192kb/s),全速模式为12mbps(1.5mb/s),且高速模式为480mbps(60mb/s)。

26.在上述不同传输速度操作模式下,输出电路110a中的反相器140a中的寄生电容、输出电路110b中的反相器140b中的寄生电容将呈现不同的电容值大小。

27.以反相器140a为例,在速度较低的低速模式以及全速模式中,p型mos晶体管mpa以及n型mos晶体管mna在栅极与漏极间的寄生电容,将有较大的寄生电容值。这样的特性,使输出端oa产生的信号在电平转换时,有较低的电压转换速率(slew rate),同时亦有较大的电压过冲(overshoot)量以及电压下冲(undershoot)量。

28.相对的,在速度较高的高速模式中,p型mos晶体管mpa以及n型mos晶体管mna在栅极与漏极间的寄生电容,将有较小的寄生电容值。这样的特性,将不易对输出端oa产生的信号造成影响。

29.因此,信号输出装置100将可藉由mos晶体管电容器120a、120b的设置,在不同传输速度的操作模式下,均有较佳的表现。

30.以下将以速度较低的低速模式以及全速模式做为第一操作模式,并以速度较高的高速模式做为第二操作模式,对于信号输出装置100的运行进行说明。

31.在第一操作模式下,电流供应电路130a、130b被停用,而不输出电流至对应的差分输出端txp、txn。

32.此时,输出电路110a的输入端ia所接收的输入电压via和输出电路110b的输入端ib所接收的输入电压vib之一为高电平输入电压,另一则为低电平输入电压。于一实施例中,高电平输入电压为3.3伏特,低电平输入电压为0伏特。

33.经由反相器140a、140b的运行,输出端oa所产生的输出电压voa和输出端ob所产生的输出电压vob之一为低电平输出电压,另一则为高电平输出电压。进一步地,差分输出端txp、txn分别通过电阻器ra、rb接收输出电压voa、vob,以产生其中之一为第一模式差分低

电平电压且另一者为第一模式差分高电平电压的差分电压vxp、vxn。

34.举例而言,当输入电压via、vib分别为高电平输入电压以及低电平输入电压时,输出电压voa、vob分别为低电平输出电压以及高电平输出电压。差分电压vxp、vxn则分别为第一模式差分低电平电压以及第一模式差分高电平电压。相对的,当输入电压via、vib分别为低电平输入电压以及高电平输入电压时,输出电压voa、vob分别为高电平输出电压以及低电平输出电压。差分电压vxp、vxn则分别为第一模式差分高电平电压以及第一模式差分低电平电压。

35.于一实施例中,高电平输出电压以及第一模式差分高电平电压均为3.3伏特,低电平输出电压以及第一模式差分低电平电压均为0伏特。

36.在这样的状况下,由于输出端oa、ob中的一者为高电平输出电压(例如3.3伏特),一者为低电平输出电压(例如0伏特),两者间的电压差值将为3.3伏特,大于mos晶体管电容器120a、120b的阈值电压(例如0.7伏特),mos晶体管电容器120a、120b的电容值将大于预设基准。

37.由于在第一操作模式下,反相器140a、140b有较大的寄生电容值,导致输出电压voa、vob在电平转换时有较快的电压转换速率,并容易产生较大的电压过冲量以及电压下冲量。因此,mos晶体管电容器120a、120b具有较大的电容值,将可有效减慢电压转换速率,同时降低电压过冲量以及电压下冲量。

38.在第二操作模式下,电流供应电路130a、130b仅其中之一被启用以输出供应电流至对应的差分输出端。举例而言,当电流供应电路130a被启用时,将输出供应电流ica至差分输出端txp,而电流供应电路130b将被停用。当电流供应电路130b被启用时,将输出供应电流icb至差分输出端txn,而电流供应电路130a将被停用。

39.此时,输出电路110a的输入端ia所接收的输入电压via和输出电路110b的输入端ib所接收的输入电压vib均为高电平输入电压。于一实施例中,高电平输入电压为3.3伏特。

40.经由反相器140a、140b的运行,输出端oa所产生的输出电压voa和输出端ob所产生的输出电压vob均为低电平输出电压。

41.此时,响应于是否接收到供应电流,差分输出端txp、txn在其中之一输出第二操作模式差分高电平电压,并在另一者输出第二操作模式差分低电平电压。

42.举例而言,当差分输出端txp接收到电流供应电路130a的供应电流ica,而差分输出端txn并未接收到电流供应电路130b的供应电流时,差分输出端txp将输出第二操作模式差分高电平电压,差分输出端txn则输出第二操作模式差分低电平电压。

43.相对的,当差分输出端txn接收到电流供应电路130b的供应电流icb,而差分输出端txp并未接收到电流供应电路130a的供应电流时,差分输出端txn将输出第二操作模式差分高电平电压,差分输出端txp则输出第二操作模式差分低电平电压。

44.于一实施例中,第二操作模式差分高电平电压为0.4伏特。低电平输出电压以及第二操作模式差分低电平电压为0伏特。

45.在这样的状况下,由于输出端oa、ob两者均为低电平输出电压(例如0伏特),两者间的电压差值将为0伏特,不大于mos晶体管电容器120a、120b的阈值电压(例如0.7伏特),mos晶体管电容器120a、120b的电容值将不大于预设基准。

46.由于在第二操作模式下,反相器140a、140b有较小的寄生电容值,不易对输出电压

voa、vob造成影响。因此,mos晶体管电容器120a、120b具有较小的电容值,将可有效加速在差分输出端txp、txn的电压转换速率,同时不会造成电压过冲以及电压下冲。

47.因此,本发明的信号输出装置100可同时适用于不同速度的操作模式,降低寄生电容造成的影响,使信号的输出表现更佳。

48.请参照图2。图2显示本发明一实施例中,一种信号输出方法200的流程图。

49.除前述装置外,本发明另揭露一种信号输出方法200,应用于例如,但不限于图1的信号输出装置100中。信号输出方法200之一实施例如图2所示,包括下列步骤:

50.于步骤s210:判断信号输出装置100是否运行于第一操作模式中。

51.于步骤s220:当信号输出装置100运行在第一操作模式下时,使电流供应电路130a、130b被停用。

52.于步骤s230:使输出电路110a的输入端ia和输出电路110b的输入端ib分别接收高电平输入电压以及低电平输入电压,以在输出端oa、ob分别产生低电平输出电压以及高电平输出电压,进而使mos晶体管电容器120a、120b的电容值大于预设基准。

53.此时,输出端oa、ob分别产生的低电平输出电压以及高电平输出电压将分别通过电阻器ra、rb传送至差分输出端txp、txn,以分别产生第一模式差分高电平电压以及第一模式差分低电平电压。

54.于步骤s240:当信号输出装置100并非运行在第一操作模式下,则判断出信号输出装置100运行在第二操作模式下,使电流供应电路130a、130b仅其中之一被启用以输出供应电流ica或icb至对应的差分输出端txn、txp。

55.此时,差分输出端txn、txp将根据是否接收到供应电流,产生第二模式差分高电平电压以及第二模式差分低电平电压。

56.于步骤s250:使输出电路110a的输入端ia和输出电路110b的输入端ib分别接收高电平输入电压,以在输出端oa、ob分别产生低电平输出电压,进而使mos晶体管电容器120a、120b的电容值不大于预设基准。

57.需注意的是,上述的实施方式仅为一范例。于其他实施例中,本领域的通常知识者当可在不违背本发明的精神下进行更动。

58.综合上述,本发明中信号输出装置及方法可藉由在两个输出端间设置mos晶体管电容器,响应于不同速度的操作模式而产生不同大小的电容值,进而降低寄生电容造成的影响,使信号的输出表现更佳。

59.虽然本案之实施例如上所述,然而该些实施例并非用来限定本案,本技术领域具有通常知识者可依据本案之明示或隐含之内容对本案之技术特征施以变化,凡此种种变化均可能属于本案所寻求之专利保护范畴,换言之,本案之专利保护范围须视本说明书之申请专利范围所界定者为准。

60.附图标记说明:

61.100:信号输出装置

62.110a:输出电路

63.110b:输出电路

64.120a:mos晶体管电容器

65.120b:mos晶体管电容器

66.130a:电流供应电路

67.130b:电流供应电路

68.140a:反相器

69.140b:反相器

70.gnd:接地端

71.ia:输入端

72.ib:输入端

73.ica:供应电流

74.icb:供应电流

75.mna:n型mos晶体管

76.mnb:n型mos晶体管

77.mpa:p型mos晶体管

78.mpb:p型mos晶体管

79.oa:输出端

80.ob:输出端

81.ra:电阻器

82.rb:电阻器

83.txn:差分输出端

84.txp:差分输出端

85.vdd:电压源

86.via:输入电压

87.vib:输入电压

88.voa:输出电压

89.vob:输出电压

90.vxn:差分电压

91.vxp:差分电压

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1