一种数据速率逐比特可变的数模转换装置及配置方法与流程

[0001]

本发明涉及数模转换技术领域,特别是指一种数据速率逐比特可变的数模转换装置及配置方法。

背景技术:

[0002]

面对移动通信和卫星通信领域功能多样化、功能集成化、设备小型化的状况,调制解调器需要在设备小型化的前提下集成更多的功能,尤其需要覆盖数据速率范围更广的通信体制。ad9361射频捷变收发器将其信号链封装于一个软件可配置的ic中,并以其可配置性、低功耗、体积小的优点在通信领域得到了广泛应用。目前,基于专门数模转换芯片的数据速率逐比特可变的数模转换装置需要额外的时钟管理芯片来提供时钟,成本高且硬件电路复杂。而基于ad9361射频捷变收发器的数模转换装置,一旦切换数据速率需要按其设计限制重新计算时钟配置函数的参数值,无法实现自适应配置。因此采用数据速率逐比特可变的数模转换装置及配置方法来满足功能多样化、设备小型化的调制解调器设计具有重要的应用价值。

技术实现要素:

[0003]

有鉴于此,本发明提出一种数据速率逐比特可变的数模转换装置及配置方法,其能够实现数模转换装置在步进1hz、范围1mhz-125mhz内数据速率时钟的实时切换。

[0004]

为了实现上述目的,本发明提供的技术方案是:一种数据速率逐比特可变的数模转换装置,其包括配置单元1、数模转换单元2、时钟单元3、供电单元4,所述配置单元1包括单片机,该单片机以软件模块的形式实现查表单元5、存储单元6、运算单元7和参数配置单元8,所述数模转换单元2包括ad9361射频捷变收发器;其中,配置单元1根据外部输入的数据速率指令,经过内部的查表单元5、存储单元6、运算单元7和参数配置单元8运算得到控制指令,将控制指令输出至数模转换单元2;数模转换单元2根据外部输入的控制指令配置ad9361射频捷变收发器输出所需的数据速率时钟,同时将外部输入的该数据速率下的数字信号转换成模拟信号输出;时钟单元3将内部8mhz贴片晶振的时钟供给配置单元1,并将内部50mhz恒温晶振的时钟供给数模转换单元2;供电单元4用于为配置单元1、数模转换单元2和时钟单元3供电。

[0005]

进一步的,所述查表单元5将步进1hz、范围1mhz~125mhz内可变的数据速率时钟划分为8个地址值,并根据外部输入的所需数据速率将对应的地址值输出至存储单元6;所述存储单元6包括与所述8个地址值一一对应的8个数组,每个数组由6个元素组成,6个元素分别对应6级时钟与需求数据速率的关系系数;存储单元6根据输入的地址值将对应数组输出给运算单元7;所述运算单元7将6个关系系数分别乘上外部输入的所需数据速率,得到一个新的数组

并输出至参数配置单元8;所述参数配置单元8把输入数组作为函数参数,调用ad9361射频捷变收发器自带的时钟配置函数ad9361_set_trx_path_clks,根据时钟配置函数的输出值生成控制指令,并将控制指令传给数模转换单元2。

[0006]

进一步的,所述查表单元5根据外部输入的所需数据速率将对应的地址值输出至存储单元6的具体方式为,将1mhz~125mhz的范围划分为8个区间,这8个区间与所述8个地址值一一对应,当外部输入的所需数据速率落入某个区间,则将该区间对应的地址值输出给存储单元6。

[0007]

进一步的,所述供电单元4包括ltm4644电源芯片和adp1755电源芯片, ltm4644电源芯片将外部输入的直流5v分出一路直流3.3v和一路直流2.5v,adp1755电源芯片将ltm4644电源芯片分出的直流2.5v再分出一路直流1.3v;其中,直流3.3v用于给配置单元1内的单片机以及时钟单元3内的8mhz贴片晶振供电,直流5v用于给时钟单元3内的50mhz恒温晶振供电,直流2.5v和直流1.3v用于给数模转换单元2中的ad9361射频捷变收发器供电。

[0008]

此外,本发明还提供一种数据速率逐比特可变的数模转换方法,该方法基于上述任一数模转换装置实现,包括以下步骤:(1)将ad9361射频捷变收发器作为数模转换单元,单片机作为配置单元,配置单元根据外部输入的所需数据速率指令,计算得到数模转换单元时钟配置函数需要的参数;(2)将步骤(1)得到的参数经由spi总线传输给数模转换单元,数模转换单元根据参数实现数模转换装置的数据速率切换;(3)根据ad9361射频捷变收发器的特性,由需要产生的数据速率计算1级fir滤波器、3级半带滤波器、1级数模转换和基带锁相环的共6个数据时钟,再依据这6级时钟之间的限制条件,预先为步进1hz、范围1mhz-125mhz内可变的数据速率时钟设计出该6级时钟与需求数据速率之间的关系,量化成数值并以数组的形式存储在存储单元里;(4)每次按照需要ad9361射频捷变收发器产生的数据速率去查表单元中映射出存储单元中相应的数组地址,并通过存储单元把含有6个变量系数的数组输出给运算单元;(5)运算单元按输入数组中的6个变量值与需求数据速率相乘得到6级时钟的值,然后输出给参数配置单元;(6)参数配置单元利用ad9361射频捷变收发器自带的时钟配置函数,以6级时钟的值作为该函数的参数,输出控制指令,从而实现数模装置的数据速率逐比特可变的自适应配置。

[0009]

从上面的叙述可以看出,本发明技术方案的有益效果在于:1、本发明以ad9361射频捷变收发器作为数模转换装置,在单片机上设计查表算法配置其时钟配置函数,从而实现一种数模转换装置的数据速率逐比特可变的自适应配置;同时单片机配置ad9361射频捷变收发器简化了硬件电路实现,优化查表算法设计高效快速的实现数模转换装置数据速率的逐比特可变。

[0010]

2、本发明利用ad9361射频捷变收发器作为数模转换单元,从而简化了硬件电路设计,利用单片机去配置ad9361射频捷变收发器,从而简化了配置算法的设计;其配置方法利用数组预存6级时钟与需求数据速率的系数实现了该数模转换装置的数据速率逐比特可变的自适应配置,并利用系数数组的寻址简化了时钟配置函数对不同数据速率下参数切换的实现,同时利用查表单元的优化设计,减小了1mhz-125mhz内逐比特可变数据速率时钟的分

类数目,从而缩减了存储单元中数组占用的存储空间。

[0011]

3、本发明在单片机上优化查表算法,自适应给出时钟配置函数的参数,经spi口直接控制数模转换芯片,从而实现数模转换装置在步进1hz、范围1mhz-125mhz内数据速率时钟的实时切换。

[0012]

4、本发明以ad9361射频捷变收发器作为数模转换芯片,并以单片机与其通信实现控制指令下发和状态回报,简化数模转换装置内部的交互流程,使用简单,体积小,成本低。

[0013]

总之,本发明相对于现有的数据速率逐比特可变的数模转换装置具有硬件电路简单、成本低,配置算法结构简单、占用资源少、能够自适应切换的特点,特别适用于通信系统中数模转换装置对数据速率可变范围广、快速切换和简单实现要求高的情况。

附图说明

[0014]

为了更加清楚地描述本专利,下面提供一幅或多幅附图,这些附图旨在对本专利的背景技术、技术原理和/或某些具体实施方案做出辅助说明。

[0015]

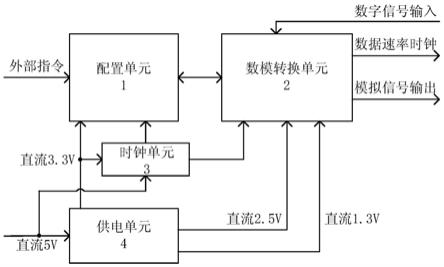

图1是本发明实施例中数模转换装置的原理方框图。

[0016]

图2是图1中配置模块的原理方框图。

具体实施方式

[0017]

为了便于本领域技术人员对本专利技术方案的理解,同时,为了使本专利的技术目的、技术方案和有益效果更加清楚,并使权利要求书的保护范围得到充分支持,下面以具体案例的形式对本专利的技术方案做出进一步的、更详细的说明。

[0018]

参照图1,一种数据速率逐比特可变的数模转换装置,其包括配置单元1、数模转换单元2、时钟单元3、供电单元4。图1是本发明的硬件设计原理方框图,实施例按图1连接线路。

[0019]

其中,供电单元根据外部输入直流5v电源由内部2个电源芯片分出直流1.3v、2.5v、3.3v用来供给配置单元1、数模转换单元2和时钟单元3。时钟单元3内部2个晶振分别给配置单元1和数模转换单元2提供参考时钟源。配置单元1和数模转换单元2之间通过spi口直连通信,用来传输配置单元1给数模转换单元2下发的控制指令和数模转换单元2给配置单元1回报的状态参数。配置单元1根据外部输入的步进1hz、范围1mhz~125mhz内的数据速率指令,由算法处理得到相应的控制指令下发给数模转换单元2。数模转换单元2根据输入的控制指令配置其芯片工作状态,产生所需的数据速率时钟并输出给后端装置,同时可将外部输入的数字信号经过正交上变频处理得到模拟信号并输出。

[0020]

图2是配置单元1的原理方框图。从配置单元1输入的所需数据速率指令输入给查表单元5,查表单元5根据该数据速率值的范围映射其相应的地址值,并输出给存储单元6。

[0021]

存储单元6内部存储了预先设计的8个6元数组,其根据输入的地址值输出对应的数组。

[0022]

运算单元7将外部输入的数据速率值分别与数组中的6个值相乘,得到一个新的数组,并输出给参数配置单元8。

[0023]

参数配置单元8将输入的数组作为时钟配置函数ad9361_set_trx_path_clks的参数,运行函数得到控制指令并输出给数模转换单元2。

[0024]

查表单元5将1mhz~125mhz的范围(即ad9361射频捷变收发器所能处理的速率范围)划分为8个区间,这8个区间与所述8个地址值一一对应,当外部输入的所需数据速率落入某个区间,则将该区间对应的地址值输出给存储单元6。

[0025]

基于上述数模转换装置,可以实现如下数模转换方法。具体方式为:1)供电单元4通过内部的2个电源芯片把外部输入的直流5v生成直流3.3v、直流2.5v和直流1.3v分别给配置单元1、数模转换单元2和时钟单元3供电。

[0026]

2)时钟单元3内部的2个晶振分别给配置单元1和数模转换单元2提供8mhz和50mhz的参考时钟源。

[0027]

3)配置单元1内部的查表单元5根据外部输入的步进1hz、范围1mhz~125mhz内的数据速率判断所在速率范围,并找到其对应的地址值输出给存储单元6。

[0028]

4)存储单元6依据ad9361射频捷变收发器6级时钟与数据速率时钟之间的限制条件预先设计出8个6元数组来量化它们之间的关系,根据输入的地址值输出对应的表示6级时钟与数据速率之间关系的数组。

[0029]

5)运算单元7把所需数据速率与数组内的元素分别相乘得到了对应6级时钟的具体数值。

[0030]

6)参数配置单元把这6级时钟值以数组的形式作为ad9361射频捷变收发器自带的时钟配置函数ad9361_set_trx_path_clks的参数,调用该函数,产生相应的控制指令并作为配置单元1的输出。

[0031]

7)配置单元1通过与数模转换单元2之间的spi口下发控制指令,数模转换单元2进行相应配置输出所需的数据速率时钟给fpga或其它基带信号处理芯片,同时fpga或其它基带信号处理芯片将输入的已调制的数字基带信号正交上变频到中频模拟信号,从而实现数模转换装置的数据速率逐比特可变的自适应功能。

[0032]

总之,本发明基于单片机配置ad9361射频捷变收发器实现数模转换装置的硬件架构,并在单片机内采用分区查表算法实现数据速率逐比特可变的目的。其内部主要由配置单元、数模转换单元、时钟单元、供电单元组成装置的硬件架构,并在配置单元上以软件模块的形式实现查表单元、存储单元、运算单元和参数配置单元。配置单元用来配置模数转换单元的数据速率时钟在步进1hz、范围1mhz-125mhz内快速切换。数模转换单元根据控制指令输出所需的数据速率时钟,同时将外部输入的该数据速率下的数字信号转换成模拟信号输出。时钟单元分别给配置单元和数模转换单元提供8mhz和50mhz的参考时钟源。供电单元给配置单元、数模转换单元、时钟单元提供所需的直流电源。查表单元将输入的所需数据速率映射为对应地址值。存储单元预存了8个6元数组,6元数组对应6级时钟与需求数据速率之间的数值关系,根据外部输入的地址值输出对应的数组。运算单元将输入信号相乘得到实际的6级时钟数值。参数配置单元把以数组形式输入的6级时钟作为时钟配置函数的参数,调用该函数并输出控制指令。

[0033]

该装置在调制解调器中可以实现数模转换单元的数据速率时钟在步进1hz、范围1mhz-125mhz内的自适应快速切换,同时完成数字信号到模拟信号的转换。

[0034]

需要理解的是,上述对于本专利具体实施方式的叙述仅仅是为了便于本领域普通技术人员理解本专利方案而列举的示例性描述,并非暗示本专利的保护范围仅仅被限制在这些个例中,本领域普通技术人员完全可以在对本专利技术方案做出充分理解的前提下,

以不付出任何创造性劳动的形式,通过对本专利所列举的各个例采取组合技术特征、替换部分技术特征、加入更多技术特征等等方式,得到更多的具体实施方式,所有这些具体实施方式均在本专利权利要求书的涵盖范围之内,因此,这些新的具体实施方式也应在本专利的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1