一种开关量信号控制电路的制作方法

[0001]

本实用新型涉及工业自动化控制领域,具体设计一种开关量信号可靠输出的电路。

背景技术:

[0002]

随着国家步入工业4.0信息智能化时代,无人化、自动化、数字化和智能化控制已成为近年来工业现场控制领域最主要发展趋势,几乎已经渗透到工业控制现场中每一个领域,如无人车间、无人餐厅等应用场所;无人化、自动化、数字化和智能化控制是一种建立在可靠稳定的现场控制系统采集和输出的基础之上,对自动控制的精度以及准确度的要求越来越高,如模拟量的采集、开关量输入信号采集、开关量信号输出控制等等。

[0003]

传统的开关量信号输出控制主要原理图如下图1(a)、图1(b)所示;主要通过配置微处理器mcu输出i/o口的高低电平状态来控制晶体三极管或增强型mosfet电子开关的状态,继而达到继电器线圈的得电或失电,最终使得继电器触点闭合或断开,图1(a)、图1(b)的方式具有电气隔离和抗共模干扰能力强的优点,但以上两种方式具有一个致命缺点,当微处理器在得电和失电过程中,微处理器的i/o口是不确定状态或不受控的状态,而且微处理器芯片在得电后到开关量信号输出i/o口初始化之前的这段时间内每一种微处理器芯片的i/o口默认状态不同,有的微处理器芯片i/o口默认状态为高电平,有的微处理器芯片i/o口默认状态为低电平,因此对于图1(a)、图1(b)的传统方案在上述提到不确定状态下很容易产生开关量信号误动作,给控制系统的稳定性、安全性和可靠性带来致命的危害。由于默认电平不可控,因此只能针对不同微处理器进行适应性设置以避免上述误动作。但由于不同微处理器的该默认电平不同,如果针对每个微处理器都进行相应设置,则会大大影响生产效率。

技术实现要素:

[0004]

本实用新型要解决的问题是针对不同微处理器在得电和失电过程中i/o口默认状态不同而且不受控,使得传统的开关量信号控制电路很容易在该过程中产生开关量信号误动作而给控制系统的稳定性、安全性和可靠性带来致命的危害的问题,提供一种开关量信号控制电路。

[0005]

为解决上述技术问题,本实用新型采用的技术方案是:一种开关量信号控制电路,包括微处理器、第一开关管、继电器,所述微处理器具有第一i/o接口、第二i/o接口、第三i/o接口,所述第一开关管的控制端与第一i/o接口电连接,所述继电器的一对常开触点连接在开关量信号控制电路的受控电路中;

[0006]

其特征在于:所述开关量信号控制电路还包括第二开关管、开关管驱动单元,所述第一开关管、第二开关管、继电器线圈串联电连接于第一供电端和地之间;

[0007]

所述开关管驱动单元具有与第三i/o接口电连接的第一端、与第二开关管的控制端电连接的第二端、与第二i/o接口电连接的第三端;

[0008]

所述开关管驱动单元的电路结构使得:

[0009]

(a)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述开关管驱动单元令第二开关管关断;

[0010]

(b)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述开关管驱动单元令第二开关管关断;

[0011]

(c)当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平时,或当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时,或当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平且第一开关管导通时,或当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平且第一开关管导通时,所述开关管驱动单元令第二开关管导通。

[0012]

申请人研究时发现,虽然不同微处理器在得电和失电过程中i/o口默认状态不同且不受控,但对于同一个微处理器,各个i/o口输出电平在该过程中的输出电平状态是一致的,即同为高电平或同为低电平。本实用新型中,当得电或失电过程中第二i/o接口、第三i/o接口的输出默认同为高电平或默认同为低电平时,所述开关管驱动单元均令第二开关管关断,即使此时由于第一i/o接口的默认输出电平而向第一开关管传递了错误的电平信号,由于第一开关管、第二开关管、继电器线圈串联电连接,因此继电器线圈也不会因为误动作而导通,从而避免因第一i/o接口输出所不希望的默认电平信号而产生误动作的风险,有效保护了开关量信号控制电路的受控电路。当第二i/o接口、第三i/o接口的输出为相反电平(一个为高电平、另一个为低电平时),则说明微处理器已经完成对各个i/o接口的初始化,此时利用各个i/o接口对继电器进行控制便不会有误动作的风险。若开关管驱动单元的结构使得当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平时或使得当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时才令第二开关管导通,则可利用第一i/o接口的输出电平对第一开关管的通断进行控制,若第一开关管接通,则串联回路中的第一开关管、第二开关管接通可以使继电器满足得电条件,从而可以安全地对继电器进行控制。若开关管驱动单元的结构使得当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平且第一开关管导通时或使得当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平且第一开关管导通时才令第二开关管导通,则串联回路中的第一开关管、第二开关管接通可以使继电器满足得电条件,从而可以安全地对继电器进行控制。

[0013]

进一步地,所述开关管驱动单元为第三开关管,所述第三开关管的控制端、一个连接端、另一个连接端分别对应为开关管驱动单元的第一端、第二端、第三端;

[0014]

所述第三开关管的电路结构使得:

[0015]

(a1)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述第三开关管关断,从而令第二开关管关断;

[0016]

(b1)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述第三开关管关断,从而令第二开关管关断;

[0017]

(c1)当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平时,或当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时,所述第三开关管导通;

[0018]

(d1)当所述第三开关管导通时,或当所述第一开关管、第三开关管均导通时,所述第二开关管导通。

[0019]

进一步地,所述第一开关管、第二开关管、第三开关管分别为三极管t1、三极管t2、三极管t3,各个三极管的基极对应为各个三极管的控制端,所述三极管t3的集电极、发射极分别为三极管t3的一个连接端、另一个连接端;

[0020]

(a1)所述三极管t1、三极管t2、三极管t3分别为npn型、pnp型、npn型,所述三极管t1的集电极、发射极分别与继电器线圈一端、地对应电连接,所述三极管t2的集电极、发射极分别与继电器线圈另一端、第一供电端对应电连接;或

[0021]

(b1)所述三极管t1、三极管t2、三极管t3分别为npn型、npn型、pnp型,所述三极管t1的集电极、发射极分别与三极管t2的发射极、地对应电连接,所述三极管t2的集电极通过继电器线圈与第一供电端电连接;或

[0022]

(c1)所述三极管t1、三极管t2、三极管t3分别为pnp型、pnp型、npn型,所述三极管t1的集电极通过继电器线圈与地电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、第一供电端对应电连接;或

[0023]

(d1)所述三极管t1、三极管t2、三极管t3分别为pnp型、npn型、pnp型,所述三极管t1的集电极、发射极分别与继电器线圈一端、第一供电端对应电连接,所述三极管t2的集电极、发射极分别与继电器线圈另一端、地对应电连接;或

[0024]

(e1)所述三极管t1、三极管t2、三极管t3分别为pnp型、pnp型、npn型,所述三极管t1的集电极、发射极分别与三极管t2的发射极、第一供电端对应电连接,所述三极管t2的集电极通过继电器线圈与地电连接;或

[0025]

(f1)所述三极管t1、三极管t2、三极管t3分别为npn型、npn型、pnp型,所述三极管t1的集电极通过继电器线圈与第一供电端电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、地对应电连接。

[0026]

进一步地,所述第一开关管、第二开关管、第三开关管分别为mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3,各个mosfet场效应管的栅极分别为各个mosfet场效应管的控制端,所述mosfet场效应管q3的漏极、源极分别为mosfet场效应管q3的一个连接端、另一个连接端;

[0027]

(a2)所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为n沟道增强型、p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极、源极分别与继电器线圈一端、地对应电连接,所述mosfet场效应管q2的漏极、源极分别与继电器线圈另一端、第一供电端对应电连接;或

[0028]

(b2)所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为n沟道增强型、n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、地对应电连接,所述mosfet场效应管q2的漏极通过继电器线圈与第一供电端电连接;或

[0029]

(c2)所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为p沟道增强型、p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极通过继电器线圈与地电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、第一供电端对应电连接;或

[0030]

(d2)所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为p沟道增强型、n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与继电器线

圈一端、第一供电端对应电连接,所述mosfet场效应管q2的漏极、源极分别与继电器线圈另一端、地对应电连接;或

[0031]

(e2)所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为p沟道增强型、p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、第一供电端对应电连接,所述mosfet场效应管q2的漏极通过继电器线圈与地电连接;或

[0032]

(f2)所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为n沟道增强型、n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极通过继电器线圈与第一供电端电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、地对应电连接。

[0033]

进一步地,所述开关管驱动单元为具有两个逻辑输入端、一个逻辑输出端的逻辑门电路,

[0034]

所述逻辑门电路的一个逻辑输入端、一个逻辑输出端、另一个逻辑输入端分别为逻辑门电路的第一端、第二端、第三端;

[0035]

所述逻辑门电路的电路结构使得:

[0036]

(a2)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述逻辑门电路输出第一电平信号,从而令第二开关管关断;

[0037]

(b2)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述逻辑门电路输出第一电平信号,从而令第二开关管关断;

[0038]

(c2)当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平时,或当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时,所述逻辑门电路输出第二电平信号;

[0039]

(d2)当所述逻辑门电路输出第二电平信号时,或当所述第一开关管导通且逻辑门电路输出第二电平信号时,所述第二开关管导通。

[0040]

进一步地,所述第一开关管、第二开关管分别为三极管t1、三极管t2,各个三极管的基极为各个三极管的控制端;

[0041]

(a3)所述三极管t1、三极管t2分别为npn型、pnp型,所述三极管t1的集电极、发射极分别与继电器线圈一端、地对应电连接,所述三极管t2的集电极、发射极分别与继电器线圈另一端、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门;或

[0042]

(b3)所述三极管t1、三极管t2分别为npn型、npn型,所述三极管t1的集电极、发射极分别与三极管t2的发射极、地对应电连接,所述三极管t2的集电极通过继电器线圈与第一供电端电连接,所述逻辑门电路为逻辑异或门;或

[0043]

(c3)所述三极管t1、三极管t2分别为pnp型、pnp型,所述三极管t1的集电极通过继电器线圈与地电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门;或

[0044]

(d3)所述三极管t1、三极管t2分别为pnp型、npn型,所述三极管t1的集电极、发射极分别与继电器线圈一端、第一供电端对应电连接,所述三极管t2的集电极、发射极分别与继电器线圈另一端、地对应电连接,所述逻辑门电路为逻辑异或门;或

[0045]

(e3)所述三极管t1、三极管t2分别为pnp型、pnp型,所述三极管t1的集电极、发射

极分别与三极管t2的发射极、第一供电端对应电连接,所述三极管t2的集电极通过继电器线圈与地电连接,所述逻辑门电路为逻辑异或非门;或

[0046]

(f3)所述三极管t1、三极管t2分别为npn型、npn型,所述三极管t1的集电极通过继电器线圈与第一供电端电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、地对应电连接,所述逻辑门电路为逻辑异或门。

[0047]

进一步地,所述第一开关管、第二开关管分别为mosfet场效应管q1、mosfet场效应管q2,各个mosfet场效应管的栅极分别为各个mosfet场效应管的控制端;

[0048]

(a4)所述mosfet场效应管q1、mosfet场效应管q2分别为n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与继电器线圈一端、地对应电连接,所述mosfet场效应管q2的漏极、源极分别与继电器线圈另一端、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门;或

[0049]

(b4)所述mosfet场效应管q1、mosfet场效应管q2分别为n沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、地对应电连接,所述mosfet场效应管q2的漏极通过继电器线圈与第一供电端电连接,所述逻辑门电路为逻辑异或门;或

[0050]

(c4)所述mosfet场效应管q1、mosfet场效应管q2分别为p沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极通过继电器线圈与地电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门;或

[0051]

(d4)所述mosfet场效应管q1、mosfet场效应管q2分别为p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极、源极分别与继电器线圈一端、第一供电端对应电连接,所述mosfet场效应管q2的漏极、源极分别与继电器线圈另一端、地对应电连接,所述逻辑门电路为逻辑异或门;或

[0052]

(e4)所述mosfet场效应管q1、mosfet场效应管q2分别为p沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、第一供电端对应电连接,所述mosfet场效应管q2的漏极通过继电器线圈与地电连接,所述逻辑门电路为逻辑异或非门;或

[0053]

(f4)所述mosfet场效应管q1、mosfet场效应管q2分别为n沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极通过继电器线圈与第一供电端电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、地对应电连接,所述逻辑门电路为逻辑异或门。

[0054]

进一步地,所述第一供电端与微处理器的正电压供电端电连接。

[0055]

本实用新型具有的优点和积极效果是:本实用新型可以避免因第一i/o接口输出所不希望的默认电平信号而产生误动作的风险,安全地对继电器进行控制。

附图说明

[0056]

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其

他的附图。

[0057]

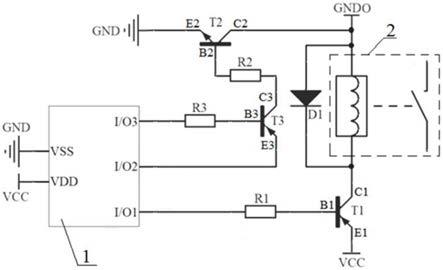

图1(a)现有技术的晶体三极管开关量输出电路结构示意图;

[0058]

图1(b)现有技术的增强型mosfet开关量输出电路结构示意图;

[0059]

图2(a)为本实用新型实施例1的开关量信号控制电路的电路结构示意图;

[0060]

图2(b)为本实用新型实施例2的开关量信号控制电路的电路结构示意图;

[0061]

图2(c)为本实用新型实施例3的开关量信号控制电路的电路结构示意图;

[0062]

图3为本实用新型实施例4的开关量信号控制电路的电路结构示意图;

[0063]

图4为本实用新型实施例7的开关量信号控制电路的电路结构示意图;

[0064]

图5(a)是本实用新型实施例13的开关量信号控制电路的部分电路结构示意图;

[0065]

图5(b)是本实用新型实施例14的开关量信号控制电路的部分电路结构示意图;

[0066]

图5(c)是本实用新型实施例15的开关量信号控制电路的部分电路结构示意图;

[0067]

上述附图中,1、微处理器,2、继电器,3、逻辑异或门,4、逻辑异或非门。

具体实施方式

[0068]

下面将结合本申请的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

[0069]

实施例1

[0070]

如何保证全过程开关量信号能够稳定可靠安全地输出,是减少工业自动化现场控制系统出现误动作的关键所在。

[0071]

本实用新型提供一种开关量信号控制电路,包括微处理器1、第一开关管、继电器2,所述微处理器1具有第一i/o接口、第二i/o接口、第三i/o接口,所述第一开关管的控制端与第一i/o接口电连接,所述继电器2的一对常开触点(p1、p2)连接在开关量信号控制电路的受控电路中,所述开关量信号控制电路还包括第二开关管、开关管驱动单元。通过继电器2的一对常开触点接通或断开,从而使得受控电路接通或关断。

[0072]

所述第一开关管、第二开关管、继电器2线圈串联电连接于第一供电端和地之间。所述第一开关管、第二开关管、继电器2线圈串联电连接于第一供电端和地之间的含义是:所述第一开关管的两个连接端、第二开关管的两个连接端、继电器2线圈两端均位于第一供电端和地之间的串联回路中。

[0073]

所述开关管驱动单元具有与第三i/o接口电连接的第一端、与第二开关管的控制端电连接的第二端、与第二i/o接口电连接的第三端。

[0074]

所述开关管驱动单元的电路结构使得:

[0075]

(a)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述开关管驱动单元令第二开关管关断;

[0076]

(b)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述开关管驱动单元令第二开关管关断;

[0077]

(c)当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平时,或当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时,或当所述第二i/o接口、第三i/

o接口的输出分别为高电平、低电平且第一开关管导通时,或当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平且第一开关管导通时,所述开关管驱动单元令第二开关管导通。

[0078]

第一i/o接口、第二i/o接口、第三i/o接口分别为i/o1、i/o2、i/o3。

[0079]

所述开关管驱动单元为第三开关管,所述第三开关管的控制端、一个连接端、另一个连接端分别对应为开关管驱动单元的第一端、第二端、第三端;

[0080]

如图2(a)所示,本实施例1中,所述第一开关管、第二开关管、第三开关管分别为三极管t1、三极管t2、三极管t3。各个三极管的基极b1、b2、b3对应为各个三极管的控制端,所述三极管t3的集电极c3、发射极e3分别为三极管t3的一个连接端、另一个连接端,且分别与三极管t2的基极b2、第二i/o接口i/o2电连接。

[0081]

所述三极管t1、三极管t2、三极管t3分别为npn型、pnp型、npn型,所述三极管t1的集电极c1、发射极e1分别与继电器2线圈一端、地gnd对应电连接,所述三极管t2的集电极c2、发射极e2分别与继电器2线圈另一端、第一供电端vcc对应电连接。

[0082]

本实施例1中,通过三极管t1、三极管t2、三极管t3的结构及上述连接关系,使得:

[0083]

(a1)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述三极管t3关断,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0084]

(b1)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述三极管t3关断,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0085]

(c1)当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时,三极管t3导通。两个i/o接口存在差异说明微处理器1启动后已经完成了各个io接口的初始化过程,即此时不会受到微处理器刚启动时io接口电平不确定的影响,无需再利用与继电器2线圈串联的两个开关管起到保护作用;

[0086]

(d1)当所述三极管t3导通时,三极管t2导通。若i/o1的输出电平为高电平,则三极管t1导通,此时与继电器1线圈串联的两个开关管均导通,因此可利用i/o1的输出电平来控制继电器1一对常开触点的连通或关断。

[0087]

继电器2线圈并联连接有二极管d1。

[0088]

所述第一供电端vcc可为正电压供电端。优选地,所述第一供电端vcc与微处理器1的正电压供电端vdd电连接。地gnd与微处理器1的接地端vss共地。

[0089]

t1、t2、t3为晶体三极管。pnp三极管可选择仙童公司型号为ss8550bbu的三极管,集电极电流(collector current)i

c

为-1.5a,集电极发射极电压v

ce

为-25v。npn三极管可选择仙童公司型号为bc81716mft的三极管,集电极电流(collector current)为0.8a,集电极发射极电压v

ce

为45v,晶体三极管t1、t2和t3全部工作在开关状态。晶体三极管t1、t2和t3的集电极电流i

c

和集电极发射极电压v

ce

在微处理器的弱电控制系统中足以满足要求。微处理器的i/o口的灌电流和拉电流能力为

±

4ma,i/o输出高电平时一般输出3.3v或者5v电平,输出低电平时一般输出0v电平。开关量输出继电器2的型号可为松下公司的pa1a-5v,线圈两端的额定电压为5vdc,继电器额定电流消耗为24ma,在电源vcc功率足够的情况下,t1、t2、t3晶体三极管足以满足现场开关量信号输出要求。二极管d1为松下继电器线圈的续流二极

管,当继电器线圈在失电情况下二极管d1为线圈能量提供续流回路,以避免出现电压尖峰击穿继电器线圈,二极管型号为仙童公司的fdll4148。

[0090]

微处理器可以为单片机、dsp、fpga,cpld控制芯片,例如ti公司的tms320f2812。

[0091]

三极管t1的基极与第一i/o接口之间连接有第一电阻r1,三极管t2的基极与三极管t3的集电极之间连接有第二电阻r2,三极管t3的基极与第三i/o接口之间连接有第三电阻r3。第一电阻r1、第二电阻r2、第三电阻r3的阻值可选择为4.7kω、1.5kω、4.7kω,从而将流入或流出微处理器i/o口的电流控制在4ma以下。

[0092]

本实施例1中,在微处理器mcu上电后并且初始化完成之后,在微处理器i/o口初始化过程中,可设置i/o1、i/o2和i/o3都为推挽输出状态,并且在微处理器整个开关量输出工作过程中,都设置i/o3为高电平输出、i/o2为低电平输出,当需要控制继电器2触点闭合时,把i/o1设置为高电平,需要控制继电器触点断开时,把i/o1设置为低电平,从而控制继电器2线圈失电或得电,从而使得继电器2的一对常开触点关断或导通,从而实现对受控电路的控制。

[0093]

实施例2

[0094]

如图2(b)所示,本实施例2与实施例1的区别在于:所述三极管t1、三极管t2、三极管t3分别为npn型、npn型、pnp型,所述三极管t1的集电极c1、发射极e1分别与三极管t2的发射极e2、地gnd对应电连接,所述三极管t2的集电极c2通过继电器2线圈与第一供电端vcc电连接。

[0095]

本实施例2中,通过三极管t1、三极管t2、三极管t3的结构及上述连接关系,使得:

[0096]

(a1)当所述第二i/o接口i/o2、第三i/o接口i/o3的输出同为高电平时,所述三极管t3关断,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0097]

(b1)当所述第二i/o接口i/o2、第三i/o接口i/o3的输出同为低电平时,所述三极管t3关断关断,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0098]

(c1)当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平时,所述三极管t3导通。两个i/o接口存在差异说明微处理器1启动后已经完成了各个io接口的初始化过程,即此时不会受到微处理器刚启动时io接口电平不确定的影响,无需再利用与继电器2线圈串联的两个开关管起到保护作用。

[0099]

(d1)当所述三极管t1、三极管t3均导通时,所述三极管t2导通。三极管t3导通后,即可利用三极管t1控制继电器2,即i/o1的输出信号令三极管t1导通,此时三极管t2导通也满足导通条件而导通,从而使得继电器1线圈所在回路导通,从而使得一对常开触点闭合。而如果i/o1的输出信号令三极管t1关断,则说明此时不希望受控电路导通,由于三极管t1关断、三极管t2关断,使得继电器1线圈所在回路无法接通,因此受控电路无法导通。

[0100]

本实施例2中,在微处理器mcu上电后并且初始化完成之后,在微处理器i/o口初始化过程中,设置i/o1、i/o2和i/o3都为推挽输出状态,并且在微处理器整个开关量输出工作过程中,都设置i/o3为低电平输出、i/o2为高电平输出。当需要控制继电器2触点闭合时,把i/o1设置为高电平,需要控制继电器触点断开时,把i/o1设置为低电平,从而控制继电器2线圈失电或得电,从而使得继电器2的一对常开触点关断或导通,从而实现对受控电路的控

制。

[0101]

实施例3

[0102]

如图2(c)所示,本实施例3与实施例1的区别在于:所述三极管t1、三极管t2、三极管t3分别为pnp型、pnp型、npn型,所述三极管t1的集电极通过继电器2线圈与地gnd电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、第一供电端vcc对应电连接。

[0103]

(a1)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述三极管t3关断,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0104]

(b1)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述三极管t3关断,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0105]

(c1)当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时,三极管t3导通。两个i/o接口存在差异说明微处理器1启动后已经完成了各个io接口的初始化过程,即此时不会受到微处理器刚启动时io接口电平不确定的影响,无需再利用与继电器2线圈串联的两个开关管起到保护作用;

[0106]

(d1)当所述三极管t3导通时,三极管t2导通。当所述三极管t3导通时,三极管t2导通。若i/o1的输出电平为低电平,则三极管t1导通,此时与继电器1线圈串联的两个三极管均导通,因此可利用i/o1的输出电平来控制三极管t1,从而控制继电器1一对常开触点的连通或关断。

[0107]

本实施例3中,在微处理器mcu上电后并且初始化完成之后,在微处理器i/o口初始化过程中,设置i/o1、i/o2和i/o3都为推挽输出状态,并且在微处理器整个开关量输出工作过程中,都设置i/o3为高电平输出、i/o2为低电平输出,当需要控制继电器2触点闭合时,把i/o1设置为低电平,需要控制继电器触点断开时,把i/o1设置为高电平,从而控制继电器2线圈失电或得电,从而使得继电器2的一对常开触点关断或导通,从而实现对受控电路的控制。

[0108]

实施例4-6

[0109]

如图3所示,实施例4与实施例1的区别在于:所述三极管t1、三极管t2、三极管t3分别为pnp型、npn型、pnp型,所述三极管t1的集电极c1、发射极e1分别与继电器2线圈一端、第一供电端vcc对应电连接,所述三极管t2的集电极c2、发射极e2分别与继电器2线圈另一端、地gnd对应电连接。

[0110]

实施例5与实施例4的区别在于:所述三极管t1、三极管t2、三极管t3分别为pnp型、pnp型、npn型,所述三极管t1的集电极c1、发射极e1分别与三极管t2的发射极e2、第一供电端对应电连接,所述三极管t2的集电极c2通过继电器2线圈与地电连接。相应附图未给出,可类比图3得到。

[0111]

实施例6与实施例4的区别在于:所述三极管t1、三极管t2、三极管t3分别为npn型、npn型、pnp型,所述三极管t1的集电极通过继电器2线圈与第一供电端电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、地对应电连接。相应附图未给出,可类比图3得到。

[0112]

实施例7-12

[0113]

如图4所示,实施例7与实施例1的区别在于:所述第一开关管、第二开关管、第三开关管分别为mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3,各个mosfet场效应管的栅极(g1、g2、g3)分别为各个mosfet场效应管的控制端,所述mosfet场效应管q3的漏极d3、源极s3分别为mosfet场效应管q3的一个连接端、另一个连接端,且分别与q2的栅极g2、i/o2对应电连接,栅极g3与i/o3电连接。所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为n沟道增强型、p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极d1、源极s1分别与继电器2线圈一端、地gnd对应电连接,所述mosfet场效应管q2的漏极d2、源极s2分别与继电器2线圈另一端、第一供电端vcc对应电连接。

[0114]

实施例8与实施例7的区别在于:所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为n沟道增强型、n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、地对应电连接,所述mosfet场效应管q2的漏极通过继电器2线圈与第一供电端电连接。相应附图未给出,可类比图4得到。

[0115]

实施例9与实施例7的区别在于:所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为p沟道增强型、p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极通过继电器2线圈与地电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、第一供电端对应电连接。相应附图未给出,可类比图4得到。

[0116]

实施例10与实施例7的区别在于:所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为p沟道增强型、n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与继电器2线圈一端、第一供电端对应电连接,所述mosfet场效应管q2的漏极、源极分别与继电器2线圈另一端、地对应电连接。相应附图未给出,可类比图4得到。

[0117]

实施例11与实施例7的区别在于:所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为p沟道增强型、p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、第一供电端对应电连接,所述mosfet场效应管q2的漏极通过继电器2线圈与地电连接。相应附图未给出,可类比图4得到。

[0118]

实施例12与实施例7的区别在于:所述mosfet场效应管q1、mosfet场效应管q2、mosfet场效应管q3分别为n沟道增强型、n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极通过继电器2线圈与第一供电端电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、地对应电连接。相应附图未给出,可类比图4得到。

[0119]

本实用新型实施例中,p沟道增强型mosfet型号可采用安森美公司的fdn5618p,漏极电流(drain current)i

d

为-1.25a,漏极源极电压v

ds

为-60v。n沟道增强型mosfet型号可采用安森美公司的2n7002,漏极电流(drain current)i

d

为0.115a,漏极源极电压v

ds

为60v。q1、q2和q3增强型mosfet全部工作在开关状态,q1、q2和q3的漏极电流i

d

和漏极源极电压v

ds

在微处理器的弱电控制系统中足以满足要求。

[0120]

q1的栅极g1与第一i/o接口之间可设置第一电阻r1,q2的栅极g2与q3的漏极d3之间可设置第二电阻r2,q3的栅极g3与第三i/o接口之间可设置第三电阻r3。r1、r2、r3均可采用3k阻值的贴片电阻,将流入或流出微处理器i/o口的电流控制在4ma以下。

[0121]

实施例13

[0122]

本实施例13与实施例1的区别在于:

[0123]

所述开关管驱动单元为具有两个逻辑输入端、一个逻辑输出端的逻辑门电路,所

述逻辑门电路的一个逻辑输入端、一个逻辑输出端、另一个逻辑输入端分别为逻辑门电路的第一端、第二端、第三端。

[0124]

所述逻辑门电路的电路结构使得:

[0125]

(a2)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述逻辑门电路输出第一电平信号,从而令第二开关管关断;

[0126]

(b2)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述逻辑门电路输出第一电平信号,从而令第二开关管关断;

[0127]

(c2)当所述第二i/o接口、第三i/o接口的输出分别为高电平、低电平时,或当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平时,所述逻辑门电路输出第二电平信号;

[0128]

(d2)当所述逻辑门电路输出第二电平信号时,或当所述第一开关管导通且逻辑门电路输出第二电平信号时,所述第二开关管导通。

[0129]

所述第一开关管、第二开关管分别为三极管t1、三极管t2,各个三极管的基极b1、b2为各个三极管的控制端;

[0130]

本实施例13与实施例1的电路差别在于,利用图5(a)中各个元件代替图2(a)中微处理器1的i/o接口与m2点之间的器件。

[0131]

本实施例13中,所述三极管t1、三极管t2分别为npn型、pnp型,所述三极管t1的集电极、发射极分别与继电器2线圈一端、地对应电连接,所述三极管t2的集电极、发射极分别与继电器2线圈另一端、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门4。

[0132]

本实施例13中,通过三极管t1、三极管t2、逻辑异或非门4的结构及上述连接关系,使得:

[0133]

(a2)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述逻辑异或非门4输出为高电平,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0134]

(b2)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述逻辑异或非门4输出为高电平,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0135]

(c2)当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平或分别为高电平、低电平时,逻辑异或非门4输出为低电平。两个i/o接口存在差异说明微处理器1启动后已经完成了各个io接口的初始化过程,即此时不会受到微处理器刚启动时io接口电平不确定的影响,无需再利用与继电器2线圈串联的两个开关管起到保护作用;

[0136]

(d2)当所述逻辑异或非门4输出为低电平时,三极管t2导通。若i/o1输出高电平,则三极管t1导通。此时与继电器1线圈串联的两个开关管均导通,因此可利用i/o1的输出电平来控制继电器1一对常开触点的连通或关断。

[0137]

本实施例中,异或非门可采用hef4077b,异或门可采用74hct1g86。

[0138]

实施例14

[0139]

本实施例14与实施例1的电路差别在于,利用图5(b)中各个元件代替图2(b)中微处理器1的i/o接口与m1点之间的器件。

[0140]

本实施例14与实施例13的区别在于:所述三极管t1、三极管t2分别为npn型、npn

型,所述三极管t1的集电极、发射极分别与三极管t2的发射极、地对应电连接,所述三极管t2的集电极通过继电器2线圈与第一供电端vcc电连接,所述逻辑门电路为逻辑异或门3。

[0141]

本实施例14中,通过三极管t1、三极管t2、逻辑异或门3的结构及上述连接关系,使得:

[0142]

(a2)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述逻辑异或门3输出为低电平,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0143]

(b2)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述逻辑异或门3输出为低电平,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0144]

(c2)当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平或分别为高电平、低电平时,逻辑异或门3输出为高电平。两个i/o接口存在差异说明微处理器1启动后已经完成了各个io接口的初始化过程,即此时不会受到微处理器刚启动时io接口电平不确定的影响,无需再利用与继电器2线圈串联的两个开关管起到保护作用;

[0145]

(d2)当所述逻辑异或门3输出为高电平且三极管t1导通时,三极管t2导通。i/o1输出高电平时,即可利用三极管t1控制继电器2,即i/o1的输出信号令三极管t1导通,此时三极管t2导通也满足导通条件而导通,从而使得继电器1线圈所在回路导通,从而使得一对常开触点闭合。而如果i/o1的输出信号令三极管t1关断,则说明此时不希望受控电路导通,由于三极管t1关断、三极管t2关断,使得继电器1线圈所在回路无法接通,因此受控电路无法导通。

[0146]

实施例15

[0147]

本实施例15与实施例1的电路差别在于,利用图5(c)中各个元件代替图2(c)中微处理器1的i/o接口与m3点之间的器件。

[0148]

本实施例15与实施例13的区别在于:所述三极管t1、三极管t2分别为pnp型、pnp型,所述三极管t1的集电极通过继电器2线圈与地电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门4。

[0149]

本实施例15中,通过三极管t1、三极管t2、三极管t3的结构及上述连接关系,使得:

[0150]

(a2)当所述第二i/o接口、第三i/o接口的输出同为高电平时,所述逻辑异或非门4输出为高电平,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0151]

(b2)当所述第二i/o接口、第三i/o接口的输出同为低电平时,所述逻辑异或非门4输出为高电平,从而令三极管t2关断,使得继电器1的一对常开触点无法连通,从而避免在微处理器刚启动后因i/o的状态不确定且不受控出现的误动作;

[0152]

(c2)当所述第二i/o接口、第三i/o接口的输出分别为低电平、高电平或分别为高电平、低电平时,逻辑异或非门4输出为低电平。两个i/o接口存在差异说明微处理器1启动后已经完成了各个io接口的初始化过程,即此时不会受到微处理器刚启动时io接口电平不确定的影响,无需再利用与继电器2线圈串联的两个开关管起到保护作用;

[0153]

(d2)当所述逻辑异或非门4输出为低电平时,三极管t2导通。若i/o1输出低电平,则三极管t1导通。此时与继电器1线圈串联的两个开关管均导通,因此可利用i/o1的输出电

平来控制继电器1一对常开触点的连通或关断。

[0154]

实施例16-18

[0155]

实施例16与实施例13的区别在于:所述三极管t1、三极管t2分别为pnp型、npn型,所述三极管t1的集电极、发射极分别与继电器2线圈一端、第一供电端对应电连接,所述三极管t2的集电极、发射极分别与继电器2线圈另一端、地对应电连接,所述逻辑门电路为逻辑异或门3。相应附图未给出,可类比图4、图5(a)得到。

[0156]

实施例17与实施例13的区别在于:所述三极管t1、三极管t2分别为pnp型、pnp型,所述三极管t1的集电极、发射极分别与三极管t2的发射极、第一供电端对应电连接,所述三极管t2的集电极通过继电器2线圈与地电连接,所述逻辑门电路为逻辑异或非门4。相应附图未给出,可类比图4、图5(a)得到。

[0157]

实施例18与实施例13的区别在于:所述三极管t1、三极管t2分别为npn型、npn型,所述三极管t1的集电极通过继电器2线圈与第一供电端电连接,所述三极管t2的集电极、发射极分别与三极管t1的发射极、地对应电连接,所述逻辑门电路为逻辑异或门3。相应附图未给出,可类比图4、图5(a)得到。

[0158]

实施例19-24

[0159]

实施例19与实施例13的区别在于:所述第一开关管、第二开关管分别为mosfet场效应管q1、mosfet场效应管q2,各个mosfet场效应管的栅极分别为各个mosfet场效应管的控制端;所述mosfet场效应管q1、mosfet场效应管q2分别为n沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与继电器2线圈一端、地对应电连接,所述mosfet场效应管q2的漏极、源极分别与继电器2线圈另一端、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门4。相应附图未给出,可类比其他附图得到。

[0160]

实施例20与实施例19的区别在于:所述mosfet场效应管q1、mosfet场效应管q2分别为n沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、地对应电连接,所述mosfet场效应管q2的漏极通过继电器2线圈与第一供电端电连接,所述逻辑门电路为逻辑异或门3。相应附图未给出,可类比其他附图得到。

[0161]

实施例21与实施例19的区别在于:所述mosfet场效应管q1、mosfet场效应管q2分别为p沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极通过继电器2线圈与地电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、第一供电端对应电连接,所述逻辑门电路为逻辑异或非门4。

[0162]

实施例22与实施例19的区别在于:所述mosfet场效应管q1、mosfet场效应管q2分别为p沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极、源极分别与继电器2线圈一端、第一供电端对应电连接,所述mosfet场效应管q2的漏极、源极分别与继电器2线圈另一端、地对应电连接,所述逻辑门电路为逻辑异或门3。相应附图未给出,可类比其他附图得到。

[0163]

实施例23与实施例19的区别在于:所述mosfet场效应管q1、mosfet场效应管q2分别为p沟道增强型、p沟道增强型,所述mosfet场效应管q1的漏极、源极分别与mosfet场效应管q2的源极、第一供电端对应电连接,所述mosfet场效应管q2的漏极通过继电器2线圈与地电连接,所述逻辑门电路为逻辑异或非门4。相应附图未给出,可类比其他附图得到。

[0164]

实施例24与实施例19的区别在于:所述mosfet场效应管q1、mosfet场效应管q2分

别为n沟道增强型、n沟道增强型,所述mosfet场效应管q1的漏极通过继电器2线圈与第一供电端电连接,所述mosfet场效应管q2的漏极、源极分别与mosfet场效应管q1的源极、地对应电连接,所述逻辑门电路为逻辑异或门3。相应附图未给出,可类比其他附图得到。

[0165]

需要说明的是,本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

[0166]

以上对本实用新型的实施例进行了详细说明,但所述内容仅为本实用新型的较佳实施例,不能被认为用于限定本实用新型的实施范围。凡依本实用新型范围所作的均等变化与改进等,均应仍归属于本专利涵盖范围之内。在阅读了本实用新型之后,本领域技术人员对本实用新型的各种等价形式的修改均落入本申请所附权利要求所限定的范围。在不冲突的情况下,本实用新型中的实施例及实施例中的特征可以相互组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1