一种防射频干扰的电路板的制作方法

1.本实用新型涉及pcb电路板技术领域,更具体的涉及一种防射频干扰的电路板。

背景技术:

2.在家用电器、工业自动化、生产过程控制、智能仪器仪表等智能设备装置中,其pcb电路板上设有各种各样的通过电或磁彼此紧密连接又相互影响的电子元器件,在这些电子元器件中又包含了大量的具备射频收发功能的、可相互产生电磁及射频干扰的电子元器件。因此,智能设备其pcb电路板若不进行适当的防电磁、射频干扰处理,可能造成整个电路系统无法正常工作,在实际使用过程中会因为运行方式的改变、故障、开关操作及其他电器设备的近距离使用等引起的电磁震荡而影响pcb电路板上各电子元器件的正常运行,致使智能设备的控制误差加剧,干扰严重时还会导致智能设备失灵,进而造成使用者经济损失。

3.另外,随着移动终端的普及,市场竞争日趋白热化,在优胜劣汰的市场环境下,智能设备pcb电路板的性价比显得尤为重要,在降低成本和提升性能方面,各大制造厂商各显神通。为了压缩生产成本,很多智能终端设计厂商采用各种方式,降低成本,提升生产效率。在此背景下,部分智能设备的pcb电路板采用正面贴片、背面插件式焊接电子元器件的方式进行生产。这种设计能够带来贴片便利,从而大幅减低生产制造成本。但同时因其为一面贴片、另一面插件的结构,导致了智能设备的pcb电路板本体布线困难,容易因布线设置的原因出现射频指标干扰问题,进而影响智能设备整体的emc性能,出现如信号弱、信号干扰严重等的棘手问题。

4.此种问题的传统解决方案,就是分别为多个如高频放大、混频、调解、本振等具有射频干扰的模块电路提供一个公共电位参考点,即接地端子,然后将相应的接地端子逐个拉导电布接地,通过将分散于pcb电路板上的接地端子分别接地的方式以将干扰信号消除。但是,由于接地端子为分散式分布,在将接地端子逐个拉导电布接地时所需辅料太多,且要注意避开电路板本体上的导线,实际操作步骤繁杂,造成pcb电路板的生产组装成本过高,其性能一致性也得不到有效保障。

5.因此,在保障智能设备pcb电路板单面贴片的成本优势及方便装配的前提下,需要对智能设备的pcb电路板进行改进,以简化其防射频干扰处理的繁杂步骤,减少所需辅料,防止和抑制电磁干扰,提高电磁兼容性emc,避免因射频干扰导致智能设备出现故障及失灵。

技术实现要素:

6.综上所述,本实用新型的目的在于解决现有智能设备的pcb电路板其防射频干扰的结构设计不合理、emc性能差及生产组装成本高的技术不足,而提供防射频干扰效果更好、生产组装成本更低的一种防射频干扰的电路板。

7.为实现上述目的,本实用新型采用了下述技术方案:

8.一种防射频干扰的电路板,包括有电路板本体,所述电路板本体的正面焊接有贴

片式电子元器件,电路板本体的背面焊接有插件式电子元器件,所述的贴片式电子元器件与插件式电子元器件皆与电路板本体电性连接。所述电路板本体的背面设有两个以上起屏蔽作用的接地端子,电路板本体背面的非接地端子区域覆盖有绝缘油墨。电路板本体的背面整面粘贴有覆于所述绝缘油墨及接地端子上的、形状尺寸与电路板本体相匹配的导电布,且导电布上预留有避开所述插件式电子元器件的电子元器件避空位,导电布将所述的接地端子电性连接成一个整体,形成一个整层的gnd环境。

9.所述的导电布包括有纤维布基材,所述纤维布基材的内侧面整面粘贴有导电背胶,导电布经所述的导电背胶对应粘贴在所述电路板本体背面的绝缘油墨和接地端子上。

10.所述的导电布上预留有避开所述电路板本体上开设的安装孔的安装孔避空位。

11.所述电路板本体的背面设有覆铜膜,所述覆铜膜经蚀刻工艺处理形成导线和所述的接地端子,接地端子分散处于所述导线的空隙区域。

12.所述的绝缘油墨为绿油。

13.本实用新型的有益效果为:本实用新型在确保电路板正面贴片、背面插件的低成本生产方式的同时,通过整面粘贴于所述电路板本体背面的导电布将分散处于其背面两个以上的接地端子电性连接为一个整体,形成一个整层的总地线gnd环境,形成的总地线只存在一个电位参考点,因此没有公共阻抗耦合的存在,解决了各模块电路的相互干扰的问题,提高了电路板整体的电磁兼容性(emc),有效防止和抑制了电磁干扰及射频干扰。而且,相较于传统智能设备pcb电路板解决射频干扰问题的逐个拉导电布接地的方式,本实用新型将多个分散布局且形状各异的导电布优化集合成一个与电路板本体形状尺寸相匹配的导电布,简化了防射频干扰处理的繁杂步骤,有效减少了防射频干扰处理所需的辅料,降低了智能设备其pcb电路板生产组装的成本,且提高了电路板生产组装的效率。

附图说明

14.图1为本实用新型电路板本体背面整体结构示意图;

15.图2为本实用新型导电布整体结构示意图;

16.图3为本实用新型导电布的横截面结构示意图;

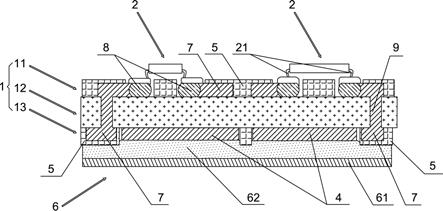

17.图4为本实用新型电路板本体整体结构横截面示意图其一;

18.图5为本实用新型电路板本体整体结构横截面示意图其二。

19.图中:1.电路板本体,11.正面布线层,12.绝缘层,13.背面布线层,14.安装孔,2.贴片式电子元器件,21.接线端子,3.插件式电子元器件,31.插脚,4.接地端子, 5.绝缘油墨,6.导电布,61. 纤维布基材,62. 导电背胶,63. 电子元器件避空位,64. 安装孔避空位,7. 导线,8. 焊盘,9.过孔。

具体实施方式

20.以下结合附图和本实用新型优选的具体实施例对本实用新型的结构作进一步地说明。

21.参照图1至图5所示,本实用新型:

22.一种防射频干扰的电路板,包括有电路板本体1,电路板本体1的上部正面上焊接有多个贴片式电子元器件2,电路板本体1的下部背面上焊接有多个插件式电子元器件3,贴

片式电子元器件2和插件式电子元器件3皆与电路板本体1电性连接。在电路板本体1的背面上设有多个分散布置的、起屏蔽作用的接地端子4,电路板本体1背面的非接地端子区域覆盖有绝缘油墨5。在电路板本体1的背面上还整面粘贴有一块与电路板本体1背向形状尺寸相匹配的导电布6,在该导电布6上对应预留有避开插件式电子元器件3的电子元器件避空位63。本实用新型通过一整块导电布6将电路板本体1背面的所有接地端子4电性连接成一个整体,形成一个整层的gnd环境以消除智能设备pcb电路板的射频干扰问题。

23.具体的,为了降低智能设备其pcb电路板生产制造的成本,同时降低电路板本体1布线的难度,本实施例中的电路板本体1优选的采用双面布线电路板结构。当然了,在其它一些实施例中也完全可以采用如单面板或者多层板的电路板结构。采用单面板结构的电路板虽然制作成本更低,但是其存在布线困难、防射频干扰能力差的弊端;而采用多层板虽然有利于布线及提高抗干扰能力,但是其制作工艺复杂,制作成本高,不利于降低产品成本。

24.具体的,双面布线电路板本体1的结构由上向下包括有正面布线层11、绝缘层12和背面布线层13。其中,正面布线层11和背面布线层13主要包括由铺设在绝缘层12上下两面上的覆铜膜经蚀刻工艺处理后形成的导线7。

25.需要说明的是,为了抑制电路板本体1正面上焊接的贴片式电子元器件2间的电磁干扰、屏蔽其他用电设备对本实用新型电路板本体1上电子元器件的射频干扰,以及屏蔽本实用新型电路板本体1上的电子元器件向外发射电磁或射频干扰,本实用新型背面布线层13的覆铜膜在设计其导线7时,还设计有多个对应具有射频干扰的贴片式电子元器件2的大面积露铜区,此处所述的露铜区即为本实用新型电路板本体1背面上的接地端子4,且各接地端子4皆位于背面布线层13其导线7的空隙区域内,以起到屏蔽及抑制电路板本体1射频干扰的作用。

26.具体的,处于电路板本体1中间的绝缘层12由绝缘材料制成,优选的可采用玻纤布加树脂材料制作,其厚度可依据实际需求进行相应调整。

27.为了提高本实用新型电路板整体的电磁兼容性,在安排具有射频干扰的电子元器件如cpu处理器、ic集成电路等的具体位置时,应避免其距离过近。同时在设计背面布线层13的导线7时应配合电路板本体1正面贴装的具有射频干扰的电子元器件的具体位置,来设计接地端子4的相应位置,使各接地端子4分散在电路板本体1的背面上且与相应的具有射频干扰的电子元器件相对应。另外,应使接地端子4的覆盖面积尽量大些,以提高屏蔽效果。

28.常用的双面布线电路板其正面布线层11和背面布线层13上的导线7经焊盘8及过孔9电性连接,贴片式电子元器件2及插件式电子元器件3对应焊接在相应的焊盘8及过孔9上以实现与导线7的电性连接。

29.具体的,在电路板本体1上设有多个用于焊接贴片式电子元器件2及插件式电子元器件3的焊盘8以及与焊盘8配合使用的过孔9。在电路板本体1上还设有多个用于固定安装的安装孔14,安装孔14是上下贯穿电路板本体1的非镀通孔,其本身并不与正面布线层11及背面布线层13的导线7电性连接。

30.具体的,参照图4及图5所示,电路板本体1的上部正面通过smt工艺焊接有多个贴片式电子元器件2,每个贴片式电子元器件2上皆设有至少两个的接线端子21,接线端子21分别对应焊接在焊盘8上,同时焊盘8分别焊接在正面布线层11的两根相互靠近的导线7上。在其中一个焊接有焊盘8的正面布线层11的导线7上连接有一竖直贯穿绝缘层12以使正面

布线层11的导线7与背面布线层13的导线7电性连接的过孔9,贴片式电子元器件2通过焊盘8、正面布线层11的导线7及过孔9与背面布线层13的导线7电性连接。在电路板本体1的背面上对应设有与具有射频干扰的如cpu等的贴片式电子元器件2配合使用的接地端子4,且接地端子4完全覆盖住与其相对应的贴片式电子元器件2,以起到屏蔽保护的作用。

31.本实用新型的电路板本体1在其背面设置的接地端子4,可以分别对不同贴片式电子元器件2或模块电路进行单独接地,可有效降低接地阻抗,也可降低共模干扰,避免相邻贴片式电子元器件2间的窜扰,提高了本实用新型的电磁兼容性能。

32.具体的,smt工艺要素包括丝印、点胶、贴装、固化、回流焊接、清洗、检测及返修。首先采用丝印机、smt贴片钢网将焊膏及贴片胶漏印到电路板本体1正面的相应位置上,注意应使焊膏准确对应漏印到相应导线7的焊盘8上,为贴片式电子元器件2的焊接做准备。然后通过点胶机将胶水滴到绝缘层12上表面的固定位置上以便于将贴片式电子元器件2粘接固定在电路板本体1上。然后通过贴片机将表面贴装的贴片式电子元器件2准确安装到电路板本体1正面的相应位置上。然后通过固化炉将贴片胶融化,使贴片式电子元器件2牢固地粘接在绝缘层12上。然后通过回流焊炉将焊膏融化,使贴片式电子元器件2经焊膏与相应的焊盘8络牢固地粘接在一起,并通过正面布线层11的导线7及过孔9与电路板本体1背面布线层13的导线7电性连接在一起。然后通过清洗机将贴装好贴片式电子元器件2的电路板本体1上焊接残留物如助焊剂等除去。清洗后对电路板本体1的贴片式电子元器件2焊接质量进行检测并测试,对不合格产品进行返工。

33.需要说明的是,为了保护正面布线层11、便于贴片式电子元器件2的贴装及插件式电子元器件3的后续插装及焊接,在smt表面贴装工艺之前需要将电路板本体1的正面整层涂布起保护电路板本体1及导线7作用的绝缘油墨5。该处涂布的绝缘油墨5行业内通常选用红胶,并在smt贴装前涂布在电路板本体1正面的正面布线层11上。需要注意的是,在涂布红胶时应注意避开电路板本体1正面上的焊盘8以免影响后续smt表面贴装工艺及插件式电子元器件3焊接的正常进行。

34.具体的,参照图4及图5所示,在电路板本体1的背面上同样整层涂有起保护电路板本体1及导线7作用的绝缘油墨5。优选的,此处使用的绝缘油墨5行业内通常选用成本较低的绿油。通过绿油将电路主板背面除了接地端子4以外的部分完全覆盖起来,以起到保护背面布线层13导线7的作用。

35.应注意的是,在涂布绿油时应注意避开电路板本体1背面上的焊盘8以免影响插件式电子元器件3的正常插装。

36.在电路板本体1的正面上焊接好贴片式电子元器件2后,再将如开关按键、接口等具有长引脚的插件式电子元器件3手动或自动插装在电路板本体1的背面上并焊接。

37.具体的,参照图1及图4所示,本实用新型电路板本体1的背面上焊接有多个插件式电子元器件3,每个插件式电子元器件3上都设有至少两个的插脚31,插脚31从电路板本体1的背面向上对应插接到相应的过孔9内。每个用于插装插件式电子元器件3插脚的过孔9皆上下贯穿电路板本体1,每个过孔9的上、下开口处皆连接有焊盘8,同时焊盘8又分别与上层布线层11及下层布线层13上的导线7电性连接,以实现插件式电子元器件3与上层布线层11及下层布线层导线7间的电性连接。

38.实际插装后,将插件式电子元器件3经过孔9伸出到电路板本体1正面上方的插脚

31多余部分手工剪切或切脚机自动剪切,使插脚31恰好部分漏出过孔9上端的焊盘8处即可。而后通过手工焊接或者浸焊炉自动焊接将插脚31与相应的焊盘8及过孔9焊接在一起,使插件式电子元器件3牢固地焊接在电路板本体1的背面上,并通过插脚31、背面布线层13的导线7及相应的过孔9、焊盘8将插件式电子元器件3与电路板本体1正面布线层11的导线7电性连接在一起。

39.需要说明的是,在插装插件式电子元器件3并焊接之前,涂布在电路板本体1正面上的绝缘油墨5已经避开了焊盘8,因此,在将插件式电子元器件3的插脚上端部焊接在相应的焊盘8及过孔9上时并不会影响正面布线层11其导线7与背面布线层13导线7之间的电性连接。在插件式电子元器件3焊接在电路板本体1的背面后,整个电路板本体1的背面凸出的部件只有插件式电子元器件3,其它部分都基本呈平面状。而且,电路板本体1背面上涂布的绝缘油墨5较薄,明显薄于背面布线层13的导线7及接地端子4的厚度,因此涂布绿油后,其端面并不明显超出未涂布绿油的接地端子4的端面,以保证导电布6能够有效粘贴在接地端子4上。

40.在将插件式电子元器件3插装到电路板本体1背面上后,根据电路板本体1背面整体的形状及结构,设计一个可整面覆盖粘贴在电路板本体1背面上的导电布6。具体的,导电布6包括有纤维布基材61,在纤维布基材61朝向背面布线层13的内侧面上整面粘贴有导电背胶62,导电布6通过导电背胶62整面粘贴固定在电路板本体1的背面上。

41.应注意的是,由于电路板本体1的背面上只焊接有插件式电子元器件3,因此,在设计导电布6时需开设用于避开插件式电子元器件3的电子元器件避空位63,防止粘贴时插件式电子元器件3阻碍导电布6的整面粘贴,同时也是为了避免导电布6粘贴后导电背胶62接触插件式电子元器件3的焊接点将插件式电子元器件3短接。另外需注意的是,在电路板本体1上还设有安装孔14,因此导电布6需对应开设避开安装孔14的安装孔避空位64,防止粘贴后导电布6将安装孔14堵塞。

42.然后,将导电布6通过导电背胶62对应粘贴在电路板本体1的背面上,电路板本体1通过导电背胶62将其背面上的所有接地端子4电性连接成一个整体,使整个导电布6形成一个整层的总地线gnd环境。形成的总地线只存在一个电位参考点,因此没有公共阻抗耦合的存在,进一步解决了各电子元器件间相互干扰的问题,提高了本实用新型电路板本体1的电磁兼容性emc,有效防止和抑制了电磁干扰及射频干扰。

43.而且,相较于传统智能设备pcb电路板解决射频干扰问题的将各接地端子4逐个拉导电布6接地的方式,本实用新型将多个分散布局且形状各异的导电布6优化集合成一个与电路板本体1整体形状尺寸相匹配的导电布6,简化了防射频干扰处理的繁杂步骤及辅料,降低了电路板本体1生产组装的成本,提高了智能设备pcb电路板生产组装的效率。

44.优选的,本实用新型选用的导电布6其性能指标如下:

45.厚度:0.11

±

5%mm,表面阻抗(25.4mm*50mm):≤0.04ω/sq,耐热温度:≥110℃,屏蔽性能(10mhz-3ghz):≥75 db,抗磨损:500000次,金属结合力:≥3级grade。

46.另外,为了验证本实用新型电路板整体防射频干扰的性能,做了对比检测,结果如下:

[0047][0048]

从此表中可直观的看出改进后的本实用新型电路板在各频段的抗射频干扰的能力明显高于改进前的,证明了本实用新型电路板是能够带来显著防射频干扰的技术效果的。

[0049]

虽然结合附图对本实用新型的具体实施方式进行了详细地描述,但不应理解为对本实用新型的保护范围的限定。在权利要求书所描述的范围内,本领域技术人员不经创造性劳动即可做出的各种修改和变形仍属于本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1