一种双电源CML结构时钟驱动电路的制作方法

一种双电源cml结构时钟驱动电路

技术领域

1.本实用新型涉及于航空、航海和工业控制等信号通信领域,尤其涉及一种双电源cml结构时钟驱动电路。

背景技术:

2.不同电源电压时采用固定的cml电路结构。cml电路传统结构如图1所示,当vip为高、vin为低时,m1导通,m2截止。vop电压为vdd,von电压为 vdd

‑

ibias*ro,输出电压摆幅为ibias*ro与尾电流大小直接相关,考虑到与信道的匹配,cml内部上拉电阻为50ω,设计输出信号摆幅的特征值为0.75v时,尾电流为15m。电路工作电压为2.5v/3.3v,要求cml电路输出共模为vdd

‑

0.4,摆幅为0.6~1v。

3.在实际的设计和应用中,在3.3v电压下正常工作的bandgap电路在2.5v 工作时会受到压降的影响,进而影响内部的电流、输出信号幅度等关键性能指标。在3.3v正常工作的电路,当电源电压变为2.5v时,基准电流太小,导致输出信号摆幅不能满足设计指标要求。在2.5v正常工作的电路,当电源为3.3v 时,基准电流过大,导致输出信号摆幅超出设计指标范围,同时电路功耗过大。

技术实现要素:

4.本实用新型为解决背景技术中存在的上述技术问题,提供了一种双电源 cml结构时钟驱动电路,同时实现在2.5v和3.3v两种电压下的电路功能。

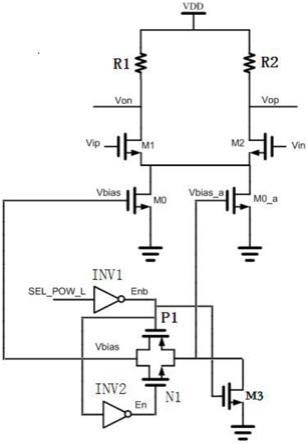

5.本实用新型的技术解决方案是:本实用新型为一种双电源cml结构时钟驱动电路,所述驱动电路包括nmos管m1、nmos管m2和nmos管m0,nmos管 m1和nmos管m2的源端分别接nmos管m0的漏端,nmos管m0的源端接地,其特殊之处在于:所述驱动电路还包括nmos管m0_a、nmos管n1、pmos管p1、反相器inv1和反相器inv2,反相器inv1的输出接反相器inv2的输入,同时接pmos管p1的栅极;反相器inv2的输出接nmos管n1的栅极;nmos管n1的源端接pmos管p1的漏端,同时接nmos管m0的栅极,nmos管n1的漏端接pmos 管p1的源端,同时接nmos管m0_a的栅极,nmos管m0_a的漏端接nmos管m1 和nmos管m2的源端,nmos管m0_a的源端接地。

6.优选的,驱动电路还包括nmos管m3,nmos管n1的漏端和pmos管p1的源端分别通过nmos管m3接地,nmos管m3的栅极接pmos管p1的栅极。

7.本实用新型的双电源cml结构时钟驱动电路,在现有的cml电路的基础上增加了nmos管m0_a、nmos管n1和pmos管p1,通过电源判决的使能信号控制尾电流管的个数,从而控制不同电源电压时的尾电流的大小;在电源电压3.3v 正常工作时,加大了2.5v工作时的尾电流,使得低电源下信号输出摆幅满足指标要求。在2.5v工作正常时,减小了高电源3.3v工作时的尾电流,降低了模块的电流功耗。因此,本实用新型在一个电路下,同时实现在2.5v和3.3v两种电压下的电路功能。

附图说明

8.图1是现有的cml电路结构图;

9.图2是本实用新型的电路原理图。

具体实施方式

10.在实际的设计和应用中,在3.3v电压下正常工作的bandgap电路在2.5v 工作时会受到压降的影响,进而影响内部的电流、输出信号幅度等关键性能指标。在低电压工作时对关键电路和指标进行补偿,使得在2.5v和3.3v及相应的电压波动下,保证电路的输出信号质量

11.在高电源电压3.3v时bandgap输出的基准电流iunit_h为300ua,此时15ma 尾电流设计由基准电流iunit_h的50倍电流镜实现。cml电路内部上拉电阻为 50ω,输出信号摆幅为0.75v。

12.在2.5v电压下bandgap输出的基准电流iunit_l只有260ua,50倍电流镜后的理想尾电流为12m,此时摆幅为0.6v,已是输出信号摆幅要求的下限。在电路实际的工作过程中电流镜的存在偏差,尾电流值可能偏小,同时考虑到上拉电阻随着工艺的偏差,管尾电电流无法满足设计要求,不能保证输出信号的摆幅满足要求。若要满足15m的尾电流要求,电流镜倍数必须为60。

13.因此在低电源电压2.5v工作时,考虑在现有的驱动电路设计中增加一组控制开关nmos管m0_a,通过控制使能信号使电路在2.5v电源电压下工作时增加 nmos管的个数,即增大电流镜相的倍数,适当的增大尾电流,保证2.5v电源电压下,输出时钟共模及增益满足设计要求。

14.下面结合附图和具体实施例对本实用新型的技术方案做进一步详细描述。

15.参见图2,本实用新型的具体实施例的电路采用3.3v的mos管器件完成电路设计,同时实现在2.5v和3.3v两种电压下的电路功能。其结构包括电源vdd、 nmos管m1、nmos管m2、nmos管m0、nmos管m0_a、nmos管m3、电阻r1、电阻r2、nmos管n1、pmos管p1、反相器inv1和反相器inv2,电源vdd分别通过电阻r1和电阻r2接nmos管m1和nmos管m2的漏端,nmos管m1和nmos管 m2的源端分别接nmos管m0的漏端,nmos管m0的源端接地,nmos管m1和nmos 管m2的源端还分别接nmos管m0_a的漏端,反相器inv1的输出接反相器inv2 的输入,同时接pmos管p1的栅极;反相器inv2的输出接nmos管n1的栅极; nmos管n1的源端接pmos管p1的漏端,同时接nmos管m0的栅极,nmos管n1 的漏端接pmos管p1的源端,同时接nmos管m0_a的栅极,nmos管m0_a的漏端接nmos管m1和nmos管m2的源端,nmos管m0_a的源端接地,nmos管n1 的漏端和pmos管p1的源端分别通过nmos管m3接地,nmos管m3的栅极接pmos 管p1的栅极。

16.本实用新型的工作原理如下:通过电源内部分压与内部基准电压进行比较,用逻辑电路来判断当前芯片的上电情况及工作电压,输出控制信号sel_pow_l,分别通过反相器inv1和反相器inv2输入pmos管p1和nmos管n1。当vdd=3.3v 时,输出控制信号sel_pow_l=0,pmos管p1和nmos管n1关断,vbias_a=0, nmos管m0_a关断,nmos管m0提供50*iunit_h的尾电流。当vdd=2.5v时,输出控制信号sel_pow_l=1,pmos管p1和nmos管n1导通,vbias_a=vbias,此时nmos管m0和nmos管m0_a均打开,nmos管m0提供50*iunit_l的尾电流,nmos管m0_a提供10*iunit_l的尾电流,总电流为60*ibias_l,电流叠加增大,输出摆幅增大。满足

指标要求。

17.最后应说明的是:以上实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述实施例对本实用新型进行了详细地说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1