基于低功率反相器的CTLE的制作方法

基于低功率反相器的ctle

技术领域

1.本公开的示例总体上涉及电子电路,并且具体地涉及基于低功率反相器的连续时间线性均衡器(ctle)。

背景技术:

2.连续时间线性均衡器(ctle)是用于信号均衡的有线接收器前端的核心模拟构建块。已经研究了各种ctle架构以优化功率、面积和性能。传统的ctle电路采用电流模式逻辑(cml)电路。最近,ctle设计专注于基于反相器的电路,因为与基于cml的设计相比,其芯片面积更小。然而,基于反相器的设计的功率和性能取决于它们的拓扑结构、反相器的数量和尺寸以及它们的线性度。需要为ctle提供基于低功率反相器的设计。

技术实现要素:

3.描述了包括连续时间线性均衡器(ctle)的电子器件和用于提供基于低功率反相器的ctle的技术。在一个示例中,被配置为连续时间线性均衡器(ctle)的电子器件包括:第一反相器;第二反相器,具有输入端以接收输入信号;电容器,被耦接在第一反相器的输入端和第二反相器的输入端之间;电阻器,被耦接在共模电压与第一反相器的输入端之间;第三反相器,具有输出端以提供输出信号;节点,包括第一反相器的输出端、第二反相器的输出端、第三反相器的输入端、和第三反相器的输出端。

4.在另一示例中,配置为接收器的电子器件包括具有连续时间线性均衡器(ctle)的前端电路和耦接到前端电路的数字后端电路。ctle包括:第一反相器;第二反相器,具有输入端以接收输入信号;电容器,被耦接在第一反相器的输入端和第二反相器的输入端之间;电阻器,被耦接在共模电压与第一反相器的输入端之间;第三反相器,具有输出端以提供输出信号;节点,包括第一反相器的输出端、第二反相器的输出端、第三反相器的输入端、和第三反相器的输出端。

5.在另一示例中,配置为连续时间线性均衡器(ctle)的电子器件包括:第一反相器;第二反相器,具有输入端以接收输入信号;电容器,被耦接在第一反相器的输入端和第二反相器的输入端之间;第一电阻器,被耦接在共模电压与第一反相器的输入端之间;第三反相器;节点,包括第一反相器的输出端、第二反相器的输出端、第三反相器的输出端,所述节点提供输出信号;

6.和第二电阻器,耦接在第三反相器的输入端和节点之间。

7.这些和其他方面可以参考以下详细描说明来理解。

附图说明

8.为了可以详细理解以上列举的特征的方式,可以通过参考示例实现来获得以上简要概括的更具体的描述,其中一些示例实现在附图中示出。然而,要指出的是,附图仅说明了典型的示例实施方式,因此不应被认为是对其范围的限制。

9.图1是描绘根据示例的接收器的框图;

10.图2是描绘根据现有技术的ctle的示意图;

11.图3是描绘根据现有技术的ctle的示意图;

12.图4是描绘根据示例的图1的ctle的示意图;

13.图5是图4的ctle的传递函数的图;

14.图6是描绘根据另一示例的ctle的示意图;

15.图7是图6的ctle的传递函数的图;

16.图8是描绘根据另一示例的ctle的示意图;

17.图9是描绘根据另一示例的ctle的示意图;

18.图10是描绘根据示例的用于本文描述的ctle电路的vcm发生器的示意图;

19.图11是描绘根据另一示例的ctle的示意图;

20.图12a是描绘根据示例的可编程器件的框图;

21.图12b是描绘根据示例的可编程ic的框图;

22.图12c示出了根据示例的可编程ic的现场可编程门阵列(fpga)实现方案。

23.为了便于理解,在可能的情况下,使用了相同的附图标记来表示附图共有的相同元件。预期一个示例的单元可以有益地结合到其他示例中。

具体实施方式

24.下文参照附图描述各种特征。应当注意,附图可以或可能不按比例绘制,并且相似结构或功能的元件在所有附图中由相似的附图标记表示。应注意,附图仅旨在便于对特征的描述。它们不旨在作为要求保护的发明的详尽描述或作为对要求保护的发明范围的限制。此外,图示的示例不需要具有所示的所有方面或优点。结合特定示例描述的方面或优点不一定限于该示例并且可以在任何其他示例中实践,即使未如此说明或即使未此明确描述。

25.图1是描绘配置为根据示例提供的接收器100的电子器件的框图。接收器100包括前端电路102和数字后端电路104。前端电路102包括连续时间线性均衡器(ctle)106以及其他组件(例如,自动增益控制电路、滤波器、可以是与ctle 106相同或不同的其他ctle等等)。数字后端电路104包括用于处理前端电路102输出的模拟信号的各种电路(例如,采样器、模数转换器(adc)、判决反馈均衡器(dfe)电路、时钟和数据恢复电路等等)。ctle 106接收输入信号并作为高通滤波器操作以补偿提供输入信号的传输介质的低通特性。ctle 106的峰值幅度和频率响应的位置都可以通过前端电路102和/或数字后端电路104中的控制电路进行调整。下面描述ctle 106的示例实现。

26.图2是描绘根据现有技术的ctle 200的示意图。这样的电路在2018年ieee集成电路会议(cicc)zheng,kevin等人发表的“a 56gb/s 6mw 300um2 inverter-based ctle for short-reach pam2 applications in 16nm cmos”中所描述。ctle 200包括反相器202、204、208和210以及电容器206。反相器202和204的输入端被耦接以接收输入信号(in)。反相器202的输出端被耦接到节点x。反相器204的输出端被耦接到节点y。电容器206被耦接在节点x和y之间。反相器208的输入端和输出端都被耦接到节点x。反相器210的输入端和输出端都被耦接到节点y。反相器210的输出端提供输出信号(out)。

27.假设反相器204具有跨导gm1,反相器202具有跨导gm2,反相器208和210具有跨导gm

l

,电容器206具有电容c

hf

。ctle 200是一种基于反相器的ctle,并使用了加法拓扑。峰值是通过将gm2添加到通过电容器206的高频信号路径(产生“加法”拓扑)而实现的。低频增益(g1)、高频增益(g2)和峰值由以下等式定义:

28.g1=gm1/gm

l

29.g2=(gm1+gm2)/(2*gm

l

)

30.峰值(peaking)(db)=20*log[(gm1+gm2)/2*gm1]

[0031]

低频和高频的边界由c

hf

和gm

l

确定。

[0032]

图3是描绘根据现有技术的ctle 300的示意图。图3的ctle使用减法拓扑,例如在2018年ieee集成电路电路会议(cicc)zheng、kevin等人发表的“an inverter-based analog front end for a 56gb/s pam4 wireline transceiver in 16nm cmos”中所描述。ctle300包括反相器302、304、306、308和310以及电容器312。反相器302和308的输入端被耦接以接收输入信号(in)。反相器302的输出端被耦接到:反相器304的输入端、反相器304的输出端和反相器306的输入端(称为节点314)。反相器306的输出端被耦接到:反相器308的输出端、反相器310的输入端和反相器310的输出端(称为节点316)。节点316提供输出信号(out)。

[0033]

假设反相器302具有跨导gma,反相器304具有跨导gmb,反相器306具有跨导gm2,反相器308具有跨导gm1,并且反相器310具有跨导gm

l

。对于ctle 300,g1、g2和峰值由以下等式定义:

[0034]

g1=(gm1/gm

l

)

–

(gma/gmb)*(gm2/gm

l

)

[0035]

g2=gm1/gm

l

[0036]

峰值(db)=20*log[(gmb*gm1)/(gmb*gm

1-gma*gm2)]

[0037]

低频和高频的边界由chf和gmb决定。

[0038]

尽管基于反相器的ctle设计在面积消耗方面很有吸引力,但其功率是主要的设计问题。需要的均衡越激进(aggressive),ctle消耗的功率就越多。基于反相器的ctle的另一个设计问题是线性度,它会影响信噪失真比(sndr)。为了说明功耗估计,假设g1=0db,g2=6db,这会产生6db峰值。

[0039]

考虑图2所示的加法拓扑。在这种情况下:

[0040]

g1=gm1/gm

l

=1(0db)

[0041]

g2=(gm1+gm2)/(2*gm

l

)=2(6db)

[0042]

gm1=gm

l

[0043]

gm2=3*gm

l

[0044]

总计gm=gm1+gm2+2*gm

l

=gm

l

+3*gm

l

+2*gm

l

=6*gm

l

[0045]

因此,反相器202的跨导为3*gm

l

,在本例中,反相器204的跨导为gm

l

。总器件漏极寄生电容约为6*cdd;总器件栅极寄生电容约为2*cgg,其中cdd和cgg分别是具有gm

l

的跨导的反相器的漏极和栅极电容。由于节点x和节点y之间的共模失配,图2的加法拓扑存在线性问题。由于电容c

hf

和两个不同的gm

l

反相器,节点x和节点y处的直流偏置条件不相同。更具体地说,当所有器件完美匹配时,反相器的偏置条件实际上是相同的。然而,当输入摆幅出现时,就会存在非线性。在此拓扑中,顶部路径需要3x(gm2/gm

l

=3)的增益才能实现6db峰值。

在这种情况下,当输入摆幅较大时,顶部路径可能会饱和。这将导致反相器与底部路径相比具有非常不同的大信号偏置。

[0046]

在图3的减法拓扑中,再次假设g1=0db,g2=6db,这会产生6db的峰值。在这种情况下:

[0047]

(1)g1=(gm1/gm

l

)

–

(gma/gmb)*(gm2/gm

l

)=1(0db)

[0048]

(2)g2=gm1/gm

l

=2(6db)-》gm1=2*gm

l

[0049]

(3)从(1),gm1–

(gma/gmb)*gm2=gm

l

[0050]

从(2)和(3),gm2=(gmb/gma)*gm

l

[0051]

总计gm=gm1+gm2+gm

l

=2*gm

l

+(gmb/gma)*gm

l

+gm

l

=3*gm

l

+(gm

b-/gma)*gm

l

[0052]

如果gma=gmb,则gm总计是4*gm

l

[0053]

为了与图2的加法拓扑进行公平比较,就增益带宽积而言,图3的减法拓扑的gm

l

应加倍(例如,2*gm

l

)。因此,反相器306具有2*gm

l

的跨导,反相器308具有4*gm

l

的跨导,并且反相器310具有2*gm

l

的跨导。假设gma=gmb,则gm总计现在是8*gm

l

。在输出out处的总器件漏极寄生电容约为8*cdd;在输出out处的总器件栅极寄生电容约为2*cgg,其中cdd和cgg分别是具有gm

l

跨导的反相器的漏极和栅极寄生电容。

[0054]

将图2的加法拓扑与图3的减法拓扑进行比较,减法拓扑改善了线性度,因为反相器308的输出端和反相器306的输出端连接在一起。特别是,将反相器306和308的输出端连接在一起使得它们的大信号偏置条件非常相似,从而消除了图2的加法拓扑中的问题。然而,图3的减法拓扑显示了更高的功耗和更多的器件寄生电容,才具有与图2的加法拓扑相同的增益带宽积。

[0055]

图4是描绘根据示例的ctle 106的示意图。ctle 106包括反相器402、404和406,以及电容器408和电阻器410。ctle 106可以耦接到vcm发生器450。下面参考图10描述示例vcm发生器450。本领域技术人员将理解,可以使用其他类型的共模电压发生器。节点412耦接到反相器402的输入端。节点414耦接到反相器404的输入端。电容器408耦接在节点412和414之间。电阻器410耦接在电压vcm和节点412之间。节点414接收输入信号(in)。反相器402的输出端被耦接到:反相器404的输出端、反相器406的输入端和反相器406的输出端(称为节点416)。节点416提供输出信号(out)。电阻器410具有电阻r

hf

;电容器408具有电容c

hf

;反相器404具有跨导gm1;反相器402具有跨导gm2;反相器406具有跨导gm

l

。

[0056]

图4中所示的ctle 106采用了加法拓扑。与图2的ctle 200相反,电容器408设置在反相器402和404的输入端。此外,图4的ctle 106省略了gm

l

反相器之一(例如,反相器208)。电压vcm是由前端电路102在内部产生的输入共模电压。下面描述产生vcm的示例。

[0057]

对于ctle 106,g1和g2由以下等式定义:

[0058]

g1=gm1/gm

l

[0059]

g2=(gm1+gm2)/gm

l

[0060]

峰值(db)=20*log[(gm1+gm2)/gm1]

[0061]

在低频,输入信号被电容器408阻挡。在高频,输入信号通过电容器408。因此,ctle106是加法拓扑。ctle 106的传递函数为:

[0062]

(gm1/gm

l

)*(1+(gm2/gm1)*(sr

hfchf

/(1+sr

hfchf

))),

[0063]

其中s是复数频率参数。

[0064]

图5是图4的ctle 106的传递函数的曲线图500。曲线图500包括表示增益(db)的纵轴和表示频率(对数尺度)的横轴。曲线502代表ctle 106的传递函数,其在频率f2和f3之间具有等于20*log(g2)的增益。在频率0和f1之间,增益为20*log(g1)。因此,获得的峰值为20*log(g2/g1),单位为db。在频率f3之后增益下降。

[0065]

假设g1=0db和g2=6db,这导致6db峰值。在这种情况下:

[0066]

g1=gm1/gm

l

=1(0db)-》gm1=gm

l

[0067]

g2=(gm1+gm2)/gm

l

=2(6db)-》gm2=gm

l

[0068]

总计gm=gm1+gm2+gm

l

=3*gm

l

[0069]

为了与图2的ctle 200进行公平比较,在增益带宽积方面,ctle 106的gm

l

应该加倍(例如,2*gm

l

)。在这种情况下,反相器402具有2*gm

l

的跨导,反相器404具有2*gm

l

的跨导,并且反相器406具有2*gm

l

的跨导。out处的总器件漏极寄生电容约为6*cdd;out处的总器件栅极寄生电容约为2*cgg,其中cdd和cgg分别是具有跨导gm

l

的反相器的漏极和栅极寄生电容。与图2的加法拓扑相比,图4的加法拓扑显示了相同的功耗和器件寄生电容,但不存在线性问题,因为反相器402和404的输出连接在一起。

[0070]

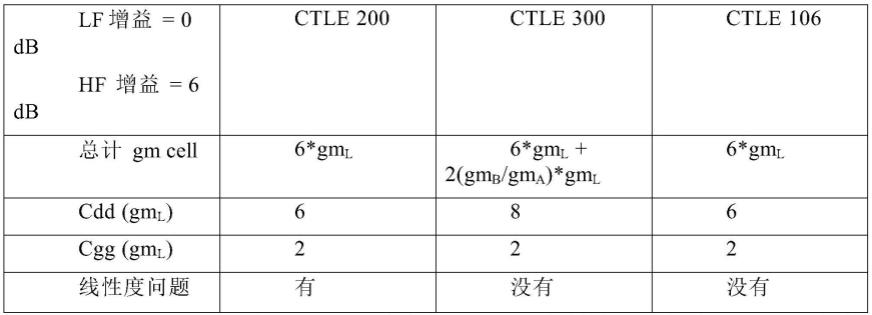

下表1总结了图2的ctle 200和图4的ctle 106之间的比较。

[0071]

表1

[0072][0073]

如表1所示,图4中ctle 106的拓扑显示出比减法拓扑更少的功耗,并且没有线性问题,如图2的加法拓扑所示。

[0074]

图6是描绘根据另一示例的ctle 600的示意图。ctle 600可用作上述ctle 106的替代版本。ctle 600在低频和高频处呈现多个峰值。与图4的ctle 106相比,额外的峰值是通过添加另一个反相器、电阻器和电容器来实现的。

[0075]

具体而言,ctle 600包括反相器602、604、606和608,以及电阻器610和612,以及电容器614和616。节点618耦接到反相器602的输入端。节点620耦接到反相器604的输入端。节点622耦接到反相器606的输入端。电容器614耦接在节点618和620之间。电容器616耦接在节点620和622之间。电阻器610耦接在节点618和电压vcm之间。电阻器612耦接在节点622和电压vcm之间。节点624包括反相器602的输出端、反相器604的输出端、反相器606的输出端、反相器608的输入端和反相器608的输出端。节点624提供输出信号(out)。节点620接收输入信号(in)。电阻器610和612分别具有电阻值r

hf

和r

lf

。电容器614和616分别具有电容值c

hf

和c

lf

。反相器604、602、606和608分别具有跨导gm1、gm2、gm3和gm

l

。

[0076]

图7是图6的ctle 600的传递函数的曲线图700。曲线图700包括代表增益(db)的纵

轴和代表频率(对数标度)的横轴。曲线702代表ctle 600的传递函数,其在频率fl2和fh1之间具有等于20*log(g1)的中等增益,在频率fh2和f3之间具有等于20*log(g2)的高增益。在频率0和fl1之间,低增益等于20*log(g0)。因此,对于峰值h和峰值

l

,获得的峰值分别为20*log(g2/g1)和20*log(g2/g0),以db计。在频率f3之后增益下降。ctle 600可以通过在输入端和输出端之间添加反相器支路(使用相应的电容器和电阻器)来扩展以具有更多峰值。

[0077]

图8是描绘根据另一示例的ctle 800的示意图。ctle 800可用作上述ctle 106的替代版本。ctle 800包括反相器802、804和806,以及电容器808和电阻器810和818。节点812耦接到反相器802的输入端。节点814耦接到反相器804的输入端。电容器808耦接在节点812和814之间。电阻器810耦接在电压vcm和节点812之间。节点814接收输入信号(in)。反相器802的输出端耦接到:反相器804的输出端和反相器806的输出端(称为节点816)。节点816提供输出信号(out)。电阻818耦接在节点816和反相器806的输入端之间。电阻器810具有电阻值r

hf

;电容器808具有电容c

hf

;反相器804具有跨导gm1;反相器802具有跨导gm2;反相器806具有跨导gm

l

,电阻器818具有电阻值ra。ctle 800类似于图4的ctle 106,但通过使用由反相器806和电阻器818形成的有源电感器而达到带宽扩展。

[0078]

图9是描绘根据另一示例的ctle 900的示意图。ctle 900包括反相器902、904和906,以及电容器908、电阻器910和电感器918。节点912耦接到反相器902的输入端。节点914耦接到反相器904的输入端。电容器908耦接在节点912和914之间。电阻器910耦接在电压vcm和节点912之间。节点914接收输入信号(in)。反相器902的输出端耦接到:反相器904的输出端、反相器906的输入端和反相器906的输出端(称为节点916)。电感器918耦接到节点916并提供输出信号(out)。电阻器910具有电阻值r

hf

;电容器908具有电容c

hf

;反相器904具有跨导gm1;反相器902具有跨导gm2;反相器906具有跨导gm

l

;并且电感器918具有电感值l。ctle 900类似于图4的ctle 106,但采用了使用无源电感器918的带宽扩展。

[0079]

在进一步的示例中,ctle 106、600、800和900的各种组件可以是可变的并且能够针对均衡目标和应用进行编程。对于ctle 106,这包括电阻器410、电容器408、反相器402、反相器404和反相器406(即,反相器可以具有可调节的跨导)。对于ctle 600,这包括电阻器610、612、电容器614、616和反相器602、604、606和608。对于ctle800,这包括电阻器810、818、电容器808和反相器802、804和806。对于ctle 900,这包括电阻器910、电容器908、电感器918和反相器902、904和906。

[0080]

图10是描绘根据示例的用于本文描述的ctle电路的vcm发生器1000的示意图。vcm发生器1000包括反相器1002,其输入端连接到其输出端以提供电压vcm。vcm发生器1000使用基于反相器的二极管来实现。就布局样式和偏置条件(例如,电流密度)而言,反相器1002应该是反相器402、404和406的复制品。

[0081]

图11是描绘根据另一示例的ctle 1100的示意图。ctle 1100从伪差分输出生成共模电压vcm。ctle 1100包括反相器1102、1104、1106、1122、1124和1126。ctle 1100还包括电阻器1110、1130、1137和1138。ctle 1100还包括电容器1108和1128。

[0082]

节点1112耦接到反相器1102的输入端。节点1114耦接到反相器1104的输入端。电容器1108耦接在节点1112和1114之间。电阻器1110耦接在节点1114和提供vcm的节点1140之间。节点1112接收输入信号(inp)。反相器1102的输出端耦接到:反相器1104的输出端、反相器1106的输入端和反相器1106的输出端(称为节点1116)。节点1116提供输出信号

(outn)。电阻器1110具有电阻值r

hf

;电容器1108具有电容值c

hf

;反相器1102具有跨导gm1;反相器1104具有跨导gm2;反相器1106具有跨导gm

l

。

[0083]

节点1132耦接到反相器1122的输入端。节点1134耦接到反相器1124的输入端。电容器1128耦接在节点1132和1134之间。电阻器1130耦接在节点1132和提供vcm的节点1140之间。节点1134接收输入信号(inn)。反相器1122的输出端耦接到:反相器1124的输出端、反相器1126的输入端和反相器1126的输出端(称为节点1136)。节点1136提供输出信号(outp)。电阻器1130具有电阻值r

hf

;电容器1128具有电容值c

hf

;反相器1124具有跨导gm1;反相器1122具有跨导gm2;反相器1126具有跨导gm

l

。

[0084]

电阻器1137耦接在节点1116和节点1140之间。电阻器1138耦接在节点1136和节点1140之间。节点1140提供电压vcm。在这种伪差分情况下,vcm是通过自偏置生成的,这消除了与将复制二极管用作vcm发生器相关的功耗。

[0085]

图12a是描绘根据示例的可编程器件54的框图。可编程器件54包括多个可编程集成电路(ic)1,例如可编程ic 1a、1b、1c和1d。在示例中,每个可编程ic 1是设置在中介层60上的ic裸片。每个可编程ic 1包括可编程器件54的超级逻辑区域(slr)53,例如slr 53a、53b、53c和53d。可编程ic 1通过中介层60(称为超长线(sll)52)上的导体进行互连。

[0086]

图12b是描绘根据示例的可编程ic 1的框图。可编程ic 1可用于实现可编程器件或可编程器件54中的可编程ic之一。可编程ic 1包括可编程逻辑(pl3)(也称为可编程结构)、配置逻辑25、和配置存储器26。可编程ic 1可以被耦接到外部电路,例如非易失性存储器27、dram 28、和其他电路29。pl 3包括逻辑单元30、支持电路31、和可编程互连32。逻辑单元30包括可以被配置为实现多个输入端的一般逻辑功能的电路。支持电路31包括专用电路,例如收发器、输入/输出块、数字信号处理器、存储器等。逻辑单元和支持电路31可以使用可编程互连32互连。用于对逻辑单元30进行编程、用于设置支持电路31的参数以及用于对可编程互连32进行编程的信息由配置存储器26存储在配置存储器26中。配置逻辑25可以从非易失性存储器27或任何其他来源(例如,dram 28或从其他电路29)获得配置数据。在一些示例中,可编程ic 1包括处理系统(ps)2。ps 2可以包括微处理器、存储器、支持电路、io电路等。在一些示例中,可编程ic 1包括片上网络(noc)55和数据处理引擎(dpe)阵列56。noc 55被配置为提供可编程ic 1的子系统之间的通信,例如在可编程ic 1的子系统之间的通信,诸如在ps 2、pl 3和dpe阵列56之间的通信。dpe阵列56可以包括被配置为执行数据处理的dpe阵列,例如矢量处理器阵列。在示例中,可编程ic 1可以包括ctle 106的一个或多个实例,包括本文描述的其任何示例实现。

[0087]

图12c图示了包括pl 3的可编程ic 1的现场可编程门阵列(fpga)实现。图12c中所示的pl 3可以用于本文所述的可编程器件的任何示例中。pl 3包括大量不同的可编程块,包括可配置逻辑块(“clb”)33、随机存取存储器块(“bram”)34、输入/输出块(“iob”)36、配置和时钟逻辑(“config/clocks”)42,数字信号处理块(“dsp”)35,专用输入/输出块(“i/o”)41(例如,配置端口和时钟端口),以及其他可编程逻辑39,例如数字时钟管理器、模数转换器、系统监控逻辑等。在示例中,可编程ic 1可以包括ctle 106的一个或多个实例,包括本文描述的其任何示例实现。

[0088]

在一些pl中,每个可编程块可以包括至少一个可编程互连元件(“int”)43,该互连元件具有与同一块内可编程逻辑元件的输入和输出端48的连接,如图6d顶部所包含的示例

所示。每个可编程互连元件43还可以包括到同一块或其他块中的相邻可编程互连元件的互连段49的连接。每个可编程互连元件43还可以包括到逻辑块(未示出)之间的通用路由资源的互连段50的连接。一般路由资源可以包括逻辑块(未示出)之间的路由通道,逻辑块包括互连段(例如,互连段50)的轨道和用于连接互连段的开关块(未示出)。一般路由资源的互连段(例如互连段50)可以跨越一个或多个逻辑块。可编程互连元件43与通用布线资源一起为所示pl实现可编程互连结构(“可编程互连”)。

[0089]

在示例实现中,clb 33可以包括可配置逻辑元件(“cle”)44,其可以被编程以实现用户逻辑加上单个可编程互连元件(“int”)43。bram 34可以包括bram逻辑元件(“brl”)45以及一个或多个可编程互连元件。典型地,包含在块中的互连元件的数量取决于块的高度。在图示的示例中,bram块具有与五个clb相同的高度,但也可以使用其他数字(例如,四个)。除了适当数量的可编程互连元件之外,dsp块35还可以包括dsp逻辑元件(“dspl”)46。除了可编程互连元件43的一个实例之外,iob 36可以包括例如输入/输出逻辑元件(“iol”)47的两个实例。如本领域技术人员将看到的,例如,连接到i/o逻辑元件47的实际的i/o焊盘通常不限于输入/输出逻辑元件47的区域。

[0090]

在图示的示例中,靠近裸片中心的柱状区域(如图3d所示)用于配置、时钟和其他控制逻辑。从水平区域或列延伸的垂直列51用于在pl的宽度上分布时钟和配置信号。

[0091]

使用图12c所示架构的一些pl包括额外的逻辑块,这些逻辑块破坏了构成pl大部分的常规柱状结构。额外的逻辑块可以是可编程块和/或专用逻辑。

[0092]

应当指出,图12c打算仅仅说明示例性pl架构。例如,行中逻辑块的数量、行的相对宽度、行的数量和顺序、行中包含的逻辑块的类型、逻辑块的相对大小、以及被包括在图12c顶部的互连/逻辑实现纯粹是示例性的。例如,在实际的pl中,通常在clb出现的任何地方都包含不止一个相邻的clb行,以促进用户逻辑的有效实现,但相邻clb行的数量会随着pl的整体大小而变化。

[0093]

虽然上述内容针对具体示例,但在不脱离其基本范围的情况下可以设计其他和进一步的示例,并且其范围由所附权利要求确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1