双三相谐波抑制收发器的制作方法

双三相谐波抑制收发器

1.本技术要求jiang等人在2020年5月30日提交的题目为“dual 3-phase harmonic rejiection transceiver”的美国临时专利申请第63/032,591号的优先权,该美国临时专利申请以其整体通过引用被合并。

技术领域

2.本公开内容一般地涉及用于减少收发器中的不想要的谐波含量的架构。

背景技术:

3.在诸如蜂窝电话的无线终端中,通常具有可能干扰信号处理的不期望的本地振荡器时钟生成的谐波信号(谐波)。在发射器侧,这些谐波可以通过非线性被混频回接近期望信号的载波频率,并且产生近信道失真,并且可能影响附近使用相同或接近相同的载波频率的其他无线终端。在接收器侧,接近期望信号的时钟谐波频率的阻断信号在被混频回基带频率时可以通过下变频处理落在期望的信号频率之上,以降低接收信号的信噪比和失真比。期望尽可能地减小这些时钟谐波的影响。

技术实现要素:

4.根据本公开内容的一个方面,具有三相信号源的发射器被配置成提供形成三相输入信号的三个输入信号和三个输入信号中的每一个的反相输入信号,并且包括频率合成器和谐波抑制混频器。频率合成器被配置成生成具有三个时钟信号的第一三相时钟信号,三个时钟信号中的每一个具有与三相输入信号的输入信号之一相对应的相位,并且生成具有三个时钟信号的第二三相时钟信号,三个时钟信号中的每一个具有与三相输入信号的反相输入信号之一相对应的相位。谐波抑制混频器包括:第一组三个混频器,每个混频器被配置成接收第一三相时钟信号的时钟信号之一并将第一三相时钟信号的时钟信号之一与对应相位的输入信号之一混频;以及第二组三个混频器,每个混频器被配置成接收第二三相时钟信号的时钟信号之一并将第二三相时钟信号的时钟信号之一与对应相位的反相输入信号之一混频。谐波抑制混频器还被配置成:通过组合第一组三个混频器的输出来形成第一中间信号,通过组合第二组三个混频器的输出来形成第二中间信号,以及组合第一中间信号和第二中间信号以形成谐波抑制混频器的第一输出信号。

5.可选地,在前述方面中,发射器还包括第一可变增益放大器和第二可变增益放大器。第一可变增益放大器被配置成:接收第一中间信号;以及在组合第一中间信号和第二中间信号以形成谐波抑制混频器的第一输出信号之前,放大第一中间信号。第二可变增益放大器被配置成:接收第二中间信号;以及在组合第一中间信号和第二中间信号以形成谐波抑制混频器的第一输出信号之前,放大第二中间信号。

6.可选地,在前述方面中的任一方面中,谐波抑制混频器还包括第二混频部分,包括:第三组三个混频器,每个混频器被配置成接收第一三相时钟信号中的时钟信号之一并将第一三相时钟信号中的时钟信号之一与对应相位的输入信号之一的反相输入信号混频;

以及第四组三个混频器,每个混频器被配置成接收第二三相时钟信号的时钟信号之一并将第二三相时钟信号的时钟信号之一与对应相位的反相输入信号之一为其反相的输入信号混频。谐波抑制混频器被配置成:通过组合第三组三个混频器的输出来形成第三中间信号,通过组合第四组三个混频器的输出来形成第四中间信号,以及组合第三中间信号和第四中间信号以形成谐波抑制混频器的第二输出信号。

7.可选地,在前述方面中,发射器还包括电感耦合器,包括:第一线圈,其被配置成:在第一端子处接收谐波抑制混频器的第一输出信号,并且在第二端子处接收谐波抑制混频器的第二输出信号;以及与第一线圈电感耦合的第二线圈,第二线圈具有被配置成为发射器提供单端输出的第一端子和连接至接地的第二端子。

8.可选地,在前述方面中,发射器还包括被配置成接收和放大单端输出的功率放大器。

9.可选地,在前述方面中,发射器还包括被配置成接收和发送单端输出的天线。

10.可选地,在前述方面中的任一方面中,三相信号源被配置成接收同相/正交格式的输入信号,并从其生成形成三相输入信号的三个输入信号和三个输入信号中的每个信号的反相输入信号。

11.可选地,在前述方面中的任一方面中,频率合成器包括:压控振荡器,其被配置成生成振荡器信号;第一三相生成器,其被配置成从振荡器信号生成第一三相时钟信号;延迟电路,其被配置成接收和延迟振荡器信号;以及第二三相生成器,其连接至延迟电路并被配置成从延迟的振荡器信号生成第二三相时钟信号。

12.可选地,在前述方面中,频率合成器包括锁相环,该锁相环包括压控振荡器。

13.可选地,在前述两个方面中的任一方面中,压控振荡器被配置成生成频率为三相时钟信号的频率的3/2的振荡器信号。

14.可选地,在前述方面中,延迟电路将90

°

相移引入到振荡器信号中。

15.可选地,在前述两个方面中的任一方面中,频率合成器被配置成生成三相时钟信号,其中三个时钟信号中的每个时钟信号的占空比为1/3。

16.根据本公开内容的另一方面,提供了一种发送信号的方法,包括:接收形成三相输入信号的三个输入信号和三个输入信号中的每个信号的反相输入信号;接收具有三个时钟信号的第一三相时钟信号和具有三个时钟信号的第二三相时钟信号,第一三相时钟信号的三个时钟信号中的每一个具有与三相输入信号的输入信号之一相对应的相位,并且第二三相时钟信号的三个时钟信号中的每一个具有与三相输入信号的反相输入信号之一相对应的相位;以及从形成三相输入信号的三个输入信号和三个输入信号中的每个信号的反相输入信号以及从第一三相时钟信号和第二三相时钟信号生成第一输出信号。第一输出信号通过以下操作来生成:对于第一三相时钟信号的三个时钟信号中的每一个,将时钟信号与对应相位的输入信号混频;针对第一三相时钟信号的三个时钟信号,组合所混频的时钟信号和输入信号,以形成第一中间信号;对于第二三相时钟信号的三个时钟信号中的每一个,将时钟信号与对应相位的反相输入信号混频;针对第二三相时钟信号的三个时钟信号,组合所混频的时钟信号和反相输入信号,以形成第二中间信号;以及组合第一中间信号和第二中间信号以生成第一输出信号。

17.可选地,在前述方面中,该方法还包括在组合第一中间信号和第二中间信号以生

成第一输出信号之前,分别放大第一中间信号和第二中间信号。

18.可选地,在前述两个方面中的任一方面中,该方法还包括:从形成三相输入信号的三个输入信号和三个输入信号中的每个信号的反相输入信号以及从第一三相时钟信号和第二三相时钟信号生成第二输出信号,通过:对于第一三相时钟信号的三个时钟信号中的每一个,将时钟信号与对应相位的反相输入信号混频;针对第一三相时钟信号的三个时钟信号,组合所混频的时钟信号和反相输入信号,以形成第三中间信号;对于第二三相时钟信号的三个时钟信号中的每一个,将时钟信号与对应相位的反相输入信号之一为其反相的输入信号混频;针对第二三相时钟信号的三个时钟信号,组合所混频的时钟信号和输入信号,以形成第四中间信号;以及组合第三中间信号和第四中间信号以生成第一输出信号。

19.可选地,在前述方面中,该方法还包括:将第一输出信号和第二输出信号分别施加至电感耦合器的第一线圈的第一端子和第二端子;接收并放大来自电感耦合器的与第一线圈电感耦合的第二线圈的输出;以及发送经放大的输出。

20.可选地,在发送信号的方法的前述方面中的任一方面中,该方法还包括:接收同相/正交格式的输入信号;以及从输入信号生成形成三相输入信号的三个输入信号和三个输入信号中的每个信号的反相输入信号。

21.可选地,在发送信号的方法的前述方面中的任一方面中,该方法还包括:由压控振荡器生成振荡器信号;从振荡器信号生成第一三相时钟信号;延迟振荡器信号;以及从延迟的振荡器信号生成第二三相时钟信号。

22.可选地,在前述方面中,压控振荡器被配置成生成频率为三相时钟信号的频率的3/2的振荡器信号。

23.可选地,在前述方面中,延迟振荡器信号包括将90

°

相移引入到振荡器信号中。

24.可选地,在前述三个方面中的任一方面中,该方法还包括:生成第一三相时钟信号,其中三个时钟信号中的每个时钟信号的占空比为1/3;以及生成第二三相时钟信号,其中三个时钟信号中的每个时钟信号的占空比为1/3。

25.根据本公开内容的附加方面,一种接收器包括:频率合成器,其被配置成生成具有三个时钟信号的第一三相时钟信号;以及生成具有三个时钟信号的第二三相时钟信号,第二三相时钟的三个时钟信号包括与第一三相时钟信号的三个时钟信号之一具有180

°

相移的时钟信号;以及谐波抑制混频器。谐波抑制混频器包括第一混频部分,第一混频部分包括:第一组三个混频器,每个混频器被配置成接收并混频第一三相时钟信号的时钟信号之一和输入信号,以生成三相第一输出信号的三个信号之一;以及第二组三个混频器,每个混频器被配置成接收并混频第二三相时钟信号的时钟信号之一和输入信号,以生成三相第二输出信号的三个信号之一,第二输出信号中的每个信号是第一三相输出信号的对应信号的反相。

26.可选地,在前述方面中,接收器还包括差分三相到正交转换器,其被配置成接收第一三相输出信号和第二三相输出信号并将第一三相输出信号和第二三相输出信号转换为同相/正交格式。

27.可选地,在接收器的前述方面中的任一方面中,接收器还包括:第一低噪声放大器,其被配置成接收并放大输入信号;以及将经放大的输入信号提供给第一组三个混频器;以及第二低噪声放大器,其被配置成接收并放大输入信号;以及将经放大的输入信号提供

给第二组三个混频器。

28.可选地,在前述方面中,第一低噪声放大器和第二低噪声放大器被配置成提供经放大的输入信号作为差分输出,第一组三个混频器和第二组三个混频器分别接收第一低噪声放大器和第二低噪声放大器的正侧输出:谐波抑制混频器还包括:第二混频部分,第二混频部分包括:第三组三个混频器,每个混频器被配置成接收并混频第一三相时钟信号的时钟信号之一和第一低噪声放大器的负侧输出,以生成三相负侧第一输出信号的三个信号之一;以及第四组三个混频器,每个混频器被配置成接收并混频第二三相时钟信号的时钟信号之一和低噪声放大器的负侧输出,以生成三相负侧第二输出信号的三个信号之一,负侧第二输出信号中的每个信号是第一负侧三相输出信号的对应信号的反相。

29.可选地,在接收器的前述两个方面中的任一方面中,接收器还包括被配置成接收输入信号并将其提供给第一低噪声放大器和第二低噪声放大器的天线。

30.可选地,在接收器的前述方面中的任一方面中,频率合成器包括:压控振荡器,其被配置成生成振荡器信号;第一三相生成器,其被配置成从振荡器信号生成第一三相时钟信号;延迟电路,其被配置成接收和延迟振荡器信号;以及第二三相生成器,其连接至延迟电路并被配置成从延迟的振荡器信号生成第二三相时钟信号。

31.可选地,在前述方面中,频率合成器包括锁相环,该锁相环包括压控振荡器。

32.可选地,在接收器的前述两个方面中的任一方面中,压控振荡器被配置成生成频率为三相时钟信号的频率的3/2的振荡器信号。

33.可选地,在前述方面中,延迟电路将90

°

相移引入到振荡器信号中。

34.可选地,在接收器的前述两个方面中的任一方面中,频率合成器被配置成生成三相时钟信号,其中三个时钟信号中的每个时钟信号的占空比为1/3。

35.根据本公开内容的另一方面,提供了一种接收信号的方法,包括:接收输入信号;接收具有三个时钟信号的第一三相时钟信号和具有三个时钟信号的第二三相时钟信号,第一三相时钟信号的三个时钟信号中的每一个具有与三相输入信号的输入信号之一相对应的相位,并且第二三相时钟信号的三个时钟信号中的每一个具有与三相输入信号的反相输入信号之一相对应的相位;以及从输入信号以及从第一三相时钟信号和第二三相时钟信号生成形成三相第一输出信号的三个第一输出信号和三个第一输出信号中的每个信号的反相输出信号,三个第一输出信号中的每一个具有与三个时钟信号之一相对应的相位。三个第一输出信号通过以下操作来生成:对于第一组三个混频器中的对应一个混频器中的第一三相时钟信号的三个时钟信号中的每一个,将时钟信号与输入信号混频,以生成三相第一输出信号;以及对于第二组三个混频器中的对应一个混频器中的第二三相时钟信号的三个时钟信号中的每一个,将时钟信号与输入信号混频,以生成三个第一输出信号中的每个信号的反相输出信号。

36.可选地,在接收信号的方法的前述方面中,该方法还包括将三相第一输出信号和三个第一输出信号中的每个信号的反相输出信号转换为同相/正交格式。

37.可选地,在接收信号的方法的前述方面中的任一方面中,该方法还包括:在第一低噪声放大器和第二低噪声放大器中分别放大输入信号;提供来自第一低噪声放大器的经放大的输入信号以与对应的第一三相时钟信号混频,以生成三相第一输出信号;以及提供来自第二低噪声放大器的经放大的输入信号以与对应的第二三相时钟信号混频,以生成三个

第一输出信号中的每个信号的反相输出信号。

38.可选地,在前述方面中,第一低噪声放大器和第二低噪声放大器被配置成提供经放大的输入信号作为差分输出,第一组三个混频器和第二组三个混频器分别接收第一低噪声放大器和第二低噪声放大器的正侧输出,该方法还包括:对于第三组三个混频器中的对应一个混频器中的第一三相时钟信号的三个时钟信号中的每一个,将时钟信号与第一低噪声放大器的负侧输出混频,以生成三相负侧第一输出信号的三个信号之一;以及对于第四组三个混频器中的对应一个混频器中的第二三相时钟信号的三个时钟信号中的每一个,将时钟信号与低噪声放大器的负侧输出混频,以生成三相负侧第二输出信号的三个信号之一,负侧第二输出信号中的每个信号是第一负侧三相输出信号的对应信号的反相。

39.可选地,在前述两个方面中的任一方面中,该方法还包括从天线接收输入信号并将其提供给第一低噪声放大器和第二低噪声放大器。

40.可选地,在接收信号的方法的前述方面中的任一方面中,该方法还包括:由压控振荡器生成振荡器信号;从振荡器信号生成第一三相时钟信号;延迟振荡器信号;以及从延迟的振荡器信号生成第二三相时钟信号。

41.可选地,在前述方面中,压控振荡器被配置成生成频率为三相时钟信号的频率的3/2的振荡器信号。

42.可选地,在前述方面中,延迟振荡器信号包括将90

°

相移引入到振荡器信号中。

43.可选地,在接收信号的方法的前述三个方面中的任一方面中,该方法还包括:生成第一三相时钟信号,其中三个时钟信号中的每个时钟信号的占空比为1/3;以及生成第二三相时钟信号,其中三个时钟信号中的每个时钟信号的占空比为1/3。

44.提供本发明内容以简化形式介绍一系列概念,这些概念下面将在具体实施方式中进一步描述。本发明内容既不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在用于帮助确定所要求保护的主题的范围。所要求保护的主题不限于解决背景技术中指出的任何或所有缺点的实现方式。

附图说明

45.本公开内容的各方面通过示例的方式被示出,并且不受附图的限制,对于附图,相似的附图标记指示要素。

46.图1示出了用于传送数据的无线网络。

47.图2是可以在诸如图1中的网络中使用的无线通信系统的框图。

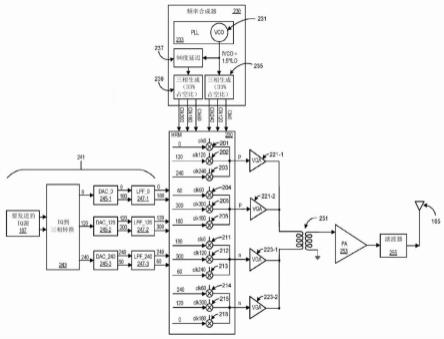

48.图3是示出改进的谐波抑制的双三相发射器的第一实施方式的框图。

49.图4是示出了来自图3的频率合成器块的每个时钟及其占空比的时序图。

50.图5示出了图3的实施方式的功率放大器的性能的模拟结果。

51.图6是示出图3的实施方式中的收发器的操作的第一实施方式的流程图。

52.图7是示出改进的谐波抑制的双三相接收器的第一实施方式的框图。

53.图8a示出了在期望的接收器信号的载波频率的第二谐波处存在的强阻断频率的示例。

54.图8b示出了图7的接收器针对图8a的输入的输出。

55.图9是示出图7的实施方式中的接收器的操作的实施方式的流程图。

具体实施方式

56.现在将参照附图来描述本公开内容,附图一般涉及用于减少来自发射器和接收器的不想要的谐波含量的技术。提出了以下双三相发射器和接收器的实施方式,所述双三相发射器和接收器可以从以本地振荡器频率的3/2的频率操作的压控振荡器生成本地振荡器时钟信号,并且能够在通常要求压控振荡器以本地振荡器频率的两倍(或更高)运行的水平下减少不想要的谐波。在下面描述的架构中,生成第一三相时钟信号以及第二移位的三相时钟信号。这些时钟信号中的第一时钟信号的分量各自与相同相位的三相输入信号的分量混频,其中所得到的三个信号被混频以形成第一中间信号。第二三相时钟信号的分量各自与相同相位的三个三相输入信号的反相分量混频,其中所得到的三个信号被混频以形成第二中间信号。这两个中间信号可以被分别放大和组合以提供输出。在差分实施方式中,可以类似地通过切换三相输入及其反相的角色来生成n侧输出。

57.应当理解,本公开内容的当前实施方式可以以许多不同的形式来实现,并且权利要求的范围不应被解释为受限于本文中阐述的实施方式。而是,提供这些实施方式以使得本公开内容将是透彻且完整的,并且这些实施方式将本发明的实施方式构思充分传达给本领域技术人员。实际上,本公开内容旨在覆盖包括在由所附权利要求限定的本公开内容的范围和精神内的这些实施方式的替代、修改和等同物。此外,在本公开内容的当前实施方式的以下详细描述中,阐述了许多具体细节以便提供透彻的理解。然而,对于本领域普通技术人员而言将清楚的是,可以在没有这样的具体细节的情况下实践本公开内容的当前实施方式。

58.图1示出了用于传送数据的无线网络。通信系统10包括例如用户设备11a至11c、无线电接入网络(radio access network,ran)12a至12b、核心网络13、公共交换电话网络(public switched telephone network,pstn)14、因特网15和其他网络16。附加的或替选的网络包括私有数据分组网络和公共数据分组网络,包括公司内部网。虽然在图中示出了特定数量的这些部件或元件,但是在系统10中可以包括任意数量的这些部件或元件。

59.在一个实施方式中,无线网络可以是第五代(fifth generation,5g)网络,5g网络包括至少一个5g基站,5g基站采用正交频分复用(orthogonal frequency-division multiplexing,ofdm)和/或非ofdm以及短于1毫秒(ms)的传输时间间隔(transmission time interval,tti)(例如,100或200微秒)来与通信装置进行通信。通常,对基站的提及可以指enb和5g基站(gnb)中的任一个。另外,网络还可以包括用于处理经由至少一个enb或gnb基站从通信装置接收的信息的网络服务器。

60.系统10使多个无线用户能够发送和接收数据以及其他内容。系统10可以实现一种或更多种信道接入方法,例如但不限于码分多址(code division multiple access,cdma)、时分多址(time division multiple access,tdma)、频分多址(frequency division multiple access,fdma)、正交fdma(orthogonal fdma,ofdma)或单载波fdma(single-carrier fdma,sc-fdma)。

61.用户设备(user equipment,ue)11a至11c被配置成在系统10中操作和/或通信。例如,用户设备11a至11c被配置成发送和/或接收无线信号或有线信号。每个用户设备11a至11c表示任何合适的终端用户装置,并且可以包括这样的装置(或者可以被称为):用户设备/装置、无线发送/接收单元(receive unit,ue)、移动台、固定或移动用户单元、寻呼机、

蜂窝电话、个人数字助理(personal digital assistant,pda)、智能手机、膝上型计算机、计算机、触摸板、无线传感器、可穿戴装置或消费电子装置。

62.在所描绘的实施方式中,ran 12a至12b分别包括一个或更多个基站17a、17b(统称为基站17)。基站17中的每一个被配置成与ue 11a、11b、11c中的一个或更多个无线对接,以使得能够接入核心网络13、pstn 14、因特网15和/或其他网络16。例如,基站(base station,bs)17可以包括一些公知装置中的一个或更多个,诸如基站收发台(base transceiver station,bts)、node-b(nodeb)、演进型nodeb(evolved nodeb,enb)、下一代(第五代)(5g)nodeb(gnb)、家庭nodeb、家庭enodeb、站点控制器、接入点(access point,ap)或无线路由器或服务器、路由器、交换机或具有有线或无线网络的其他处理实体。

63.在一个实施方式中,基站17a形成ran 12a的一部分,ran 12a可以包括其他基站、元件和/或装置。类似地,基站17b形成ran 12b的一部分,ran 12b可以包括其他基站、元件和/或装置。基站17中的每一个进行操作以在特定地理地区或区域(有时被称为“小区”)内发送和/或接收无线信号。在一些实施方式中,可以采用具有用于每个小区的多个收发器的多输入多输出(multiple-input multiple-output,mimo)技术。

64.基站17使用无线通信链路通过一个或更多个空中接口(未示出)与用户设备11a至11c中的一个或更多个进行通信。空中接口可以利用任何合适的无线电接入技术。

65.设想系统10可以使用多信道接入功能,包括例如其中基站17和用户设备11a至11c被配置成实现长期演进无线通信标准(long term evolution,lte)、lte高级(lte advanced,lte-a)和/或lte多媒体广播多播服务(multimedia broadcast multicast service,mbms)的方案。在其他实施方式中,基站17和用户设备11a至11c被配置成实现umts、hspa或hspa+标准和协议。当然,也可以使用其他多址方案和无线协议。

66.ran 12a至12b与核心网络13进行通信以向用户设备11a至11c提供语音、数据、应用、通过因特网协议的语音(voice over internet protocol,voip)或其他服务。应当理解,ran 12a至12b和/或核心网络13可以与一个或更多个其他ran(未示出)直接或间接通信。核心网络13还可以用作其他网络(诸如pstn 14、因特网15和其他网络16)的网关接入。另外,用户设备11a至11c中的一些或全部可以包括用于使用不同的无线技术和/或协议通过不同的无线链路与不同的无线网络进行通信的功能。

67.ran 12a至12b还可以包括毫米和/或微波接入点(ap)。ap可以是基站17的一部分,或者可以位于远离基站17的位置。ap可以包括但不限于连接点(mmw cp)或能够进行mmw通信的基站17(例如,mmw基站)。mmw ap可以发送和接收例如从24g hz至100ghz的频率范围内的信号,但是不需要在整个该范围内进行操作。如本文中所使用的,术语基站用于指代基站和/或无线接入点。

68.尽管图1示出了通信系统的一个示例,但是可以对图1进行各种改变。例如,通信系统10可以包括任意数量的任何适当配置的用户设备、基站、网络或其他部件。还应当理解,术语用户设备可以指代与蜂窝或移动通信系统中的无线电网络节点进行通信的任何类型的无线装置。用户设备的非限制性示例是目标装置、装置到装置(device-to-device,d2d)用户设备、机器类型用户设备或能够进行机器到机器(machine-to-machine,m2m)通信的用户设备、膝上型计算机、pda、ipad、平板电脑、移动终端、智能手机、膝上型嵌入式设备(laptop embedded equipped,lee)、膝上型安装设备(laptop mounted equipment,lme)和

usb加密狗。

69.图2是诸如移动手机或用户设备11a至11c或基站17的无线通信系统100的框图,示出了关于以下附图所讨论的一些元件。为了从处理器111的电路元件发送输出信号,发射器(transmitter,tx)rf/模拟部分101根据tx数字基带块107的结构将输出信号从基带或中频(intermediate frequency,if)范围上变频至射频(radio frequency,rf)范围,并且还在将发送信号提供给天线105之前对输出的发送信号进行放大和滤波。发射器(tx)rf/模拟部分101还可以被配置成执行其他处理以准备输出的发送信号。由tx数字基带块107生成的输出信号以同相/正交(in-phase/quadrature,i/q)格式作为同相信号i

tx

和正交信号q

tx

提供给tx rf/模拟部分101。尽管tx数字基带块107在图2中被示出为与tx rf/模拟部分101分离的块,但是根据实施方式,这些元件可以不同地组合为电路元件,并以硬件、固件、软件或这些的组合来实现。

70.信号由天线105接收并被提供给接收器(receiver,rx)rf/模拟部分102。rx部分102在将信号传送到处理器111处所表示的装置上的其他元件之前执行任何需要或想要的信号处理,诸如从射频(rf)范围至中频(if)范围的下变频以及滤波。在图2的实施方式中,rx rf/模拟部分102的输出是i/q格式的,并且rx数字基带部分117将其转换成提供给处理器的接收信号。尽管rx数字基带部分117在图2中被示出为与rx rf/模拟部分102分离的块,但是根据实施方式,这些元件可以不同地组合为电路元件,并以硬件、固件、软件或这些的组合来实现。另外,尽管图2将tx rf/模拟部分101和rx rf/模拟部分102表示为单独的元件,但是根据实施方式,发射器和接收器路径可以共享许多元件或者被实现为组合的收发器。在下文中,“收发器”通常可以用于指代组合的发射器/接收器、单独的收发器和接收器部分或者在发射器与接收器之间共享一个或更多个部件(例如,本地振荡器)的实施方式。

71.在诸如移动电话的收发器中,通常具有从本地振荡器生成的不期望的时钟谐波。在发射器侧,这些时钟谐波可以通过非线性被混频回接近期望信号的频率,并且产生近信道失真(例如,cim2、cim3、cim5,其中cimx是第x阶计数器互调),并且还影响附近使用近载波频率的其他无线终端。在接收器侧,接近期望信号的时钟谐波频率的阻断信号被混频回基带频率时在下变频时可能落在期望信号频率之上,并使所接收的信号退化。因此,期望尽可能地减少这些不想要的时钟谐波的影响。

72.通常,这些不想要的谐波中的一些可以通过多相(n相)混频器设计来去除,其中适当地选择n,其中n值越高,将去除的谐波越多。因此,高的n值对于谐波抑制是优选的。然而,对于n相混频器设计,高的n值需要振荡器(例如,压控振荡器或vco)在高频下运行。(通常,最小vco频率是f

lo

*n/2,其中f

lo

是本地振荡器载波频率。)这导致vco中的高功率消耗,并且可能使vco设计具有挑战性。

73.以下给出了谐波抑制混频器(harmonic rejection mixer,hrm)混频器的实施方式,该混频器可以在较低值n=3下运行,从而降低vco频率要求,同时比传统三相hrm抑制更多的谐波。为了发送正交iq信号(同相/正交或iq格式的信号),使用n=3的最小值,即三相系统。由于n的较小值,通常优选三相系统。对于5g蜂窝系统,载波频率(如当前定义的)可以是7.15ghz。通过三相系统,vco可以低至fcarrier*n/2=7.15ghz*3/2=10.725ghz运行,这并不难设计。然而,常规的三相系统不抑制第二时钟谐波和第四谐波,这两种谐波将通过单端功率放大器在发射器情况下被转换为cim2/cim4,并且可能不符合某些标准的规范。另

外,根据前端配置,第二谐波本身可能会导致发射器系统在第二谐波频率下不符合杂散发射规范。

74.以下给出了发射器和接收器的实施方式,其使用三相系统,同时比标准三相系统抑制更多的时钟谐波。即使标准三相系统在降低压控振荡器的最大工作频率方面具有优势,但是第二谐波和第四谐波的抑制不足是严重的问题,并且使得标准三相在蜂窝系统中不是非常有用。下面给出的实施方式使用双三相系统,其中两个三相系统彼此偏移60度。在该双三相系统中,vco可以在3/2载波频率的频率下(f

vco

=fcarrier*3/2)运行,同时抑制第二谐波、第三谐波和第四谐波。这意味着该双三相系统具有六相系统的谐波抑制特性,而vco的最大频率仅为标准三相系统的最大频率。图3是示出基本概念的框图。

75.图3是表现出改进的谐波抑制的双三相发射器的第一实施方式的框图。考虑处于高级别的图3,可以在图2的tx数字基带块107内生成的iq源107提供要发送的信号。来自iq源107的信号是i/q格式的,并且如下所述,在三相信号源241中被转换成差分三相信号,所述三相信号源241的组成部分将模拟三相格式的源信号提供给谐波抑制块hrm 200。频率合成器230将双三相时钟信号提供给hrm 200。hrm 200的输出通过一组可变增益放大器vga 221-i和vga 223-i、电感耦合器251、功率放大器pa 253和滤波器255提供给天线105。

76.在iq信号路径中,来自iq源107的iq数据在转换块243中被数字地转换为一组三相基带信号(0,120,240)。然后,三个数模转换器(digital to analog converter,dac)dac_0 245-1、dac_120 245-2和dac_240 245-3将三相数字信号转换为模拟信号,然后通过低通滤波器(low pass filter,lpf)lpf_0 247-1、lpf_120 247-2和lpf_240 247-3对所述模拟信号进行滤波,以去除不想要的失真和噪声。通常,dac和lpf是相对而言不受收发器内其他噪声源影响的差分电路。这意味着除了0、120和240信号外,还创建互补信号(180,300,60)并将互补信号提供给hrm 200。元件107、243、245-1、245-2、245-3、247-1、247-2和247-3一起形成差分三相信号源241。

77.在频率合成器230的块中,vco 231可以是锁相环路pll 233的一部分。vco可以在频率fvco=1.5*flo下运行,其中flo是本地振荡器频率或载波频率。vco输出被馈送至第一三相时钟生成块235,以生成clk0、clk120和clk240。vco输出还被馈送至90度相移块237,然后被馈送至第二三相生成块239。由于三相生成块239基本上是除以1.5操作,因此初始90度相移会在最终载波频率下变为60度,这意味着将在块239中生成clk60、clk180和clk300。对于所有六个时钟(clk0,clk120,clk240,clk60,clk180和clk300),在该实施方式中,每个时钟的占空比为33.33%,因此来自生成块235和239中的每一个的三个时钟信号是非交叠的并且加起来达到100%,但是时钟形成不同的块交叠。

78.图4是示出来自频率合成器块230的每个时钟及其占空比的时序图。如图4所示,clk0、clk120和clk240形成三相时钟信号的第一组非交叠信号,以及clk60、clk180和clk300形成三相时钟信号的第二组非交叠信号。组合所有六个时钟,它们是交叠的时钟。

79.返回到图3,hrm 200的两个p侧中间输出各自进入vga 221-1或vga-2 221-2中的对应一个。这些vga中的每一个的输入是来自一组三个混频器的组合输出,每个混频器接收来自三相生成器块235或三相时钟生成器块239的一组时钟信号中的一个:vga 221-1的输入是接收clk0的混频器201、接收clk120的混频器202和接收clk240的混频器203的组合输出,以产生第一p侧中间输出;以及vga 221-2的输入是接收clk60的混频器204、接收clk300

的混频器205和接收clk180的混频器206的组合输出,以产生第二p侧中间输出。如上所述,这些时钟信号中的每一个具有1/3或33%的占空比,并且是非交叠的,但加起来达到100%。

80.类似的布置用于hrm 200的n侧中间输出,每个输出进入对应的vga 223-1或vga-3 223-2中的一个。这些vga中的每一个的输入是来自一组三个混频器的组合输出,每个混频器接收来自三相生成器块235或三相时钟生成器块239的一组时钟信号中的一个:vga 223-1的输入是接收clk0的混频器211、接收clk120的混频器212和接收clk240的混频器213的组合输出,以产生第一n侧中间输出;以及vga 221-2的输入是接收clk60的混频器214、接收clk300的混频器215和接收clk180的混频器216的组合输出,以产生第二n侧中间输出。如上所述,这些时钟信号中的每一个具有1/3或33%的占空比,并且是非交叠的,但加起来达到100%。

81.谐波抑制混频器(hrm)200将lpf的输出与双三相lo时钟的信号组合,以生成rf输出。如图3所示,在p侧,来自相应lpf 247-1、247-2和247-3的三相输出0、120和240的信号各自与第一组混频器201、202和203中的对应一个混频器中的第一三相时钟信号的相同相位的时钟信号混频。同样在p侧,来自相应lpf 247-1、247-2和247-3的三相输出的反相输入信号180、300和60各自与第一组混频器206、205和204中的对应一个混频器中的第二三相时钟信号的相同相位的时钟信号混频。

82.hrm 200的n侧与p侧类似地布置,但是来自lpf中的每一个的输出被交换,使得输入信号与相反相位的时钟信号混频。在第一组n侧混频器中,三相输入信号的反相输入180、300和60分别与混频器211中的clk0、混频器212中的clk120和混频器213中的clk240混频。在第二组n侧混频器中,三相输入信号的输入0、120和240分别与第二三相时钟信号的与混频器216中的clk180、混频器215中的clk300和混频器214中的clk60的相反相位对应的时钟信号混频。

83.来自p侧混频器的rf中间输出由vga 221-1和221-2放大并组合以提供来自hrm 200的p侧输出信号,来自n侧混频器的rf中间输出类似地由vga 223-1和223-2放大并组合以提供来自hrm 200的n侧输出信号。为了将来自vga的rf输出转换为单端输出,可以使用电感耦合器251,其中组合的p侧输出和组合的n侧输出跨接在电感耦合器25l的第一线圈和电感耦合器251的第二线圈两端,所述电感耦合器的第二线圈的一侧设置为接地,另一侧在输出端处提供单端信号。功率放大器pa 253对单端输出进行放大,并且通过rf滤波器255对pa输出进行滤波以去除不想要的失真。最后,经滤波的rf输出被馈送至天线105以进行发射。

84.通常,hrm 200内的混频器是蜂窝应用中的无源混频器,这意味着交叠时钟会在不同路径之间产生串扰。为了避免这种情况,可以如图3所示使用分段的vga 221-1、221-2、223-1和223-2,使得每个单独的路径具有不交叠的时钟。

85.图5示出了图3的实施方式的功率放大器的输出端处的性能的模拟结果。更具体地,图5的曲线图绘制了根据频率变化的三相功率放大器输出端的输出,该输出以分贝(db)为单位进行了归一化使得期望的发射器(tx)信号为0db。在图5的曲线图中,出于快速模拟目的,期望的信号频率(约1.2288

×

108hz)被选择为低于实际的rf目标频率。在模拟中,假设90度相移块237为非理想的(使用85度)。除了期望的tx信号之外,在稍微较低的频率处还有由于lo泄漏引起的峰值下降约-60db、以及由于图像失真引起的峰值下降超过-80db。cim2n和cim4p尖峰是由于非理想的延迟值而生成的。总之,它示出了如果被适当地管理,即

使对于非理想的实现方式,cim失真也可以显著减少。

86.关于谐波,对于二阶计数器互调,图5示出了正侧上的峰值cim2p下降-80db、负侧上的峰值cim2n下降约-60db、以及cim4p下降约-90db。如果相移块237中的相移接近90度,则这些cim值将进一步减小。没有三阶cim3峰值,仅有的其他显著的尖峰是cim5,其下降约-100db。因此,图5的模拟结果示出了图3的双三相hrm架构的功率放大器pa 253的输出端处的性能可以实现与标准六相hrm相当的谐波抑制。该系统的频谱示出所有cim失真的电平对于蜂窝应用而言足够低。

87.图6是示出图3的实施方式中的收发器的操作的第一实施方式的流程图。在601处,hrm从三相信号源241接收n相输入信号的n个分量以及这些输入信号的反相。在图3的实施方式中,这包括三相输入信号的分量(0,120,240)和这些输入信号的反相(180,300,60)。在图3的实施方式中,这些信号由三相转换块dac 245-1、245-2、245-3和lpf 247-1、247-2、247-3根据iq源107的i/q信号生成。

88.在603处,频率合成器230生成lo时钟信号,并且hrm 200接收lo时钟信号。lo时钟信号包括第一三相时钟信号的三个分量和第二三相时钟信号的三个分量。在图3的实施方式中,第一三相时钟信号是来自生成器块235的时钟信号clk0、clk120和clk240,所有时钟信号的占空比为1/3,并且第二三相时钟信号与第一三相信号偏移60度,并且是来自生成器块239的时钟信号clk60、clk180和clk300,所有时钟信号的占空比为1/3。尽管图6的流程图以特定序列呈现其元素,但是将理解,这些可以全部同时执行(即,601、603及后续元素在操作期间同时进行),以在图3的电路发送时生成输出信号。

89.在605处,第一三相时钟信号的每个时钟信号与对应相位的输入信号混频。例如,在图3的实施方式中,在hrm 200的p侧的第一组混频器中,输入信号分量(0,120,240)分别与混频器201、202和203中的三相分量(clk0,clk120,clk240)混频。在607处,混频器的输出被组合以形成p侧的第一中间信号,所述第一中间信号然后在vga 221-1中被放大。

90.与605和607同时执行609和611。在609处,第二三相时钟信号的每个时钟信号与对应相位的反相输入信号混频。例如,在图3的实施方式中,在hrm 200的p侧的第二组混频器中,移位的输入信号分量(60,300,180)分别与混频器204、205和206中的第二三相分量(clk60,clk300,clk180)混频。在611处,这些混频器的输出被组合以形成p侧的第二中间信号,所述第二中间信号然后在vga 221-2中被放大。在如图3的双侧实施方式中,如上所述生成两个n侧中间输出以补充605至611。

91.在613处,在图3的双侧实施方式中,第一中间信号和第二中间信号被组合以生成hrm 200的p侧的输出信号。vga 221-1和221-2的输出被组合以提供hrm 200的p侧的输出信号。在图3的双侧实施方式中,在n侧,中间输出被类似地组合以提供hrm 200的n侧的输出信号。

92.然后在615中发送输出信号。在类似于图3的双侧实施方式中,p侧和n侧输出在电感耦合器251的线圈处被转换成单侧输出。单侧输出随后在功率放大器pa 253中进行放大,在滤波器255处进行滤波,然后从天线105发射。

93.如所描述的,与标准三相发射器系统相比,在此描述的技术使用双三相发射器系统以进行更好的谐波抑制。双三相发射器系统可以在谐波抑制方面实现与标准六相发射器系统类似的性能。另外,双三相系统仅要求vco在1.5倍的载波频率或本地振荡器频率下运

行,而不是标准六相系统所需的三倍的载波频率,这降低了vco设计复杂性和功耗。

94.图7是抑制位于第二、第三和第四时钟谐波处或附近的阻断的双三相接收器系统的实施方式的框图。图7的接收器实施方式的整体结构类似于图3的发射器实施方式,除了大致而言信号路径反转。在此给出的接收器实施方式中,使用分段低噪声放大器(low noise amplifier,lna)来避免交叠串扰。

95.更具体地,频率合成器730可以具有与图3的频率合成器230相同或类似的结构,其中vco 731、pll 733、第一三相生成块735、延迟块737和第二三相生成块739可以如以上关于对应元件231、233、235、237和239所描述的那样进行操作。

96.不是接收三相输入信号及其分量的反相信号,hrm 700现在生成三相输出信号(0,120,240),并且因为图7同样是双侧实施方式,还生成三相输出的反相值(180,300,60)。互补的输出信号对用作到一组低通滤波器和模数转换器的差分输入。更具体地,(0,180)对是到lpf_0 747-1的差分输入,lpf_0 747-1的输出然后进入adc_0745-1,以提供三相输出的(单端)第一(0度相位)分量。类似地,(120,300)对是到lpf_120 747-2的差分输入,lpf_120 747-2的输出然后进入adc_120 745-2,以提供三相输出的(单端)第二(120度相位)分量;以及(240,60)对是到lpf_240 747-3的差分输入,lpf_240 747-3的输出然后进入adc_240 745-3,以提供三相输出的(单端)第三(240度相位)分量。

97.到hrm 700的输入来自lna 721-1和lna-2 721-2的分段lna,每个lna通过rf滤波器755被连接以从天线105接收信号。lna 721-1和721-2的输出是差分的,其中每一个的p侧输出进入hrm 700中对应一组p侧混频器,以及每一个的n侧输出进入hrm 700中对应一组n侧混频器。

98.在hrm 700内,来自lna 921-1的p侧输出进入第一组p侧混频器701、702和703,以分别与clk0、clk120和clk240混频,以生成输出分量0、120和240。来自lna921-1的n侧输出进入第一组p侧组混频器对711、712和713,以分别与clk0、clk120和clk240混频,以生成输出分量180、300和60,以生成反向差分输出分量180、300和60。

99.类似地,来自lna 921-2的p侧输出进入第二第一组n侧混频器711、712和713,以分别与clk0、clk120和clk240混频,以生成输出分量60、300和180。来自lna 921-1的n侧输出进入第二组n侧组混频器对714、715和716,以分别与clk60、clk300和clk180混频,以生成输出分量60、300和180,以生成反向差分输出分量240、300和180。

100.对于接收器,要解决的问题是当在天线处存在接近期望的接收器信号频率的谐波频率(例如,在第二谐波处)的强阻断(即,诸如另一近接蜂窝电话的干扰信号)时,要求接收器的最大vco频率在1.5倍的载波频率处。这由图8a示出。

101.图8a示出了在期望的接收器信号的载波频率的第二谐波处存在强阻断频率的示例。图8a是在图7的接收器的天线105处看到的信号的频率与电平的曲线图。fcarrier处的信号是期望的接收器信号,其中fcarrier对应于来自频率合成器块730的时钟信号的本地振荡器频率。在fcarrier*2处的信号是接近期望的信号的第二谐波的强阻断信号的示例,并且具有比期望信号更高的电平。通过1.5倍时钟,接收器将是三相系统,这意味着接近第二谐波的强阻断将通过下变频过程被转换成基带信号,并落入期望的信道,并且在标准的三相接收器系统中,将降低接收器的信噪比。取决于阻断信号电平,该时钟生成的失真电平可以显著大于目标/期望的信号电平,这意味着这种典型的三相系统可能无法通过标准要

求的阻断测试用例。

102.在如图7所示的双三相实施方式中,可以使第二谐波到基带的转换最小化。在图7的布置中,来自天线105的单端信号被lna块721-1、721-2转换为差分形式,并馈送至hrm 700,然后通过信号路径传播,类似于图3的发射器那样。图8b示出了图8b中表示的从三相到iq转换块743得到的输出。

103.图8b示出了图7的接收器针对图8a的输入的输出。接收器信道的基带频率从-fc延伸至fc。接近第二谐波的不想要的阻断可以被转换为目标rx信道内的基带,这将降低信噪比;然而,使用双三相接收器架构,如图8b所示,该阻断转换将被最小化为具有较低电平,从而提高信噪比。

104.图9是示出图7的实施方式中的接收器的操作的实施方式的流程图。在901处,接收输入信号。参考图7的实施方式,输入信号由天线105接收,然后进入分段lna721-1和721-2,其中差分输出被提供给hrm 700的p侧和n侧。

105.在903处,频率合成器730生成lo时钟信号,并且hrm 700接收lo时钟信号。lo时钟信号包括第一三相时钟信号的三个分量和移位的第二三相时钟信号的三个分量。在图7的实施方式中,这些是时钟信号clk0、clk120和clk240以及移位信号clk60、clk180和clk300,所有时钟信号的占空比为1/3(33%)。

106.在905处,对于第一三相时钟信号中的每个分量,来自lna 721-1的p侧输入信号与时钟信号混频,以生成对应的三相输出信号。在图7的实施方式中,在p侧,lna721-1的输出进入混频器701、702和703,在混频器701、702和703中,lna 721-1的输出分别与clk0、clk120和clk240混频,以提供0、120和240分量的第一三相输出信号。

107.在907处,对于第二三相时钟信号中的每个分量,来自lna 721-2的p侧输入信号与时钟信号混频,以生成对应的第二三相输出信号,第二三相输出信号的分量是905的第一三相输出信号的分量的反相。在图9的实施方式中,在p侧,lna 721-2的输出进入混频器704、705和706,在混频器704、705和706中,lna 721-2的输出分别与clk60、clk300和clk180混频,以提供60、300和180分量的第二三相输出信号。来自905的第一三相输出和来自907的第二三相输出一起生成差分三相输出。然后,差分三相输出可以进入lpf 747-1、747-2和747-3,接着进入adc 745-1、745-2和745-3,以及三相到iq转换器745,以提供iq格式的输出数据。

108.对于如图7中的双侧实施方式,lna 721-1和721-2的n侧输出分别进入要与第一三相时钟信号混频的第一组n侧混频器(711,712,713)以及要与第二三相时钟信号混频的第二组n侧混频器(714,715,716)。这些分别生成第二反相输出信号和第一输出信号的另一副本,其可以类似地用于生成iq输出。

109.如上所述,对于接收器实施方式以及发射器实施方式,所描述的双三相架构允许使用较低的vco频率来实现与传统六相系统类似的谐波性能。这将vco的最大工作频率的要求降低到1.5倍,而不是标准六相系统的3倍vco频率要求。

110.可以使用硬件、固件、软件或者这些的组合来实现本文中描述的技术。所使用的软件或固件存储在一个或更多个处理器可读存储装置上,以对图3至图9的一个或更多个块进行编程以执行本文中描述的功能。处理器可读存储装置可以包括计算机可读介质,诸如易失性和非易失性介质、可移除和不可移除介质。作为示例而非限制,计算机可读介质可以包

括计算机可读存储介质和通信介质。可以以用于存储诸如计算机可读指令、数据结构、程序模块或其他数据的信息的任何方法或技术来实现计算机可读存储介质。计算机可读存储介质的示例包括ram、rom、eeprom、闪速存储器或其他存储技术、cd-rom、数字多功能盘(dvd)或其他光盘存储装置、磁带盒、磁带、磁盘存储装置或其他磁性存储装置、或者可以用于存储期望信息并且可以由以上描述的部件访问的任何其他介质。一个或多个计算机可读介质不包括传播的、调制的或瞬态的信号。

111.通信介质通常在传播的、调制的或瞬态的数据信号诸如载波或其他传输机制中体现计算机可读指令、数据结构、程序模块或其他数据,并且包括任何信息传递介质。术语“调制的数据信号”是指以对信号中的信息进行编码的方式设置或改变其特性中的一个或更多个的信号。作为示例而非限制,通信介质包括有线介质诸如有线网络或直接有线连接以及无线介质诸如rf和其他无线介质。上述的任何组合也包括在计算机可读介质的范围内。

112.在替选实施方式中,软件或固件中的一些或全部可以由专用硬件逻辑部件代替。例如但不限于,可以使用的说明性类型的硬件逻辑部件包括现场可编程门阵列(field-programmable gate array,fpga)、专用集成电路(application-specific integrated circuit,asic)、专用标准产品(application-specific standard product,assp)、片上系统(system-on-a-chip,soc)、复杂可编程逻辑器件(complex programmable logic device,cpld)、专用计算机等。在一个实施方式中,实现一个或更多个实施方式的软件(存储在存储装置上)用于对一个或更多个处理器进行编程。一个或更多个处理器可以与一个或更多个计算机可读介质/存储装置、外围装置和/或通信接口进行通信。

113.应当理解,本主题可以以许多不同的形式来实现,并且不应被解释为限于本文中阐述的实施方式。而是,提供这些实施方式以使得本主题将是透彻且完整的,并且这些实施方式将本公开内容完全传达给本领域技术人员。实际上,本主题旨在覆盖包括在由所附权利要求限定的主题的范围和精神内的这些实施方式的替代、修改和等同物。此外,在本主题的以下详细描述中,阐述了许多具体细节以提供对本主题的透彻理解。然而,对于本领域普通技术人员而言将清楚的是,可以在没有这样的具体细节的情况下实践本主题。

114.本文中参考根据本公开内容的实施方式的方法、装置(系统)和计算机程序产品的流程图图示和/或框图描述了本公开内容的各方面。应当理解的是,流程图和/或框图的每个块以及流程图图示和/或框图中的块的组合可以由计算机程序指令来实现。可以将这些计算机程序指令提供给通用计算机、专用计算机或其他可编程数据处理装置的处理器以产生机器,使得经由计算机或其他可编程指令执行装置的处理器执行的指令创建用于实现流程图和/或框图块或多个块中指定的功能/动作的机构。

115.已经出于说明和描述的目的呈现了本公开内容的描述,但是本公开内容的描述并不旨在为穷举性的或者限于所公开的形式的公开内容。在不脱离本公开内容的范围和精神的情况下,许多修改和变型对于本领域普通技术人员将是明显的。选择和描述本文中的公开内容的各方面是为了最佳地解释本公开内容的原理和实际应用,并且使得本领域的其他普通技术人员能够理解具有适于所设想的特定用途的各种修改的本公开内容。

116.出于本文献的目的,与所公开的技术相关联的每个过程可以连续地并且由一个或更多个计算装置执行。过程中的每个步骤可以由与其他步骤中使用的计算装置相同或不同的计算装置执行,并且每个步骤不必一定由单个计算装置执行。

117.尽管已经以特定于结构特征和/或方法动作的语言描述了主题,但是应当理解,所附权利要求中限定的主题不必限于以上描述的特定特征或动作。而是,以上描述的特定特征和动作可以作为实现权利要求的示例形式而被公开。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1