驱动控制电路的制作方法

驱动控制电路

1.本技术享受2020年9月15日提交的日本专利申请号2020-154310的优先权利益,该日本专利申请的全部内容被援用于本技术。

技术领域

2.本实施方式整体上涉及一种驱动控制电路。

背景技术:

3.以往,公开有如下技术:在对输出晶体管的接通断开进行控制的驱动控制电路中,以预先存储的阈值为基准,对驱动输出晶体管的驱动元件的驱动能力进行调整,兼顾输出晶体管的开关速度的高速化以及emi噪声的抑制。在使用预先存储的输出晶体管的阈值的构成的情况下,需要阈值的存储电路,电路构成变得复杂。期望能够通过简单的构成来进行输出晶体管的阈值的检测以及驱动元件的驱动能力的调整的驱动控制电路。

技术实现要素:

4.本发明的一个实施方式提供一种驱动控制电路,能够通过简单的构成来进行输出晶体管的阈值的检测以及驱动元件的驱动能力的调整。

5.根据一个实施方式,驱动控制电路具备:第1驱动晶体管,响应驱动信号而对输出晶体管的栅极供给驱动电流;第1电容,一端被施加基准电位;第2驱动晶体管,响应上述驱动信号而对上述第1电容的另一端供给充电电流;第1比较电路,将上述输出晶体管的栅极电压与上述第1电容的另一端的电压进行比较,基于其结果来输出第1检测信号;第1控制信号生成电路,响应上述第1检测信号以及上述驱动信号而生成第1控制信号;以及第3驱动晶体管,响应上述第1控制信号而对上述输出晶体管的栅极供给驱动电流。

附图说明

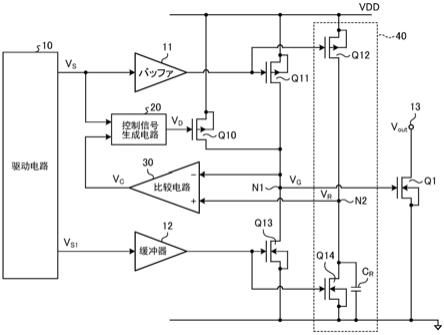

6.图1是表示第1实施方式的驱动控制电路的构成的图。

7.图2是用于对输出晶体管的栅极电容的变化进行说明的图。

8.图3是概要地表示各节点的电压关系的图。

9.图4是用于对输出晶体管的栅极电压与参照电压之间的关系进行说明的图。

10.图5是用于对第1实施方式的效果进行说明的图。

11.图6是表示第2实施方式的驱动控制电路的构成的图。

12.图7是用于对输出晶体管的栅极电压与参照电压之间的关系进行说明的图。

具体实施方式

13.以下,参照附图对实施方式的驱动控制电路进行详细说明。另外,本发明不被这些实施方式限定。

14.(第1实施方式)

15.图1是表示第1实施方式的驱动控制电路的构成的图。本实施方式具有驱动电路10。驱动电路10输出开关信号vs、v

s1

。开关信号vs、v

s1

设置有所谓的死区时间,以免驱动晶体管q11与q13以及q12与q14同时接通。

16.本实施方式具有缓冲器11、12。缓冲器11对开关信号vs进行波形整形而供给至驱动晶体管q11的栅极。缓冲器12对开关信号v

s1

进行波形整形而供给至驱动晶体管q13的栅极。

17.驱动晶体管q11的源极被施加电源电压vdd,漏极与驱动晶体管q13的漏极连接。驱动晶体管q11与q13的漏极的共同连接端n1与输出晶体管q1的栅极连接。输出晶体管q1的漏极与输出端13连接。驱动晶体管q13的源极接地。驱动晶体管q11在接通状态时向输出晶体管q1的栅极供给驱动电流。驱动晶体管q13在接通状态时使输出晶体管q1的栅极电容的电荷进行放电。

18.本实施方式具有参照电压生成电路40。参照电压生成电路40具有驱动晶体管q12、q14以及电容cr。电容cr的一端接地,被施加成为基准电位的接地电位。驱动晶体管q12的源极被施加电源电压vdd,漏极与驱动晶体管q14的漏极连接。驱动晶体管q12与q14的漏极的共同连接端n2与比较电路30的非反相输入端(+)连接。驱动晶体管q12、q14的接通断开由缓冲器11、12的输出分别控制。驱动晶体管q12在接通状态时供给充电电流,对电容cr进行充电。驱动晶体管q14在接通状态时使电容cr的电荷进行放电。

19.基于由输出晶体管q1的栅极源极间电容c

gs

和驱动晶体管q11的驱动能力确定的时间常数、以及驱动晶体管q12的驱动能力,来设定电容cr的值。例如,设定为:通过驱动晶体管q11将输出晶体管q1的栅极源极间电容c

gs

充电到成为规定的电压为止的时间、与通过驱动晶体管q12将电容cr充电到成为其规定的电压为止的时间相同。因而,电容cr的一端的电位与输出晶体管q1的源极的电位并不一定需要成为相同电位。

20.例如,在将电容cr的值设定为输出晶体管q1的栅极源极间电容c

gs

的1/2的情况下,将驱动晶体管q12的驱动能力设为驱动晶体管q11的驱动能力的1/2。由此,能够缩小驱动晶体管q12的尺寸而降低消耗电力。另外,此处所说的驱动能力是指驱动电流的供给能力。

21.本实施方式具有比较电路30。共同连接端n1与比较电路30的反相输入端(-)连接。比较电路30将共同连接端n1的电压即输出晶体管q1的栅极电压vg、与共同连接端n2的电压即参照电压生成电路40的电容cr的另一端侧的参照电压vr进行比较,并根据其比较结果来输出检测信号vc。

22.比较电路30例如具有磁滞特性。通过使比较电路30具有磁滞特性,例如,能够避免因噪声等而引起的比较电路30的误动作。

23.本实施方式具有控制信号生成电路20。对控制信号生成电路20供给检测信号vc以及开关信号vs。控制信号生成电路20响应检测信号vc以及开关信号vs而输出控制信号vd。控制信号vd对驱动晶体管q10的接通断开进行控制。控制信号生成电路20能够由对检测信号vc以及开关信号vs进行响应的闩锁电路构成。

24.驱动晶体管q10的驱动能力被设定得高于驱动晶体管q11的驱动能力。例如。通过使驱动晶体管q10的尺寸(栅极宽度)大于驱动晶体管q11的尺寸,由此能够提高驱动晶体管q10的驱动能力。

25.使用图2至图4对本实施方式的电路动作进行说明。图2表示输出晶体管q1的栅极

电容与栅极电压之间的关系。横轴表示输出晶体管q1的栅极电压,纵轴表示栅极电容。在栅极电压低于阈值的状态下,输出晶体管q1的栅极电容为栅极源极间电容c

gs

。当栅极电压变高、并成为阈值时,栅极电容成为栅极漏极间电容c

gd

。当栅极电压超过阈值地变高时,栅极电容成为c

gs

与c

gd

之和即c

gs

+c

gd

。

26.当栅极电压达到阈值时,输出晶体管q1的栅极电容成为栅极漏极间电容c

gd

,产生栅极电压在从v1到v2的区间中成为恒定的“坪(plateau)”。在本实施方式中,对该坪的区间的输出晶体管q1的栅极电压进行检测,作为输出晶体管q1的阈值。

27.通过驱动晶体管q12的驱动电流对参照电压生成电路40的电容cr进行充电,参照电压vr以一定的斜率上升。另一方面,输出晶体管q1的栅极电压vg在以阈值产生的坪中成为恒定。因此,通过将参照电压vr与栅极电压vg进行比较,能够容易地检测出栅极电压vg达到了输出晶体管q1的阈值的情况。

28.图3是概要地表示各节点的电压关系的图。上段的实线100表示开关信号vs。在定时t00,开关信号vs为l电平。

29.下一段表示栅极电压vg以及参照电压vr。单点划线101表示参照电压vr,实线102表示栅极电压vg。驱动晶体管q11、q12响应开关信号vs而接通,在定时t0,参照电压vr以及输出晶体管q1的栅极电压vg开始上升。在定时t1,检测出参照电压vr变得高于栅极电压vg,并达到输出晶体管q1的阈值的情况。在定时t2,栅极电压vg变得高于参照电压vr。

30.下一段的实线103表示比较电路30的检测信号vc。比较电路30在参照电压vr变得高于栅极电压vg的定时t1,输出h电平的检测信号vc。

31.下一段的实线104表示控制信号生成电路20输出的控制信号vd。控制信号vd响应h电平的检测信号vc而转变为l电平,使驱动晶体管q10接通。由此,能够提高向输出晶体管q1的栅极供给驱动电流的能力。控制信号生成电路20维持l电平,直至开关信号vs成为h电平的定时t3为止。

32.下段的实线105表示输出电压v

out

。当输出晶体管q1的栅极电压vg达到阈值时,输出晶体管q1的栅极被以驱动晶体管q11的驱动电流与驱动晶体管q10的驱动电流相加而得到的电流充电,输出端13的输出电压v

out

瞬间转变为l电平。输出晶体管q1在开关信号vs成为h电平的定时t3断开,输出电压v

out

成为h电平。

33.根据本实施方式,通过栅极电压vg与参照电压vr的比较,能够容易地检测出输出晶体管q1的栅极电压vg达到阈值的情况。在栅极电压vg达到阈值之前,仅使驱动能力较小的驱动晶体管q11动作,由此抑制向输出晶体管q1的栅极的冲击电流。由此,减少emi噪声。此外,在检测到栅极电压vg达到阈值之后,使驱动能力较高的驱动晶体管q10接通,并使其与驱动晶体管q11一起驱动,由此提高驱动能力。由此,能够加快输出晶体管q1的开关速度。

34.图4放大表示栅极电压vg与参照电压vr之间的关系。单点划线101表示参照电压vr,实线102表示栅极电压vg。响应开关信号vs而驱动晶体管q12接通,由此在定时t0参照电压生成电路40的电容cr开始充电,参照电压vr开始上升。另一方面,输出晶体管q1的栅极电压vg也在定时t0由于驱动晶体管q11接通而上升,但在产生坪的定时t1成为恒定。

35.定时t1由比较电路30检测出。通过对比较电路30的检测信号vc进行响应的控制信号vd使驱动能力较高的驱动晶体管q10接通,由此输出晶体管q1的栅极电压vg急剧上升,并在定时t2变得高于参照电压vr。

36.图5是用于对本实施方式的效果进行说明的图。横轴表示时间,纵轴概要地表示向输出晶体管q1的栅极的冲击电流。该图5的实线110表示仅使用驱动能力较高的驱动晶体管来驱动了输出晶体管q1的情况。

37.在通过驱动能力较高的驱动晶体管进行了驱动的情况下,冲击电流在从响应开关信号vs而接通的定时t0到t12的较短时间内达到电流值i10。由于驱动能力较高,因此冲击电流的峰值成为较大的电流值i10。实线111表示本实施方式的情况。在栅极电压vg成为阈值的定时t1之前,通过驱动能力较小的驱动晶体管q11进行驱动。因此,冲击电流被抑制为i20。由于冲击电流被抑制,因此输出晶体管q1的栅极电压vg平缓地上升。由此,栅极电压vg的变化率dv/dt变小,emi噪声得以抑制。

38.在达到阈值的定时t1之后,使驱动能力较高的驱动晶体管q10接通,并使其与驱动晶体管q11一起动作而提高驱动能力。由此,加快输出晶体管q1的开关速度。在定时t1,由于输出晶体管q1的栅极电压vg已经上升,因此冲击电流得以抑制,即使在定时t13也被抑制为i21。

39.根据本实施方式,通过与参照电压生成电路40的参照电压vr进行比较,由此能够容易地检测出输出晶体管q1的栅极电压vg达到阈值的情况。对输出晶体管q1的阈值进行检测的定时t1,能够通过参照电压生成电路40的构成来调整。例如,通过在电容cr与驱动晶体管q14的漏极之间串联连接电感器(未图示),由此能够使向电容cr的充电延迟。由此,能够使参照电压vr的上升延迟,使检测出栅极电压vg达到阈值的定时t1延迟。

40.例如,在输出晶体管q1为由gan(氮化镓)构成的gan晶体管的情况下,有时通过不同的芯片来构成gan晶体管并通过规定的布线与驱动晶体管q11、q13连接。在这种构成的情况下,由于布线具有寄生电感器成分,因此通过对电容cr连接电感器,能够抵消因布线的寄生电感器成分导致的延迟。

41.根据本实施方式,将参照电压生成电路40的电容cr的参照电压vr与输出晶体管q1的栅极电压vg进行比较,由此对栅极电压vg变得平坦的坪的区间的栅极电压vg进行检测而作为阈值电压。因而,也可以设置如下构成:在比较电路30输出检测信号vc时的参照电压vr的值从所假定的阈值范围脱离的情况下,通知异常。例如,通过对比较电路30的h电平的检测信号vc进行响应而使参照电压生成电路40的驱动晶体管q12、q14断开,由此能够使电容cr保持与输出晶体管q1的阈值对应的参照电压vr。通过将所保持的电压与假定为阈值的电压进行比较,由此能够判定是否为异常状态。

42.(第2实施方式)

43.图6是表示第2实施方式的驱动控制电路的构成的图。对于与已经说明过的实施方式对应的构成,赋予相同的符号,并仅在需要的情况下才进行重复的记载。以下也相同。

44.本实施方式具有参照电压生成电路41。参照电压生成电路41具有驱动晶体管q15、q16以及电容c

r1

。对驱动晶体管q15的栅极供给缓冲器11的输出信号,对驱动晶体管q16的栅极供给缓冲器12的输出信号。对驱动晶体管q15的源极施加电源电压vdd,漏极与驱动晶体管q16的漏极连接。驱动晶体管q16的源极接地。电容c

r1

的一端接地,被施加成为基准电位的接地电位。电容c

r1

的另一端与驱动晶体管q15、q16的漏极的共同连接端n3连接。驱动晶体管q15在接通状态时供给充电电流而对电容c

r1

进行充电。驱动晶体管q16在接通状态时对电容c

r1

的电荷进行放电。驱动晶体管q15、q16的接通断开,通过缓冲器11、12的输出来分别控制。

45.本实施方式具有比较电路31。比较电路31将栅极电压vg与共同连接端n3的参照电压v

r1

进行比较,并根据其比较结果来输出检测信号v

c1

。比较电路31为,当对非反相输入端(+)施加的参照电压v

r1

变得高于栅极电压vg时,将检测信号v

c1

设为h电平。

46.本实施方式具有控制信号生成电路21。控制信号生成电路21对比较电路31的检测信号v

c1

和开关信号vs进行响应而输出控制信号v

d1

。控制信号v

d1

对驱动晶体管q101的接通断开进行控制。驱动晶体管q101的驱动能力被设定为比驱动晶体管q11高的值。

47.使用图7对本实施方式的动作进行说明。图7表示栅极电压vg以及参照电压vr、v

r1

。单点划线101表示参照电压vr,实线102表示栅极电压vg,双点划线120表示参照电压v

r1

。如在第1实施方式的动作中说明过的那样,输出晶体管q1的栅极电压vg在阈值成为坪。因此,在定时t1,参照电压vr变得高于栅极电压vg。比较电路30检测出该电压关系,进行使驱动能力较高的驱动晶体管q10接通的控制。

48.同样,双点划线120所示的参照电压v

r1

也在定时t20变得高于栅极电压vg。通过比较电路31检测出该电压关系,比较电路31在定时t20生成h电平的检测信号v

c1

并供给至控制信号生成电路21。控制信号生成电路21响应检测信号v

c1

而将l电平的控制信号v

d1

供给至驱动晶体管q101,使驱动晶体管q101接通。通过驱动晶体管q101接通,表示栅极电压vg的实线102发生变化,但为了简化而省略图示。

49.在本实施方式中,在参照电压v

r1

变得高于栅极电压vg的定时t20,驱动能力较高的驱动晶体管q101接通。即,除了根据参照电压vr与栅极电压vg的比较动作来使驱动能力较高的驱动晶体管q10接通的调整之外,还根据参照电压v

r1

与栅极电压vg的比较动作来使驱动能力较高的驱动晶体管q101接通而进行驱动能力的调整。因此,能够进行极其细致的驱动能力的调整。

50.参照电压生成电路41能够通过驱动晶体管q15、q16以及电容c

r1

而简单地构成。此外,参照电压v

r1

的变化的斜率,能够通过电容c

r1

的值以及驱动晶体管q15的驱动电流的值来进行调整。因而,通过电容cr、c

r1

的值以及驱动晶体管q12、q15的驱动能力的调整,能够容易地调整参照电压生成电路40的参照电压vr的变化的斜率以及参照电压生成电路41的参照电压v

r1

的变化的斜率。通过调整参照电压vr、v

r1

的变化的斜率,能够对检测阈值的定时t1、t20、即使驱动能力较高的驱动晶体管q10、q101接通的定时进行调整。

51.能够使向电容cr、c

r1

的充电电流延迟,而使对输出晶体管q1的阈值进行检测的定时延迟。例如,通过在电容cr、c

r1

与共同连接端n2、n3之间连接电感器(未图示),由此能够使向电容cr、c

r1

的充电延迟。由此,能够使参照电压vr、v

r1

的上升延迟,能够使与栅极电压vg交叉的定时t1、t20延迟。

52.已经说明过的实施方式的控制信号生成电路20、21具有如下构成:在对比较电路30、31的h电平的检测信号vc、v

c1

进行了响应之后,在开关信号vs成为h电平的定时t3之前,输出l电平的控制信号vd、v

d1

,但也可以是如下构成:每当比较电路30、31的检测信号vc、v

c1

变化为h电平、l电平时,就输出输出电平发生变化的控制信号vd、v

d1

。在比较电路30、31的检测信号为l电平的情况下,能够仅使驱动能力较小的驱动晶体管q11动作而抑制冲击电流,每当检测信号vc、v

c1

成为h电平时,就使驱动能力较高的驱动晶体管q10、q101接通来提高驱动能力,而加快输出晶体管q1的开关速度。

53.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提示的,并

不意图对发明的范围进行限定。这些新的实施方式能够以其他各种方式加以实施,在不脱离发明的主旨的范围内能够进行各种省略、置换、变更。这些实施方式及其变形包含于发明的范围及主旨中,并且包含于专利请求范围所记载的发明和与其等同的范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1