一种基于阻变器件的全加器函数实现方法

1.本发明涉及一种实现全加器函数的方法,尤其是涉及一种基于阻变器件的全加器函数实现方法。

背景技术:

2.传统的cmos全加器主要包括与门、或门、异或门等模块。传统的cmos全加器是实现加法运算,常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。忆阻器具有小尺寸、多阻态、低功耗和非易失性等特点。目前,全加器函数的实现方式主要基于cmos器件,随着两个相加数数值增大,加法器数量增多,加法器自身延迟大和功耗高等缺陷日益突出,且cmos晶体管器件改进缓慢,尺寸缩小速度减缓,制作工艺正面临物理极限。由此,该cmos加法器在处理数据过程中功率消耗大、延迟大、面积大等问题。

技术实现要素:

3.本发明所要解决的技术问题是提供一种基于阻变器件的全加器函数实现方法,该方法仅采用五个忆阻器,通过改变阻变器件初始状态和读写操作即可实现全加器函数,可以减少电路面积,降低电路功耗,提高运行速度。

4.本发明解决上述技术问题所采用的技术方案为:一种基于阻变器件的全加器函数实现方法,包括以下步骤:

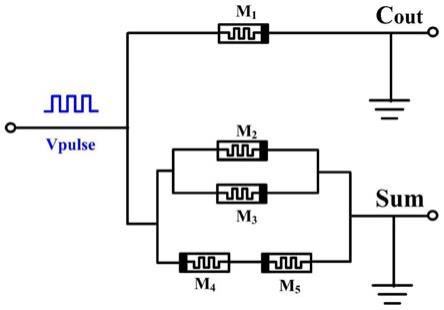

5.(1)选取具有电致电阻转变和非易失性的忆阻器,所述的忆阻器具有自下往上依次设置的底电极层、阻变层与顶电极层,定义忆阻器的顶电极层为t1端,底电极层为t2端,根据忆阻器的阻值设定忆阻器的两个阻态,将其两个阻态分别记为高阻态hrs和低阻态lrs,其中高阻态的阻值范围为2000ω~4000ω,低阻态的阻值范围为50ω~200ω;

6.(2)定义忆阻器的初始化的逻辑参数、忆阻器的输入和输出:

7.定义五个忆阻器分别为m1、m2、m3、m4、m5,其中m1单独作一路,m2和 m3并联,m4和m5串联,m2和m3与m4和m5并联,忆阻器初始化为高阻态时忆阻器的逻辑值为0,忆阻器初始化为低阻态时忆阻器的逻辑值为1;定义忆阻器的输入为脉宽50微秒的脉冲电压,该脉冲电压的幅值大小分别为0、v1,将忆阻器t1端的电势记为vt1,将忆阻器t2端的电势记为vt2;定义当写操作后,忆阻器电流为低电流值时忆阻器输出为逻辑0,忆阻器电流为高电流值时忆阻器输出为逻辑1;

8.(3)将忆阻器的t2端接地,用半导体参数分析测试仪对忆阻器的t1端施加直流扫描电压,实时测量忆阻器阻态变化的电流

‑

电压曲线图,具体过程为:

[0009]3‑

1在半导体参数分析测试仪中设置取值范围为100ua~1ma的限制电流后,用半导体参数分析测试仪对忆阻器的t1端施加正向扫描电压,正向扫描电压范围为0到0.3v,半导体参数分析测试仪测出忆阻器从高阻态向低阻态转变的电流

‑

电压曲线,记为曲线1;

[0010]3‑

2在半导体参数分析测试仪中设置取值100ma的限制电流后,用半导体参数分析测试仪对忆阻器的t1端施加负向扫描电压,负向扫描电压范围为0到

ꢀ‑

0.3v,半导体参数分

析测试仪测出忆阻器从低阻态向高阻态转变的电流

‑

电压曲线,记为曲线2;

[0011]

(4)重复步骤3

‑

1~步骤3

‑

2三百次,通过半导体参数分析测试仪300条曲线1和300条曲线2,共600条电流

‑

电压曲线,观察这600条电流

‑

电压曲线,获取vset和vreset的值,以此确定v1的取值;

[0012]

(5)信号a可以改变忆阻器状态,信号b和信号cin分别对忆阻器进行写操作,最后读取m1的电流值判断cout值,读取m2~m5的电流值之和来判断sum 值;

[0013]

(6)将cout0对应的全加器函数输出记为c0,将cout1对应的全加器函数输出记为c1,将cout2对应的全加器函数输出记为c2,以此类推,将cout7对应的全加器函数输出记为c7,分别对应全加器函数中进位的八个输出,将sum0 对应的全加器函数输出记为s0,将sum1对应的全加器函数输出记为s1,将sum2 对应的全加器函数输出记为s2,以此类推,将sum7对应的全加器函数输出记为 s7,分别对应全加器函数中两数相加和的八个输出:根据要实现的全加器函数初始化五个忆阻器到相应阻态;然后对忆阻器进行相应写操作,最后施加小电压脉冲读取电流,实现全加器函数。

[0014]

2.根据权利要求1所述的一种基于阻变器件的全加器实现方法,其特征在于所述的步骤(6)中操作实现全加器函数的具体方式为:

[0015]

实现全加器函数c0时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3,忆阻器的阻值保持不变,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取 m1的电流值为低电流,故全加器的c0输出逻辑值为0;

[0016]

实现全加器函数c1时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1 的电流值为低电流,故全加器c1输出逻辑值为0;

[0017]

实现全加器函数c2时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器的阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1 的电流值为低电流,故全加器c2输出逻辑值为0;

[0018]

实现全加器函数c3时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c3输出逻辑值为1;

[0019]

实现全加器函数c4时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半

[0020]

导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v 的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取 m1的电流值为低电流,故全加器c4输出逻辑值为0;

[0021]

实现全加器函数c5时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻

器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0.3v,忆阻器的阻值从高阻态转变为低阻态,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c5输出逻辑值为1;

[0022]

实现全加器函数c6时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100 微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c6输出逻辑值为1;实现全加器函数c7时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的 t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0.3v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的 t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c7输出逻辑值为1。

[0023]

实现全加器函数s0时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地,t2端分别接地、接地、接地、接地,m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接地、接0.3v,t2端分别接地、接0.3v、接0.3v、接地,此时m2、m3、m4、 m5阻态分别为高阻态、高阻态、高阻态、低阻态;再后将m2、m3、m4、m5的t1 端分别接地、接地、接地、

接地,t2端分别接地、接0.3v、接地、接地,最后 m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、低阻态,读取m2~m5的电流之和为低电流,故全加器s0输出逻辑值为0;

[0024]

实现全加器函数s1时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地, t2端分别接地、接地、接地、接0.3v,m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接地,此时m2、m3、 m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态;再后将m2、m3、m4、m5 的t1端分别接地、接0.3v、接0.3v、接地,t2端分别接地、接0.3v、接地、接地,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、低阻态,读取m2~m5的电流之和为高电流,故全加器s1输出逻辑值为1;

[0025]

实现全加器函数s2时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地, t2端分别接地、接地、接地、接地,m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接0.3v、接0.3v、接0.3v,t2端分别接地、接0.3v、接0.3v、接0.3v,此时m2、 m3、m4、m5阻态分别为高阻态、高阻态、高阻态、高阻态;再后将m2、m3、m4、 m5的t1端分别接地、接地、接地、接地,t2端分别接0.3v、接0.3v、接地、接地,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、低阻态,读取m2~m5的电流之和为高电流,故全加器s2输出逻辑值为1;

[0026]

实现全加器函数s3时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地, t2端分别接地、接地、接地、接0.3v,m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接0.3v、接0.3v、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接0.3v,此时m2、 m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态;再后将m2、m3、m4、 m5的t1端分别接地、接0.3v、接0.3v、接地,t2端分别接0.3v、接0.3v、接地、接地,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态,读取m2~m5的电流之和为低电流,故全加器s3输出逻辑值为0;

[0027]

实现全加器函数s4时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地,t2端分别接地、接地、接0.3v、接地,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接0.3v,t2端分别接地、接0.3v、接0.3v、接地,此时m2、m3、 m4、m5阻态分别为低阻态、高阻态、高阻态、低阻态;再后将m2、m3、m4、m5 的t1端分别接地、接地、接地、接地,t2端分别接地、接0.3v、接地、接0.3v,最后m2、m3、m4、m5阻态分别为低阻态、高阻态、高阻态、高阻态,读取m2~m5 的电流之和为高电流,故全加器s4输出逻辑值为1;

[0028]

实现全加器函数s5时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地,t2端分别接地、接地、接0.3v、接0.3v,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接地,此时m2、 m3、m4、m5阻态分别为低阻态、低阻态、高阻态、低阻态;再后将m2、m3、m4、 m5的t1端分别接地、接0.3v、接0.3v、接地,t2端分别接地、接0.3v、接地、接0.3v,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态,读取m2~m5的电流之和为低电流,故全加器s5输出逻辑值为0;

[0029]

实现全加器函数s6时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地,t2端分别接地、接地、接0.3v、接地,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接 0.3v、接0.3v、接0.3v,t2端分别接地、接0.3v、接0.3v、接0.3v,此时 m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、低阻态;再后将m2、m3、m4、m5的t1端分别接地、接地、接地、接地,t2端分别接0.3v、接0.3v、接地、接0.3v,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、高阻态,读取m2~m5的电流之和为低电流,故全加器s6输出逻辑值为0;

[0030]

实现全加器函数s7时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地,t2端分别接地、接地、接0.3v、接0.3v,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接0.3v、接0.3v、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接0.3v,此时m2、m3、m4、m5阻态分别为高阻态、低阻态、高阻态、高阻态;再后将m2、 m3、m4、m5的t1端分别接地、接0.3v、接0.3v、接地,t2端分别接0.3v、接0.3v、接地、接0.3v,最后m2、m3、m4、m5阻态分别为高阻态、低阻态、低阻态、高阻态,读取m2~m5的电流之和为高电流,故全加器s7输出逻辑值为1。

[0031]

与现有技术相比,本发明的优点在于通过选取具有电致电阻转变和非易失性的忆阻器,根据忆阻器的阻值设定忆阻器的两个阻态,定义忆阻器的初始化的逻辑参数、忆阻器的输入和输出以及写操作后忆阻器的输出,并采用半导体参数分析测试仪中分别对忆阻器施加正向扫描电压和负向扫描电压获取忆阻器阻态转换的电压,基于该电压确定忆阻器的输入的脉宽50微秒的脉冲电压的幅值大小以及恒定直流电压,然后根据设计的全加器函数实现方法初始化忆阻器到相应阻后,通过施加信号a改变忆阻器阻态,信号b和c进行写操作,最后读取电流值,就能实现该三值单变量函数了,本发明的方法仅需要五个忆阻器配合半导体参数分析测试仪,就可以实现全加器函数,实现大幅减少器件数量,优化电路结构,简化操作方法,可以减少电路面积,降低电路功耗。

附图说明

[0032]

图1为本发明的基于阻变器件的全加器函数实现方法的忆阻器的结构示意图。

[0033]

图2为本发明的基于阻变器件的全加器函数实现方法的忆阻器的电流

‑

电压曲线图。

[0034]

图3为本发明的基于阻变器件的全加器函数实现方法的忆阻器在不同阻态下施加不同正向扫描电压后阻态的转变情况。

[0035]

图4为本发明的基于阻变器件的全加器函数实现方法的忆阻器在不同阻态下施加不同负向扫描电压后阻态的转变情况。

[0036]

图5是本发明的基于阻变器件的全加器函数实现方法实现全加器函数的操作方法图。

[0037]

图6是本发明的基于阻变器件的全加器函数实现方法实现全加器函数的电路结构图。

具体实施方式

[0038]

以下结合附图实施例对本发明作进一步详细描述。

[0039]

实施例:一种基于阻变器件的全加器函数实现方法,包括以下步骤:

[0040]

(1)选取具有电致电阻转变和非易失性和多阻态特性的忆阻器,如图1所示,忆阻器具有自下往上依次设置的底电极层、阻变层与顶电极层,定义忆阻器的顶电极层为t1端,底电极层为t2端,根据忆阻器的阻值设定忆阻器的两个阻态,将其两个阻态分别记为高阻态hrs,简称h和低阻态lrs,简称l,其中高阻态的阻值范围为2000ω~4000ω,低阻态的阻值范围为50ω~200ω;本发明的基于阻变器件的全加器函数实现方法的忆阻器在不同阻态下施加不同正向扫描电压后阻态的转变情况如图3所示,本发明的基于阻变器件的全加器函数实现方法的忆阻器在不同阻态下施加不同负向扫描电压后阻态的转变情况如图4所示;

[0041]

(2)定义忆阻器的初始化的逻辑参数、忆阻器的输入和输出:定义忆阻器初始化为高阻态时忆阻器的逻辑值为0,忆阻器初始化为低阻态时忆阻器的逻辑值为2;定义忆阻器的输入为脉宽50微秒的脉冲电压,该脉冲电压的幅值大小分别为0、v1,将忆阻器t1端的电势记为vt1,将忆阻器t2端的电势记为vt2;定义当写操作后,忆阻器阻态为高阻态时忆阻器输出为逻辑0,忆阻器阻态为中间阻态时忆阻器输出为逻辑1,忆阻器阻态为低阻态时忆阻器输出为逻辑2;

[0042]

(3)将忆阻器的t2端接地,用半导体参数分析测试仪对忆阻器的t1端施加直流扫描电压,实时测量忆阻器阻态变化的电流

‑

电压曲线图,具体过程为:

[0043]3‑

1在半导体参数分析测试仪中设置取值范围为100ua~1ma的限制电流后,用半导体参数分析测试仪对忆阻器的t1端施加正向扫描电压,正向扫描电压范围为0到0.3v,半导体参数分析测试仪测出忆阻器从高阻态向低阻态转变的电流

‑

电压曲线,记为曲线1;

[0044]3‑

2在半导体参数分析测试仪中设置取值100ma的限制电流后,用半导体参数分析测试仪对忆阻器的t1端施加负向扫描电压,负向扫描电压范围为0到

ꢀ‑

0.3v,半导体参数分析测试仪测出忆阻器从低阻态向高阻态转变的电流

‑

电压曲线,记为曲线2;

[0045]

(4)重复步骤3

‑

1~步骤3

‑

2三百次,通过半导体参数分析测试仪300条曲线1和300条曲线2,共600条电流

‑

电压曲线,观察这600条电流

‑

电压曲线,获取vset和vreset的值,因为set过程(施加正向扫描电压的过程)和reset 过程(施加负向扫描电压的过程)曲线具有较好的对称度,故统计set过程中高阻态向低阻态转变时的阈值电压值或者统计reset过程中低阻态向高阻态转变时的阈值电压值,确定v1;本实施例中,v1的值为0.3v;

[0046]

(5)信号a可以改变忆阻器状态,信号b和信号cin分别对忆阻器进行写操作,最后读取m1的电流值判断cout值,读取m2~m5的电流值之和来判断sum 值;

[0047]

(6)将cout0对应的全加器函数输出记为c0,将cout1对应的全加器函数输出记为c1,将cout2对应的全加器函数输出记为c2,以此类推,将cout7对应的全加器函数输出记为c7,分别对应全加器函数中进位的八个输出,将sum0 对应的全加器函数输出记为s0,将sum1对应的全加器函数输出记为s1,将sum2 对应的全加器函数输出记为s2,以此类推,将sum7对应的全加器函数输出记为 s7,分别对应全加器函数中两数相加和的八个输出:根据要实现的全加器函数初始化五个忆阻器到相应阻态;然后对忆阻器进行相应写操作,最后施加小电压脉冲读取电流,实现全加器函数。

[0048]

本实施例中,步骤(6)中实现全加器函数的具体方式为:

[0049]

(5)将f0对应的三值单变量函数记为f0,将f1对应的三值单变量函数记为f1,将f2对应的三值单变量函数记为f2,以此类推,将f25对应的三值单变量函数记为f25,将f26对应的三值单变量函数记为f26,分别采用两步操作实现f0、f1、f2、f5、f9、f18、f4、f12、f13、f14、f22、f21、f8、f17、f24、 f25和f26这17种三值单变量函数:先根据要实现的三值单变量函数初始化忆阻器到相应阻态;然后对忆阻器进行写操作,实现该三值单变量函数;将f3对应的三值单变量函数记为f3,将f1对应的三值单变量函数记为f1,将f2对应的三值单变量函数记为f2,以此类推,将f25对应的三值单变量函数记为f25,将f26对应的三值单变量函数记为f26,分别采用三步操作实现f3、f10、f11、 f19、f20、f23、f6、f7、f15和f16这10种三值单变量函数:先根据要实现的三值单变量函数初始化忆阻器到相应阻态;然后对忆阻器进行两次写操作,实现该三值单变量函数。

[0050]

本实施例中,步骤(5)中两步操作实现17种三值单变量函数的具体方式为:

[0051]

实现全加器函数c0时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3,忆阻器的阻值保持不变,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1 的电流值为低电流,故全加器的c0输出逻辑值为0;

[0052]

实现全加器函数c1时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1 的电流值为低电流,故全加器c1输出逻辑值为0;

[0053]

实现全加器函数c2时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端

通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器的阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1 的电流值为低电流,故全加器c2输出逻辑值为0;

[0054]

实现全加器函数c3时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c3输出逻辑值为1;

[0055]

实现全加器函数c4时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为0;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为低电流,故全加器c4输出逻辑值为0;

[0056]

实现全加器函数c5时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=

‑

0.3v,忆阻器阻值从低阻态转变

为高阻态,故忆阻器输出逻辑值为0;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0.3v,忆阻器的阻值从高阻态转变为低阻态,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c5输出逻辑值为1;

[0057]

实现全加器函数c6时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100 微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c6输出逻辑值为1;

[0058]

实现全加器函数c7时,先将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,始化初为低阻态;然后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,通过半导体参数分析测试仪在忆阻器的t2端加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0v,忆阻器阻值保持不变,故忆阻器输出逻辑值为1;再后将m1的t1端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0.3v的脉冲电压,将m1的t2端通过半导体参数分析测试仪在忆阻器加载一个脉宽不小于50微秒,且幅值为0v的脉冲电压,此时忆阻器实际承受电压为vt1

‑

vt2=0.3v,忆阻器的阻值保持不变,故忆阻器输出逻辑值为1;最后通过半导体参数分析测试仪在忆阻器的t1端加载一个脉宽不小于100微秒,且幅值为0v的脉冲电压,m1的t2端接地,读取m1的电流值为高电流,故全加器c7输出逻辑值为1;

[0059]

实现全加器函数s0时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地, t2端分别接地、接地、接地、接地,m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接地、接0.3v,t2端分别接地、接0.3v、接0.3v、接地,此时m2、m3、m4、 m5阻态分别为高阻态、高阻态、高阻态、低阻态;再后将m2、m3、m4、m5的t1 端分别接地、接地、接地、接地,t2端分别接地、接0.3v、接地、接地,最后 m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、低阻态,读取m2~m5的电流之和为低电流,故全加器s0输出逻辑值为0;

[0060]

实现全加器函数s1时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地, t2端分别接地、接地、接地、接0.3v,

m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接地,此时m2、m3、m4、 m5阻态分别为高阻态、高阻态、低阻态、高阻态;再后将m2、m3、m4、m5的t1 端分别接地、接0.3v、接0.3v、接地,t2端分别接地、接0.3v、接地、接地,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、低阻态,读取m2~m5 的电流之和为高电流,故全加器s1输出逻辑值为1;

[0061]

实现全加器函数s2时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地, t2端分别接地、接地、接地、接地,m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接0.3v、接 0.3v、接0.3v,t2端分别接地、接0.3v、接0.3v、接0.3v,此时m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、高阻态;再后将m2、m3、m4、m5 的t1端分别接地、接地、接地、接地,t2端分别接0.3v、接0.3v、接地、接地,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、低阻态,读取m2~m5的电流之和为高电流,故全加器s2输出逻辑值为1;

[0062]

实现全加器函数s3时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接地、接地、接地、接地, t2端分别接地、接地、接地、接0.3v,m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接0.3v、接0.3v、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接0.3v,此时m2、 m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态;再后将m2、m3、m4、 m5的t1端分别接地、接0.3v、接0.3v、接地,t2端分别接0.3v、接0.3v、接地、接地,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态,读取m2~m5的电流之和为低电流,故全加器s3输出逻辑值为0;

[0063]

实现全加器函数s4时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地,t2端分别接地、接地、接0.3v、接地,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接0.3v,t2端分别接地、接0.3v、接0.3v、接地,此时m2、 m3、m4、m5阻态分别为低阻态、高阻态、高阻态、低阻态;再后将m2、m3、m4、 m5的t1端分别接地、接地、接地、接地,t2端分别接地、接0.3v、接地、接 0.3v,最后m2、m3、m4、m5阻态分别为低阻态、高阻态、高阻态、高阻态,读取m2~m5的电流之和为高电流,故全加器s4输出逻辑值为1;

[0064]

实现全加器函数s5时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地,t2端分别接地、接地、接0.3v、接0.3v,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接地、接地、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接地,此时m2、 m3、m4、m5阻态分别为低阻态、低阻态、高阻态、低阻态;再后将m2、m3、m4、 m5的t1端分别接地、接0.3v、接0.3v、接地,t2端分别接地、接0.3v、接地、接0.3v,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、低阻态、高阻态,读取m2~m5的电流之和为低电流,故全加器s5输出逻辑值为0;

[0065]

实现全加器函数s6时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地,t2端分别接地、接地、接0.3v、接地,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、低阻态;然后将m2、m3、m4、m5的t1端分别接地、接0.3v、接0.3v、接0.3v,t2端分别接地、接0.3v、接0.3v、接0.3v,此时m2、m3、m4、m5

阻态分别为高阻态、高阻态、高阻态、低阻态;再后将m2、 m3、m4、m5的t1端分别接地、接地、接地、接地,t2端分别接0.3v、接0.3v、接地、接0.3v,最后m2、m3、m4、m5阻态分别为高阻态、高阻态、高阻态、高阻态,读取m2~m5的电流之和为低电流,故全加器s6输出逻辑值为0;

[0066]

实现全加器函数s7时,先将m2、m3、m4、m5分别初始化为高阻态、高阻态、低阻态、低阻态;m2、m3、m4、m5的t1端分别接0.3v、接0.3v、接地、接地, t2端分别接地、接地、接0.3v、接0.3v,m2、m3、m4、m5阻态分别为低阻态、低阻态、高阻态、高阻态;然后将m2、m3、m4、m5的t1端分别接地、接0.3v、接0.3v、接0.3v,t2端分别接0.3v、接0.3v、接0.3v、接0.3v,此时m2、m3、 m4、m5阻态分别为高阻态、低阻态、高阻态、高阻态;再后将m2、m3、m4、m5 的t1端分别接地、接0.3v、接0.3v、接地,t2端分别接0.3v、接0.3v、接地、接0.3v,最后m2、m3、m4、m5阻态分别为高阻态、低阻态、低阻态、高阻态,读取m2~m5的电流之和为高电流,故全加器s7输出逻辑值为1。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1