一种数字功率放大器及通信系统的制作方法

1.本技术涉及通信技术领域,尤其涉及一种数字功率放大器及通信系统。

背景技术:

2.为了提高频谱的利用效率,无线通信采用了多种不同制式的调制信号,如正交频分复用(orthogonal frequency division multiplexing,ofma)、码分多址(code-division multiple access,cdma)、时分多址(time division multiple access,tdma)等,根据相关协议的规定,这些制式的信号具有大小不同的峰均比(peak-to-average power ratio,papr),如正交频分复用(orthogonal frequency division multiplexing,ofdm)信号的峰均比为10~12db。

3.为保证射频信号的无损发射,即要求功率放大器(power amplifier,pa)具备高线性度的特性,高峰均比的信号在基站中对功放有更高的要求,根据功率管的特性,放大器有一个线性动态范围,在这个范围内,放大器的输出功率随输入功率线性增加。随着输入功率的继续增大,放大器渐渐进入饱和区,功率增益开始下降。为保证pa的线性度,可以采用功率回退的方法,使得pa的回退至线性工作区。但是,pa的线性度与效率存在折中关系,在保证线性度的同时会牺牲效率,导致pa的功耗增加。当功率放大器为满足高峰均比要求时,例如,10~12db的峰均比时,pa需工作于相应的10~12db的回退区,此时,功率放大器的效率非常低(甚至低于4%),即在同样输出功率下,低效率导致基站的输入功率大大增加。而功率放大器作为发射机系统的核心模块之一,其功耗会占到系统总功耗的30%以上。因此,在满足信号放大的线性度及峰均比的同时,亟需降低功率放大器功耗。

4.数字pa(digital pa,dpa)结合了开关类pa的高效率特点,同时采用多比特位对输入的模拟信号进行量化,得到相应比特位数的数字信号后输入至dpa中进行功率放大,可以有效提升dpa的线性度。为了提高dpa的精度以满足系统线性度的要求,dpa中晶体管的数量与信号的量化比特位的数量呈指数增长,例如,为了获得15比特的dpa量化精度,晶体管数量将达到上千个,导致功率放大器的成本和复杂度较大。

技术实现要素:

5.本技术提供一种数字功率放大器及通信系统,用于通过对数字功率放大器中晶体管的设计,在保证数字功率放大器的量化精度的同时,降低数字功率放大器中晶体管的数量,从而,降低功率放大器的开销,提升功率放大器的整体性能。

6.第一方面,本技术提供一种数字功率放大器dpa,包括:解码器和n个晶体管集合,所述解码器包括输入端和n组输出端,所述解码器的输入端连接基带处理单元,所述解码器的n组输出端分别连接所述n个晶体管集合,所述n个晶体管集合在至少两个不同的工作电压范围下工作;所述解码器,用于接收来自所述基带处理单元的待放大信号对应的k个量化电平,将所述k个量化电平中位于同一工作电压范围内的目标量化电平发送给工作在所述工作电压范围下的晶体管集合;所述n为大于1的正整数,所述k为正整数;所述n个晶体管集

合,用于分别放大各自接收到的所述目标量化电平。

7.通过上述实现方式,n个晶体管集合在至少两个不同的工作电压范围下工作,从而,使得每个晶体管集合最多在其工作电压范围下放大相应的量化电平,从而,每个晶体管集合对应放大的量化比特位的数量最多为其工作电压范围下对应的量化电平的数量,远小于现有技术中,dpa中的所有的晶体管都位于相同的工作电压下工作时dpa中的晶体管的数量与量化比特位的数量呈指数关系的数量。从而,dpa在相同量化精度下需要设置的晶体管的数量可以显著减少,同时也降低了功率放大器的成本和复杂度,也降低了通信系统中功率放大器的开销。

8.一种可能的实现方式,所述n个晶体管集合中存在至少两个晶体管集合工作在所述第一工作电压范围下,所述第一工作电压范围包含电压值不重叠的至少两个电压子范围,所述至少两个电压子范围与所述至少两个晶体管集合一一对应;所述解码器,用于将所述k个量化电平中位于同一电压子范围内的目标量化电平发送给所述电压子范围对应的晶体管集合;所述电压子范围对应的晶体管集合,用于放大接收到的所述电压子范围内的量化电平。

9.通过上述实现方式,晶体管集合可以分别对应放大不重叠的电压子范围内的量化电平,因此,晶体管集合对应的量化比特位可以相应对应电压子范围的量化电平的量化比特位。

10.举例来说,在待放大信号都是基于不重叠的电压子范围组成的场景下,晶体管集合对应的量化比特位的数量之和即为待放大信号的量化比特位的数量。从而,可以简少晶体管集合中的晶体管的数量。

11.一种可能的实现方式,所述n个晶体管集合中存在两个晶体管集合对应同一工作电压范围,所述两个晶体管集合对应的量化比特位的数量不同;所述解码器,还用于:从所述k个量化电平中确定所述两个晶体管集合对应的工作电压范围内的目标量化电平,在所述两个晶体管集合中选择量化比特位的数量与所述目标量化电平对应的量化比特位的数量相同的目标晶体管集合,向所述目标晶体管集合发送所述工作电压范围对应的目标量化电平。

12.通过上述实现方式,晶体管集合中可以包括同一工作电压范围的两个晶体管集合,使得在待放大信号的量化比特位的数量不同时,解码器可以根据目标量化电平在工作电压范围内对应的多个晶体管集合,选择与目标量化电平匹配的目标晶体管集合,从而,提高数字功率放大器在放大不同量化比特位数量的信号时,可以更灵活的进行放大,以更好的降低dpa的功耗开销,提高dpa的放大性能。

13.一种可能的实现方式,针对于n个工作电压范围中的任一工作电压范围:所述工作电压范围的大小或工作在所述工作电压范围下的晶体管集合对应的量化比特位的数量,与待放大信号的模拟信号的包络信号的电压值在所述工作电压范围出现的概率相关;或者,所述工作电压范围的大小或工作在所述工作电压范围下的晶体管集合的量化比特位的数量与待放大信号的模拟信号的包络信号的功率谱密度在所述工作电压范围出现的概率相关。

14.通过上述实现方式,考虑到待放大信号的包络信号在不同电压值出现的概率不同,可以对应晶体管集合的工作电压范围的大小,考虑到工作电压范围越大,在相同量化精

度下,晶体管集合中的晶体管的数量越多,因此,可以基于待放大信号的包络信号在不同电压值出现的概率越大,工作电压范围越小,以降低设置的晶体管的数量。再比如,以基于待放大信号的包络信号在不同电压值出现的概率越小,划分的工作电压范围越大,以降低晶体管集合的数量,相应的,降低了晶体管的数量。

15.另外,考虑到待放大信号的包络信号在不同电压值出现的概率不同,反映到待放大信号的包络信号的功率谱密度也不同,例如,在待放大信号的包络信号的功率谱密度越大,意味着该位置需要的量化精度越高,因此,相应的,晶体管集合的工作电压范围越小,使得保证dpa量化精度的同时,降低dpa中的晶体管的数量。

16.一种可能的实现方式,所述晶体管集合中包括至少一个晶体管,所述至少一个晶体管采用同一工作电压。通过上述实现方式,晶体管集合可以共用电源,简化dpa的复杂度。

17.一种可能的实现方式,所述n个晶体管集合中的每个晶体管集合对应k个量化比特位中的一个或多个;所述解码器,用于确定所述目标量化电平在所述k个量化比特位中所处的目标量化比特位,将所述目标量化电平发送给所述目标量化比特位对应的晶体管集合。

18.通过上述实现方式,解码器根据每个晶体管集合可以分别对应放大k个量化电平中的一个或多个,向每个晶体管集合发送目标量化电平,以实现k个量化电平的放大,简化晶体管集合的复杂度。

19.一种可能的实现方式,所述晶体管集合中还包括:第一开关电容,所述第一开关电容连接所述晶体管集合中的全部晶体管;或者,分别连接所述晶体管集合中的各个晶体管的各个第二开关电容;所述第一开关电容或每个所述第二开关电容,用于接收所述晶体管集合对应的量化电平,并传输给所连接的晶体管;所述晶体管,用于对所述开关电容发送的所述量化电平进行放大。

20.通过上述实现方式,不同晶体管集合相互之间通过第一开关电容或第二开关电容隔离,降低不同晶体管集合或不同晶体管之间的干扰,提高功率放大器的性能。

21.一种可能的实现方式,所述dpa包括第一功放单元、第二功放单元和合路单元;所述第一功放单元为主功放、且所述第二功放单元为辅功放,或者,所述第一功放单元为辅功放、且所述第二功放单元为主功放;所述n个晶体管集合位于所述第一功放单元和/或第二功放单元中;所述第一功放单元,用于放大所述待放大信号的第一子信号,得到第一子放大信号,并发送给所述合路单元;所述第二功放单元,用于放大所述待放大信号的第二子信号,得到第二子放大信号,并发送给所述合路单元;所述合路单元,用于对所述第一子放大信号和所述第二子放大信号进行合路,获得所述待放大信号对应的目标放大信号。

22.通过上述实现方式,结合多赫蒂doherty架构提升功率放大器的功率回退性能,在降低功率放大器中晶体管的数量的同时,提升数字功率放大器的整体性能。

23.一种可能的实现方式,所述dpa还包括阻抗匹配网络,所述阻抗匹配网络用于与所述n个晶体管集合的阻抗匹配。

24.通过上述实现方式,使得dpa中的n个晶体管集合放大k个量化电平时,工作在阻抗匹配的状态下,降低n个晶体管集合的功耗,提高dpa的效率。

25.第二方面,本技术提供一种通信系统,包括:基带处理单元;与所述基带处理单元连接的至少一个如第一方面中任一项所述的dpa;与所述至少一个dpa连接的天线。

附图说明

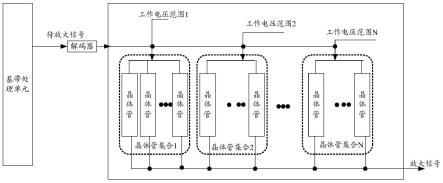

26.图1为本技术实施例提供的一种功率放大器的结构示意图;

27.图2为一种通信系统的结构示意图;

28.图3为一种通信系统的polar架构示意图;

29.图4为一种通信系统的同相信号正交信号(inphase-quadrature,iq)架构示意图;

30.图5为一种数字功率放大器的结构示意图;

31.图6为本技术实施例提供的一种通信系统的结构图;

32.图7a-图7b为一种时域包络信号的示意图;

33.图8为本技术实施例中的合成信号示意图;

34.图9为一种时域包络信号对应的功率谱密度的示意图;

35.图10a-图10c为本技术实施例提供的晶体管集合与电压范围的关系示意图;

36.图11为本技术实施例提供的一种晶体管的结构图;

37.图12为本技术实施例提供的一种通信系统的结构图;

38.图13为本技术实施例提供的一种数字功率放大器的结构图;

39.图14为本技术实施例提供的一种数字功率放大器的效率曲线示意图;

40.图15为本技术实施例提供的一种doherty功率放大器的结构示意图;

41.图16为一种功率放大器的工作效率曲线示意图;

42.图17为本技术实施例提供的一种射频系统的结构示意图。

具体实施方式

43.本技术实施例的技术方案可以应用于各种通信系统,例如:长期演进(long term evolution,lte)系统、lte频分双工(frequency division duplex,fdd)系统、lte时分双工(time division duplex,tdd)、第五代(5th generation,5g)系统或新无线(new radio,nr)等,在此不做限制。

44.下面结合附图并举实施例,对本技术提供的技术方案作进一步说明。应理解,本技术实施例中提供的系统结构和业务场景主要是为了解释本技术的技术方案的一些可能的实施方式,不应被解读为对本技术的技术方案的唯一性限定。本领域普通技术人员可以知晓,随着系统的演进,以及更新的业务场景的出现,本技术提供的技术方案对于相同或类似的技术问题仍然可以适用。

45.应理解,本技术实施例提供的技术方案,在以下具体实施例的介绍中,某些重复之处可能不再赘述,但应视为这些具体实施例之间已有相互引用,可以相互结合。

46.无线通信系统中,设备可分为提供无线网络服务的设备和使用无线网络服务的设备。提供无线网络服务的设备是指那些组成无线通信网络的设备,可简称为网络设备(network equipment),或网络单元(network element)。网络设备通常归属于运营商或基础设施提供商,并由这些厂商负责运营或维护。网络设备还可进一步分为无线接入网(radio access network,ran)设备以及核心网(core network,cn)设备。典型的ran设备包括基站(base station,bs)。

47.应理解,基站有时也可以被称为无线接入点(access point,ap),或发送接收点(transmission reception point,trp)。具体地,基站可以是5g新无线(new radio,nr)系

统中的通用节点b(generation node b,gnb),4g长期演进(long term evolution,lte)系统的演进节点b(evolutional node b,enb)。根据基站的物理形态或发射功率的不同,基站可被分为宏基站(macro base station)或微基站(micro base station)。微基站有时也被称为小基站或小小区(small cell)。

48.使用无线网络服务的设备可以为终端。终端,又可以称之为用户设备(user equipment,ue)、移动台(mobile station,ms)、移动终端(mobile terminal,mt)、终端设备等,是一种向用户提供语音或数据连通性的设备,也可以是物联网设备。例如,终端包括具有无线连接功能的手持式设备、车载设备等。终端可以是:手机(mobile phone)、平板电脑、笔记本电脑、掌上电脑、移动互联网设备(mobile internet device,mid)、可穿戴设备(例如智能手表、智能手环、计步器等),车载设备(例如,汽车、自行车、电动车、飞机、船舶、火车、高铁等)、虚拟现实(virtual reality,vr)设备、增强现实(augmented reality,ar)设备、工业控制(industrial control)中的无线终端、智能家居设备(例如,冰箱、电视、空调、电表等)、智能机器人、车间设备、无人驾驶(self driving)中的无线终端、远程手术(remote medical surgery)中的无线终端、智能电网(smart grid)中的无线终端、运输安全(transportation safety)中的无线终端、智慧城市(smart city)中的无线终端,或智慧家庭(smart home)中的无线终端、飞行设备(例如,智能机器人、热气球、无人机、飞机)等。

49.为了不断满足人们对通信速率的增长诉求,通信系统正朝多通道演进,以实现速率与通道数量成比例增长,如已被广泛采用的多输入多输出(multi-input multi-output,mimo)技术,在第四、五代移动通信(4g、5g)和无线局域网(wireless local area network,wlan)系统中均被采用,以提升系统速率。以wlan为例,2013年制定的802.11ac标准定义了最大可支持mimo规模为4

×

4,2018年新一代802.11ax标准进一步将mimo规模提升至8

×

8,正在制定中的802.11be标准将可支持16

×

16mimo规模,随着mimo规模的不断提升,相应的wlan峰值通信速率也从gbps量级提升至几十gbps。随着mimo规模的增加,通信系统中配套的模拟通道数量成比例增长,如4

×

4mimo规模需要配套4套发射机系统和4套接收机系统。随之而来的问题是系统功耗与mimo规模同样成比例增加,导致大规模mimo系统的成本、散热、功耗等问题突显。

50.图1为本技术实施例提供的一种通信系统的结构示意图,该通信系统可以是本技术实施例中的终端或者网络设备,如图1所示,该通信系统可以包括多个组件,例如:存储器,基带处理单元,射频集成电路(radio frequency intergreted circuit,rfic),射频前端(radio frequency front end,rffe)器件,以及天线(antenna,ant)。这些组件可以通过各种互联总线或其他电连接方式耦合。

51.图1中,天线1表示第一天线,天线n表示第n天线,n为大于1的正整数。发送路径(tx),接收路径(rx),不同的数字表示不同的路径。每条路径均可以表示一个信号处理通道。其中,接收路径可以包括:反馈接收路径(fbrx),主接收路径(prx),分集接收路径(drx)。路径还可以区分高频、低频和基带,高频或低频可以是指频率的相对高低。应理解,图1中的标记和组件仅为示意目的,仅作为一种可能的实现方式,本技术实施例还包括其他的实现方式。例如,通信系统可以包括更多或更少的路径,包括更多或更少的组件。

52.图1中,射频集成电路(包括rfic 1,以及一个或多个可选的rfic 2)和射频前端器件可以共同组成射频子系统。根据信号的接收或发送电路的不同,射频子系统也可以分为

射频接收通道(rf receive path)和射频发射通道(rf transmit path)。其中,射频发射通道可通过天线发射射频信号,射频接收通道可通过天线接收射频信号,对该射频信号进行处理(如放大、滤波和下变频)以得到基带信号,并传递给基带处理单元。射频发送通道可接收来自基带处理单元的基带信号,对基带信号进行处理(如上变频、放大和滤波)以得到射频信号,并最终通过天线将该射频信号辐射到空间中。射频集成电路可以被称为射频处理芯片或射频芯片。

53.具体地,射频子系统可包括天线开关,天线调谐器,低噪声放大器(low noise amplifier,lna),功率放大器,混频器(mixer),本地振荡器(local oscillator,lo)、滤波器(filter)等电子器件,这些电子器件可以根据需要集成到一个或多个芯片中。射频集成电路可以被称为射频处理芯片或射频芯片。射频前端器件也可以是独立的芯片。射频芯片有时也被称为接收机(receiver)、发射机(transmitter)或收发机(transceiver)。随着技术的演进,天线有时也可以认为是射频子系统的一部分,并可集成到射频子系统的芯片中。天线、射频前端器件和射频芯片都可以单独制造和销售。当然,射频子系统也可以基于功耗和性能的需求,采用不同的器件或者不同的集成方式。例如,将属于射频前端的部分器件集成在射频芯片中,甚至将天线和射频前端器件都集成射频芯片中,该射频芯片也可以称为射频天线模组或天线模组。

54.此外,由于射频信号通常是模拟信号,基带处理单元处理的信号主要是数字信号,通信系统中还需要有模数转换器件。本技术实施例中,模数转换器件可以设置在基带处理单元中,也可以设置在射频子系统中。模数转换器件包括将模拟信号转换为数字信号的模数转换器(analog to digital converter,adc),以及将数字信号转换为模拟信号的数模转换器(digital to analog converter,dac)。

55.基带处理单元可包括一个或多个处理器。此外,基带处理单元还可以包括一种或多种硬件加速器(hardware accelerator,hac)。硬件加速器可用于专门完成一些处理开销较大的子功能,如数据包(data packet)的组装和解析,数据包的加解密等。这些子功能采用通用功能的处理器也可以实现,但是因为性能或成本的考量,采用硬件加速器可能更加合适。在具体的实现中,硬件加速器主要是用专用集成电路(application specified intergated circuit,asic)来实现。当然,硬件加速器中也可以包括一个或多个相对简单的处理器,如mcu。

56.本技术实施例中,基带处理单元和射频子系统共同组成通信子系统,为通信系统提供无线通信功能。通常,基带处理单元负责管理通信子系统的软硬件资源,并且可配置射频子系统的工作参数。基带处理单元的处理器中可以运行通信子系统的子操作系统,该子操作系统可以是嵌入式操作系统或实时操作系统(real time operating system)。

57.基带处理单元可以集成为一个或多个芯片,该芯片可称为基带处理芯片或基带芯片。基带处理单元可以作为独立的芯片,该芯片可被称调制解调器(modem)或modem芯片。基带处理单元可以按照modem芯片为单位来制造和销售。modem芯片有时也被称为基带处理器或移动处理器。此外,基带处理单元也可以进一步集成在更大的芯片中,以更大的芯片为单位来制造和销售。这个更大的芯片可以称为系统芯片,芯片系统或片上系统(system on a chip,soc),或简称为soc芯片。基带处理单元的软件组件可以在芯片出厂前内置在芯片的硬件组件中,也可以在芯片出厂后从其他非易失性存储器中导入到芯片的硬件组件中,或

者还可以通过网络以在线方式下载和更新这些软件组件。

58.此外,该通信系统中还包括存储器。此外,在基带处理单元中,还可以分别包括一个或多个缓存。具体实现中,存储器可分为易失性存储器(volatile memory)和非易失性存储器(non-volatile memory,nvm)。易失性存储器是指当电源供应中断后,内部存放的数据便会丢失的存储器。目前,易失性存储器主要是随机存取存储器(random access memory,ram),包括静态随机存取存储器(static ram,sram)和动态随机存取存储器(dynamic ram,dram)。非易失性存储器是指即使电源供应中断,内部存放的数据也不会因此丢失的存储器。常见的非易失性存储器包括只读存储器(read only memory,rom)、光盘、磁盘以及基于闪存(flash memory)技术的各种存储器等。通常来说,内存和缓存可以选用易失性存储器,大容量存储器可以选用非易失性存储器,例如闪存。

59.应理解,本技术实施例并不限于图1所示通信系统,图1中所示的设备的名称在这里仅作为一种示例说明,并不作为对本技术适用的通信系统架构中包括的设备或网元的限定。

60.图2为本技术实施例提供的另一种通信系统的结构示意图。图2示出了通信系统中用于射频信号处理的一些常见器件。应理解,图2中虽然只示出了一条射频接收通道和一条射频发射通道,本技术实施例中的通信系统不限于此,通信系统可以包括一条或多条射频接收通道以及一条或多条射频发射通道。其中,每一条射频发射通道可以包括数模转换器(dac)以及混频器等器件,每一条射频发射通道的输出信号在通过天线发射之前,还通过pa对射频信号发送通道的输出信号进行功率调整处理。射频接收通道可以包括混频器、滤波器以及模数转换器(adc)等器件,射频接收通道从天线接收的天线还可以经过低噪声放大器(low noise amplifier,lna)等器件进行处理。图2仅为示例,本技术实施例在此不再一一列举射频接收通道和射频发射通道中所包括的器件。

61.在数字通信系统中,为增大系统容量,可以对待传输的信息进行编码,符号可以表示信息的一个或多个二进制比特。每个符号被编码为载波的幅度和相位调制的不同组合,调制越高,对编码和调制的数据的分辨率要求也越高,相应的对功率放大器的线性度的要求也越高。

62.为保证调制后的变包络信号的保真发射,提高功率放大器的效率,降低功率放大器的功耗。在射频子系统中,可以通过数字pa(digital pa,dpa)进行功率放大。dpa结合了开关类pa的高效率特点,采用多比特位量化技术,将模拟信号转换为数字信号后,对数字信号中的每个量化比特位上的量化电平分别进行放大,从而根据放大后的每个量化电平,获得放大后的信号。

63.例如,一个20v的电压信号,在量化为10比特时,每个量化步长为20v/(2

10

)=20mv。即通过10个量化比特位对应的10个量化电平(即从量化比特的低位依次对应的量化电平为:20mv,40mv,80mv,

……

,29×

20mv),可以将该20v的模拟信号量化为10比特的数字信号。从而,针对10比特上的每个比特位上的量化电平分别进行放大,可以获得线性度较好的放大信号。

64.为保证dpa对数字信号中的每个量化电平的线性度要求,可以将数字信号的二进制编码方式转换为温度计编码方式,每个量化比特位上的量化比特值可以通过温度计编码后的编码值表示。从而,每个量化比特位上可以相应对应的量化电平也可以根据温度计编

码后的编码值确定。

65.例如,第i个量化比特位上的量化电平对应放大的晶体管个数为2

i-1,其中,i为小于k的整数。k为待放大信号对应的量化比特位的数量。每个晶体管对应放大的量化电平也可以由第i个量化比特位和量化步长确定。即在放大80mv的量化电平时,对应放大该量化电平的晶体管个数为2

2-1=3。在放大29×

20mv的量化电平时,对应放大该量化电平的晶体管个数为2

9-1。即将编码后的数字信号中每个量化电平发送给对应放大该量化电平的晶体管进行功率放大,从而保证dpa放大信号的线性度要求的同时,提升了功率放大器的效率。

66.下面以polar架构和iq架构介绍dpa的架构。如图3所示,在polar架构中,dpa接收基带处理单元的模拟信号,其中,模拟信号可以通过dac模块量化为数字信号,在将模拟信号转换为数字信号的过程中,为提高系统的线性度,可以将二进制码转换成温度计码。数字信号经过相应的滤波器,例如,升采样插值滤波器,将基带数据的低频信号转换为具有射频载波频率的高频信号,以提高信号的带外信噪比,进而满足协议的频谱的要求。再经过坐标旋转数字计算(coordinate rotation digital computer,cordic)单元分为幅度信号和相位信号,幅度信号输入至dpa,相位信号经过调制器变频为射频信号(也为相位调制(phase-modulated,pm)信号)输入至dpa,dpa根据输入的幅度信号和相位调制信号合成后进行放大,输出至天线。

67.如图4所示,iq架构中,输入信号包括同相输入信号i和正交输入信号q,输入信号中的i信号和q信号具有90度的相位差。将信号i和信号q,分别输入数模转换器(dac)1和数模转换器(dac)2中,在数模转换器1将信号i进行数模转换后输出至滤波器1,例如,滤波器1可采用低通滤波器,该滤波器1用于将数模转换器1输出信号中的高频滤掉;在数模转换器2信号q进行数模转换后输出至滤波器2,例如,滤波器2可采用低通滤波器,该滤波器2用于将数模转换器2输出信号中的高频滤掉;混频器将滤波器1和滤波器2输出的信号进行混频,输出一个射频载波。该射频载波的幅度调制(即功率放大)是通过dpa来实现,将i信号和q信号这两路信号输入至量化后的dpa进行合成,最后输出至天线。

68.下面以图3中polar架构的幅度信号的解码和放大举例说明,iq架构中i信号和q信号的放大过程可以参考图4示例中幅度信号的解码和驱动放大的过程。

69.如图5所示,dpa可以包括:解码器和晶体管阵列。其中,解码器用于接收基带处理单元发送的数字信号。例如,晶体管阵列中的晶体管可以是开关电容功率放大器(switched-capacitor power amplifier,scpa)。结合图3,数字信号中的幅度信号被传递到dpa的解码器,在幅度信号量化为k个比特时,幅度信号可以包括k个量化比特位对应的量化比特值,量化比特值可以表示为幅度控制码字(amplitude control word,acw)。解码器用于解码幅度信号中的幅度控制码字,确定出数字信号中的每个量化比特位上对应的量化电平,并确定每个量化电平相应驱动的dpa中的晶体管。

70.一种可能的实现方式,acw由二进制编码,例如,确定acw为4比特,即dpa的量化比特位的数量为4。每个比特位对应控制1个dpa的晶体管,此时dpa中的晶体管阵列由4个晶体管组成。相应的,解码器可以通过acw确定每个比特位对应的晶体管的开关情况。例如,在acw为1010时,由低位到高位的顺序,可以确定第0个比特位为0,对应的晶体管处于不工作状态,第1个比特位为1,对应的晶体管用于放大第1个比特位对应的量化电平,第2个比特位为0,对应的晶体管处于不工作状态,第3个比特位为1,对应的晶体管用于放大第3个比特位

对应的量化电平。

71.解码器将接收到的数字信号进行解码,确定驱动的dpa中的晶体管后,生成相应的量化电平。结合相位调制信号,数字与门将相位调制信号和来自解码器的量化电平合并,以产生量化电平的方波向量,这些方波向量馈入放大该量化电平的晶体管后,对该量化电平进行放大。放大后的所有量化电平传递给阻抗匹配网络,阻抗匹配网络用于调整dpa的负载阻抗。

72.为了满足在不同调制方式下的射频系统的线性度的要求,需要保证数模转换的量化精度和功率放大的线性度。

73.考虑到dpa在对二进制编码的数字信号的线性度较差,在数模转换的量化精度要求较高时,例如,即dpa的量化比特位的数量为15比特,此时,无法直接采用二进制编码驱动晶体管实现功率放大。一种可能的实现方式,每个编码比特全部由温度计编码控制的晶体管实现,即每增加一个量化比特位,dpa中增加的晶体管的数量呈指数增长。以量化比特位的数量为k为例,放大第i个量化比特位上对应的量化电平所需的晶体管数量为2i个,其中,i为小于k的整数。dpa中的晶体管的数量将达到2

k-1个。

74.举例来说,为了获得acw的量化比特位为15比特,即dpa的量化比特位的数量为15,且每个量化比特全部由温度计编码控制的晶体管实现,则dpa中的晶体管的数量将达到2

15-1个。例如,由低位到高位的顺序,第0个比特位对应的量化电平通过1个晶体管放大,第1个比特位对应通过3个晶体管放大,第2个比特位对应通过3个晶体管放大,第2个比特位对应通过7个晶体管放大,

…

,第14个比特位对应控制2

14-1个晶体管。

75.为减少晶体管的个数,另一种可能的方式,编码可以采用温度计码和二进制码混合编码的方式,还是以15比特为例,高位的10比特由采用温度计编码的晶体管实现,低位的5比特由采用二进制编码的晶体管实现,相应的,解码器根据高位的温度计编码方式,解码10比特中每个比特位,从而对应控制10比特中每个比特位的晶体管,并根据低位的二进制编码方式,解码5比特中每个比特位,从而对应控制5比特中每个比特位的晶体管。此时,dpa的晶体管包括(1023+5)个,同时在版图设计时,dpa还要考虑布局要求,例如,布局成32行

×

32列的晶体管阵列,导致整体电路中的解码器和dpa的晶体管阵列的版图设计难度增大。

76.整体来说,晶体管的数量与其dpa的量化比特位的数量成指数增长。dpa的量化精度与晶体管数量相关,而且两者呈指数关系。如果要进一步提高精度,例如,16比特的dpa精度,则晶体管数量可能达到(2047+5)个。随着晶体管的数量增加,版图的设计难度大大增加,同时需要设计更为复杂的解码器,额外增加了数字放大器的功耗。

77.基于上述问题,本技术提供一种数字功率放大器的可能的结构。如图6所示,数字功率放大器包括:解码器和n个晶体管集合,解码器包括输入端和n组输出端,解码器的输入端连接基带处理单元,解码器的n组输出端分别连接n个晶体管集合,n个晶体管集合在至少两个不同的工作电压范围下工作。

78.解码器,用于接收来自所述基带处理单元的待放大信号对应的k个量化电平,将所述k个量化电平中位于同一工作电压范围内的目标量化电平发送给工作在所述工作电压范围下的晶体管集合;所述n为大于1的正整数,所述k为正整数;所述n个晶体管集合,用于分别放大各自接收到的所述目标量化电平。

79.在一些实施例中,n个晶体管集合在至少两个不同的工作电压范围可以由待放大

信号所在的电压范围确定。待放大信号可以根据调制方式确定对应的电压范围。

80.举例来说,图7a所示为一种“ofdm+正交振幅调制(quadrature amplitude modulation,qam)”信号的时域包络信号,根据该时域包络信号,可以确定待放大信号所在的电压范围在[u1,u2]。u1小于u2,u1和u2为有理数。因此,根据待放大信号所在的电压范围进行划分,获得至少两个电压范围。例如,包括电压范围1,即[u1,u0],和电压范围2,即[u0,u2]。u0小于u2,且大于u1,u0为有理数。此时,n个晶体管集合对应工作的工作电压范围至少包括电压范围1,或电压范围2。在一些示例中,n个晶体管集合中的至少一个晶体管集合的工作电压范围1至少包括电压范围1,例如,[u1,u0’],u0’大于或等于u0,u0小于u2,且大于u1,u0’为有理数。该至少一个晶体管集合用于放大工作电压范围1内的量化电平。

[0081]

在一些实施例中,所述n个晶体管集合中的每个晶体管集合对应k个量化比特位中的一个或多个;从而,解码器,可以根据所述n个晶体管集合中的每个晶体管集合对应k个量化比特位中的一个或多个,确定所述目标量化电平在所述k个量化比特位中所处的目标量化比特位,将所述目标量化电平发送给所述目标量化比特位对应的晶体管集合。

[0082]

本技术中,晶体管集合对应的工作电压范围的形式也可以有多种,相应的,具体n个晶体管集合中的每个晶体管集合对应k个量化比特位中的一个或多个的方式可以有多种,下面以方式1~方式2举例说明。

[0083]

方式1,n个晶体管集合中存在至少两个晶体管集合工作在所述第一工作电压范围下,所述第一工作电压范围包含电压值不重叠的至少两个电压子范围,所述至少两个电压子范围与所述至少两个晶体管集合一一对应;

[0084]

解码器,用于将所述k个量化电平中位于同一电压子范围内的目标量化电平发送给所述电压子范围对应的晶体管集合;

[0085]

电压子范围对应的晶体管集合,用于放大接收到的所述电压子范围内的量化电平。

[0086]

举例来说,第一工作电压范围为待放大信号的范围,即[u1,u2],第一工作电压范围包含电压值不重叠的至少两个电压子范围为:电压子范围1,[u1,v1],电压子范围2,[v1,u2]。

[0087]

针对每个电压子范围,可以对应在该电压子范围的量化比特位的数量,从而,根据每个电压子范围的量化比特位的数量之和,确定第一工作电压范围的量化比特位的数量。相应的,基于dpa的量化比特位的数量(k),和每个电压子范围设置在该电压子范围对应的量化比特位的数量,可以确定晶体管集合中晶体管的数量。

[0088]

本技术中,每个电压范围或电压子范围对应的量化比特位的数量可以有多种实现方式,下面以电压范围为例,通过方式a~方式c举例说明。

[0089]

结合方式1,在方式a中,每个电压子范围的量化比特位的数量相同。即,第一工作电压范围对应的量化比特位的数量为12时,每个电压子范围的量化比特位的数量可以为6。

[0090]

考虑到晶体管集合的量化比特位与所述晶体管集合对应的工作电压范围相关。例如,电压子范围1对应dpa量化比特位为低位的量化比特位,电压子范围1对应dpa量化比特位为高位的量化比特位。

[0091]

结合图7a,电压子范围1对应dpa量化比特位低位的6个量化比特位,电压子范围2对应dpa量化比特位高位的6个量化比特位。电压子范围1对应晶体管集合中的晶体管用于

放大电压子范围1内的量化电平,电压子范围2对应晶体管集合中的晶体管用于放大电压子范围2内的量化电平,因此,第一工作电压范围所需的晶体管的数量最大为2

6-1。此时,dpa中放大第一工作电压范围的晶体管的数量为127。

[0092]

可选的,在电压子范围1对应的低比特位的晶体管集合,还可以结合二进制编码的方式,例如,包括3个二进制编码的比特位,和3个温度计编码的比特位。此时,第1个电压范围对应的晶体管集合的晶体管的数量为23+3。此时,dpa中晶体管的数量为64+11=75。

[0093]

再比如,如图7b所示,将图7a所示的时域包络信号的包络幅度所在的电压范围划分为6个电压范围,在一个电压范围对应一个晶体管集合的一个工作电压范围时,可以对应确定6个晶体管集合的6个工作电压范围,如图7b所示,还是以每个工作电压范围对应的量化比特位的数量相同为例。在dpa的量化比特位的数量为12时,每个工作电压范围的量化比特位的数量可以为2,因此,每个电压范围所需的晶体管的数量最大为2

2-1。此时,dpa中晶体管的数量为24。

[0094]

可以看出,通过上述方法,可以极大的减少相同dpa的量化比特位的数量下所需的晶体管的数量。例如,在确定晶体管的数量和待放大信号的量化比特位的数量后,可以相应的设置n,从而满足dpa精度、版图设计和成本控制的需要。

[0095]

基于n个晶体管集合工作于不同的连续的n个电压范围,不同的电压范围采用不同的电源为相应的晶体管集合供电。通过n个电压范围组合出dpa放大的模拟信号所在的电压范围。通过不同电压范围驱动相应的晶体管集合的功率放大器,以对不同幅度的iq信号进行功率放大。

[0096]

结合图7b所示,将时域包络信号的包络幅度的大小,划分为6个连续的电压范围,包括:[0,0.6]v,[0.6,1.2]v,

…

[3,3.6]v。因此,可以设置6个晶体管集合,每个晶体管集合的工作电压范围至少包括1个电压范围,用于放大该电压范围内的量化电平。

[0097]

例如,如图8所示,在某个时刻的待放大信号的电压幅度为2v时,可以确定出对应的量化电平位于第1个电压范围[0,0.6v],第2个电压范围[0.6v,1.2v]和第3个电压范围[1.2v,1.8v]的部分。还是以上述每个电压范围对应2个量化比特位,此时,该信号对应的量化比特值可以为0000000011111,即最低的2个比特位对应驱动第1个电压范围对应的晶体管集合中的晶体管,分别用于放大最低的2个比特位上的2个量化电平。依次的2个比特位对应驱动第2个电压范围对应的晶体管,分别用于放大该电压范围对应的2个比特位上的2个量化电平。第5个比特位对应驱动第3个电压范围中的部分晶体管,分别用于放大该电压范围对应的第5个比特位上的量化电平。从而,实现对上述5个量化比特位上的量化电平进行放大。

[0098]

结合方式1,在方式b中,电压范围的大小为根据待放大信号的模拟信号的包络信号的电压值在所述工作电压范围出现的概率确定的。或者,电压范围对应的量化比特位的数量为根据待放大信号的模拟信号的包络信号的电压值在所述工作电压范围出现的概率确定的。

[0099]

相应的,n个工作电压范围中的任一工作电压范围,所述工作电压范围的大小或工作在所述工作电压范围下的晶体管集合对应的量化比特位的数量,与待放大信号的模拟信号的包络信号的电压值在所述工作电压范围出现的概率相关。

[0100]

结合图7a所示,时域包络信号的幅度变化明显,而且包络信号幅度越大,概率越

低,包络信号幅度越小,包络信号幅度值出现的概率越高。

[0101]

因此,考虑到包络信号幅度出现的概率越低,dpa对其放大的可能性越低,为降低dpa的成本,可以根据包络信号幅度出现的概率来划分n个电压范围,概率越大的电压范围的大小越小,概率越小的电压范围的大小越大,以保证信号发射的线性度要求。

[0102]

结合方式1,在方式c中,电压范围的大小为根据所述电压范围对应在待放大信号的包络信号的功率谱密度中的概率确定的。或者,电压范围对应的量化比特位的数量为根据所述电压范围对应在待放大信号的包络信号的功率谱密度中的概率确定的。

[0103]

相应的,针对于n个工作电压范围中的任一工作电压范围:所述工作电压范围的大小或工作在所述工作电压范围下的晶体管集合的量化比特位的数量与待放大信号的模拟信号的包络信号的功率谱密度在所述工作电压范围出现的概率相关。

[0104]

如图9所示,图9的横轴为待放大信号的模拟信号的包络信号的幅度值取对数后的归一化值,可以对应晶体管的功率回退量,晶体管在功率回退范围对应的电压范围内工作时,可以保证晶体管的效率较高。纵轴为不同幅度值对应的功率谱密度,即可以对应晶体管放大不同电压范围内的量化电平的概率,可以看到,对于“ofdm+qam”信号的时域包络信号,不同包络信号的幅度值出现的概率不同。电压范围3和电压范围4对应的概率最高,电压范围1和电压范围6对应的概率最低。

[0105]

进一步的,考虑到功率谱密度越高的区域,工作在该电压范围的晶体管频率越大,而在功率回退后,可能导致效率降低,因此,可以将功率谱密度概率越高的区域划分的电压范围越小,以降低放大该电压范围内的量化电平的晶体管的功率回退的大小,保证信号发射的线性度要求。

[0106]

举例来说,在n个晶体管集合分别对应放大n个电压范围内的量化电平,且n个电压范围连续且不重叠时,dpa的量化比特位的数量为所述n个晶体管集合对应放大n个电压范围的量化电平的量化比特位的数量之和。因此,在确定n个晶体管集合分别对应放大n个电压范围的量化比特位的数量及量化电平后,可以相应确定放大该电压范围内的量化电平的晶体管集合中晶体管的数量。下面通过方式b1和方式b2举例说明。

[0107]

结合方式1和方式b,在方式b1中,电压范围对应的量化比特位的数量与该电压范围的大小相关。例如,在电压范围较大时,可以设置较多的量化比特位的数量。结合图9所示,第1个电压范围较大,可以设置较多的量化比特位的数量,例如,3个比特;第3个电压范围较小,可以设置较少的量化比特位的数量,例如,2个比特。

[0108]

结合方式1和方式b,在方式b2中,电压范围对应的量化比特位的数量可以是根据待放大信号的模拟信号的包络信号的电压范围中所述电压范围出现的概率确定的。

[0109]

例如,在模拟信号的包络信号的电压范围中,该电压范围出现的概率较大时,可以设置较多的量化比特位的数量。结合图9,第1个电压范围在模拟信号的包络信号的电压范围内出现的概率较小,可以设置较少的量化比特位的数量,例如,2个比特。第3个电压范围较小,可以设置较多的量化比特位的数量,例如,3个比特。第4个电压范围较小,可以设置较多的量化比特位的数量,例如,4个比特。第6个电压在模拟信号的包络信号的电压范围出现的概率较小,可以设置较少的量化比特位的数量,例如,1个比特。示例性的,由低位到高位,可以依次对应2.6比特、3比特、4比特、3比特、3比特、2比特、1比特。

[0110]

结合方式1和方式c,在上述连续的n个电压范围的场景下,n个晶体管集合分别对

应的量化比特位组成dpa的量化比特位。此时,每个晶体管集合对应放大的电压范围可以根据图9中的功率谱密度确定。相应的,每个电压范围对应的量化比特位的数量,也可以根据图9中的功率谱密度确定。例如,根据电压范围的大小,确定电压范围的量化比特位的数量。再比如,根据所述电压范围对应的功率谱密度在待放大信号的模拟信号的包络信号的功率谱密度中的概率,确定该电压范围的量化比特位的数量。具体的方式可以参考上述方式b1和方式b2,在此不再赘述。

[0111]

通过该方式,将功率谱密度越高的区域工作的晶体管集合的量化精度更高,可以更好的保证待放大信号的线性度要求。

[0112]

方式2,n个晶体管集合对应放大的量化电平所在的n个电压范围可以是不连续的。例如,至少存在两个电压范围可以是重叠的。此处的重叠可以是部分重叠,也可以是全部重叠。

[0113]

在一些实施例中,n个晶体管集合中存在两个晶体管集合对应同一工作电压范围,所述两个晶体管集合对应的量化比特位的数量不同。

[0114]

此时,解码器,还可以用于从所述k个量化电平中确定所述两个晶体管集合对应的工作电压范围内的目标量化电平,在所述两个晶体管集合中选择量化比特位的数量与所述目标量化电平对应的量化比特位的数量相同的目标晶体管集合,向所述目标晶体管集合发送所述工作电压范围对应的目标量化电平。

[0115]

举例来说,如图10a所示,n个晶体管集合中包括晶体管集合3-1、晶体管集合3-2,晶体管集合3-1对应的工作电压范围包括电压范围3,晶体管集合3-2对应的工作电压范围包括电压范围3,电压范围3小于待放大信号对应的电压范围。其中,晶体管集合3-1对应的量化比特位的数量为k1,晶体管集合3-2对应的量化比特位的数量为k2,其中,k1和k2为小于k的正整数。在k为不同的取值时,即待放大信号的量化精度不同时,输入的电压范围3中的量化电平的量化比特位的数量可能发生变化,可以根据晶体管集合3-1和晶体管集合3-2对应的量化比特位的数量,选择与所述目标量化电平对应的量化比特位的数量相同的目标晶体管集合,例如,在电压范围3的目标量化电平对应的量化比特位的数量为k1时,则可以确定目标晶体管集合为晶体管集合3-1。从而,解码器将电压范围3中的k1个量化电平输入至晶体管集合3-1,以实现对k1个量化电平的放大。

[0116]

从而,基于不同的量化精度的要求,选择相应电压范围内量化精度匹配的晶体管集合,提高dpa放大信号的灵活性和适用范围。

[0117]

下面以待放大信号对应的电压范围为例,举例说明,通过设置不同晶体管集合对应工作的工作电压范围,及对应放大的量化电平所处的电压范围,实现待放大信号的量化精度的调整。下面以方式2-1和方式2-2举例说明。

[0118]

方式2-1,如图10b所示,将图7a所示的时域包络信号的包络幅度所在的电压范围划分为4个电压范围,分别为[u1,v2],[v2,v1],[v1,v3],[v3,u2]。

[0119]

此时,假设第1个晶体管集合的工作电压范围对应[u1,v1],第2个晶体管集合的工作电压范围对应[v2,v3],第3个晶体管集合的工作电压范围对应[v3,u2]。其中,v1大于v2,v3大于v4。第1个晶体管集合的量化比特位的数量为7,第2个晶体管集合的量化比特位的数量为8,第3个晶体管集合的量化比特位的数量为5。

[0120]

解码器可以根据每个电压范围对应的量化比特位的数量,及每个晶体管集合对应

的量化比特的数量,确定每个晶体管集合对应放大的电压范围内的量化电平。

[0121]

举例来说,在dpa的量化比特位的数量为12时,从低到高对应的每个电压范围的量化比特位的数量分别为3,4,4,2时,可以通过第1个晶体管集合放大电压范围[u1,v2]和[v2,v1]中的7个量化电平。通过第3个晶体管集合放大电压范围[v1,v3],[v3,u2]中的6个量化电平。

[0122]

例如,在dpa的量化比特位的数量为10时,从低到高对应的每个电压范围的量化比特位的数量分别为2,4,4,1时,可以通过第1个晶体管集合放大电压范围[u1,v2]中的2个量化电平,通过第2个晶体管集合放大电压范围[v2,v1]和[v1,v3]中的8个量化电平,通过第3个晶体管集合放大电压范围[v4,u2]中的1个量化电平。

[0123]

方式2-2,n个晶体管集合对应放大的量化电平的电压范围部分重叠。

[0124]

举例来说,如图10c所示,将图7a所示的时域包络信号的包络幅度所在的电压范围划分为5个电压范围,例如,从小到大依次为[u1,v2],[v2,v1],[v1,v4],[v4,v3],[v3,u2]。

[0125]

相应的,3个晶体管集合的工作电压范围分别为[u1,v1],[v2,v3],[v1,u2],且分别放大的电压范围也为[u1,v1],[v2,v3],[v1,u2]。其中,v1大于v2,u2大于v1。

[0126]

举例来说,结合图10c所示,可以确定出3个不重叠的电压范围:第1个不重叠的电压范围对应[u1,v2],第2个不重叠的电压范围对应[v2,v4],第3个不重叠的电压范围对应[v4,u2]。确定出2个重叠的电压范围:第1个重叠的电压范围对应[v2,v1],第2个重叠的电压范围对应[v4,v3]。在重叠的电压范围内,可以相应的选择量化比特位对应的目标晶体管集合。

[0127]

举例来说,在dpa的量化比特位的数量为10时,假设解码器可以依次确定电压范围对应的量化比特位数都为2。此时,第1-2个电压范围内的4个量化电平可以通过第1个晶体管集合放大,第3个电压范围内的2个量化比特位的量化电平可以通过第2个晶体管集合放大,第4-5个电压范围内的4个量化电平可以通过第3个晶体管集合放大。当然,还可以通过其他方式确定每个晶体管集合放大的量化电平,只要晶体管集合有能力放大该量化电平即可。

[0128]

通过上述方法,可以基于不同的信号,选择不同的工作电压范围对信号进行放大。或者,还可以基于不同的量化精度的要求,选择不同的工作电压范围对信号进行放大。从而,可以更灵活的适应不同信号的量化精度的要求,提高dpa的灵活性,而无需重新设计dpa的版图。

[0129]

在一些实施例中,考虑到晶体管集合工作的电压不同,因此,晶体管集合工作的工作电压可能不同,为了保证电路的正常工作,不同晶体管集合中的晶体管的结构也可以不同。例如,如图11所示,为避免晶体管被击穿,工作电压越高,需要堆叠的晶体管数量越多。示例性的,本技术中的晶体管可以是mos管,还可以是其他的开关类pa的晶体管,在此不做限定。以40nm cmos工艺为例,基于该工艺实现图11所示三种类型的晶体管,三种类型的晶体管的工作电压的最大值分别为1.2v、2.4v、3.6v。因此,在1.2v以下对应的电压范围的晶体管集合中的晶体管可以使用晶体管1,在2.4v以下对应电压范围的晶体管集合中的晶体管可以使用晶体管2,在2.4v以下对应电压范围的晶体管集合中的晶体管可以使用晶体管3。需要说明的是,由于晶体管2和晶体管3中包括多个晶体管的叠加,因此,可能会存在多个供电端口,例如,晶体管2包括2个工作电压的供电端口,晶体管3包括3个工作电压的供电端

口,具体供电电压可以根据实际需要设置,在此不做限定。

[0130]

在一些实施例中,所述晶体管集合中包括至少一个晶体管,所述至少一个晶体管采用同一工作电压。从而,可以简化电路的设计方案,降低版图设计成本和工艺难度。

[0131]

举例来说,如图12所示,所述晶体管集合中还可以包括:第一开关电容,所述第一开关电容连接所述晶体管集合中的全部晶体管。所述第一开关电容,用于接收所述晶体管集合对应的量化电平,并传输给所连接的晶体管;所述晶体管,用于对所述开关电容发送的所述量化电平进行放大。

[0132]

再举例来说,如图13所示,所述晶体管集合中还可以包括:分别连接所述晶体管集合中的各个晶体管的各个第二开关电容;每个所述第二开关电容,用于接收所述晶体管集合对应的量化电平,并传输给所连接的晶体管;所述晶体管,用于对所述开关电容发送的所述量化电平进行放大。

[0133]

在另一些实施例中,所述晶体管集合中的每个晶体管的工作电压可以为不同的工作电压,也可以为相同的工作电压。每个晶体管集合中的晶体管工作于不同的工作电压。晶体管集合中的晶体管采用开关电容的架构,每个开关电容由各自的晶体管对应放大的量化电平控制开启或关闭。

[0134]

通过上述方法,由于晶体管集合中的第一开关电容或第二开关电容,可以使得不同晶体管集合之间的电源互不影响,降低dpa的功耗。

[0135]

一种可能的实现方式,dpa中可以包括阻抗匹配网络,该阻抗匹配网络可以用于匹配n个晶体管集合中的阻抗。例如,如图13所示的电阻,可以用于匹配n个晶体管集合的阻抗。

[0136]

可选的,如图13所示,dpa中还可以包括电感,用来实现和dpa中的电容(例如,第一开关电容,或第二开关电容等)的谐振,控制dpa的工作频率。

[0137]

一种可能的实现方式中,晶体管集合中的每个晶体管的工作电压为相同的工作电压。以简化电路的实现,降低版图的设计难度。

[0138]

下面对本技术的dpa的效率计算分析:

[0139][0140][0141]

其中,voutn为第n个晶体管集合的输出电压,vn为每个晶体管集合的工作电压,cn为每个晶体管集合的电容总量,ratio_n为每个晶体管集合内开关开启的比例;poutn为第n个晶体管集合的输出功率。

[0142]

各个晶体管集合下的开关电容的损耗计算如下:

[0143][0144][0145]

需要说明的是,在确定第2个晶体管集合的开关电容的损耗psc2时,首先假设其余晶体管集合group均接地,计算第2个晶体管集合group2单独工作时的损耗,但是由于此时

第1个晶体管集合group1在正常工作,此时第2个晶体管集合group2和第1个晶体管集合group1之间的相对压差为v2-v1,所以需要减去第1个晶体管集合的开关电容的损耗psc1。晶体管集合group3~6以此类推,在此不再赘述。根据晶体管集合输出功率pout和晶体管集合的开关电容的损耗pcs可计算出效率,如图14所示,与class-b pa和polar dpa的效率进行对比,可以明显看到,本技术实施例中的dpa对功率放大器的效率的提升明显。

[0146]

本技术实施例中,dpa还可以与负载调制技术、电源调制技术等方法结合,可进一步提升功率放大器的效率,从而降低dpa的功耗。

[0147]

下面以负载调制中的doherty功率放大器为例,进行说明。图15中示例性的示出了doherty功率放大器的结构示意图,其包括第一功放单元、第二功放单元和阻抗变换网络。所述第一功放单元为主功放、且所述第二功放单元为辅功放,或者,所述第一功放单元为辅功放、且所述第二功放单元为主功放。随着输入信号功率强度的不同,可以将doherty功率放大器的工作区域大致分为三个阶段:低功率区域、回退区域、满功率区域。下面结合图16中doherty功率放大器的效率曲线图,对以上三个阶段进行具体描述:

[0148]

1)低功率区域

[0149]

在低功率区域,辅功放的通路(peak路)的偏置模式为c类,其输入功率不足以驱动使其工作,此时peak路处于开路状态。同时,主功放的通路(main路)阻抗保持不变。随着功率放大器的输入功率增大,主功放进入饱和状态,电压达到满摆幅,实现doherty功率放大器工作过程中的第一个高功率点。例如,如图16所示,功率放大器的第一个高功率点对应的功率回退点为6db,即功率放大器的输入功率相比功率放大器中的主功放和辅功放都为满功率时少6db。

[0150]

2)功率回退区域

[0151]

随着功率放大器的输入功率的逐渐增强,peak路打开,此时main路阻抗逐渐变小,但其电压一直为满摆幅,保持饱和状态;同时,peak路阻抗也逐渐变小,电压逐渐升高,但并未达到饱和状态,因此doherty功率放大器的工作效率略微下降。

[0152]

3)满功率区域

[0153]

随着功率放大器的输入功率进一步增强,main路和peak路均达到饱和状态,电压均达到满摆幅,此时doherty功率放大器实现工作过程中的第二个高功率点。例如,如图16所示,第二个高功率点对应功率放大器的功率回退点为0db。此时,功率放大器在整个系统中最高可输出功率状态。

[0154]

可以看出,当功放工作远离满功率区,进入功率回退区(如图16所示的功率回退量0db~6db)时,仍可以保证较高的功率放大器的效率,功耗较低。因此,本技术中的数字功率放大器还可以结合doherty原理,提高dpa的功率放大器的效率。

[0155]

在一些实施例中,本技术实施例中的dpa可以包括第一功放单元、第二功放单元和合路单元;所述n个晶体管集合位于所述第一功放单元和/或第二功放单元中。

[0156]

其中,第一功放单元,用于放大所述待放大信号的第一子信号,得到第一子放大信号,并发送给所述合路单元;第二功放单元,用于放大所述待放大信号的第二子信号,得到第二子放大信号,并发送给所述合路单元;合路单元,用于对所述第一子放大信号和所述第二子放大信号进行合路,获得所述待放大信号对应的目标放大信号。

[0157]

此时,来自基带处理单元的信号可以被分为第一子信号和第二子信号,并分为两

路分别输入至第一功放单元和第二功放单元。从而,第一子信号可以由第一功放单元进行放大,第二子信号可以有第二功放单元进行放大。经过第一功放单元放大后的第一子放大信号,和经过第二功放单元放大后的第二子放大信号可以通过合路单元合路,从而,获得待放大信号对应的目标放大信号。

[0158]

通过第一功放单元和/或第二功放单元结合本技术中的dpa中的n个晶体管集合的功率放大方式,可以降低第一功放单元和/或第二功放单元中所需的晶体管的数量,提高功放的效率和功放的效果。

[0159]

再比如,dpa中还可以结合异相outphasing负载调制技术,进一步提高dpa的整体效率;如图17所示,为异相架构的射频功率放大系统的结构示意图,信号控制系统(signal control system,scs)将输入的一路基带数字信号分路为两路数字信号输出,针对scs输出的每路数字信号,由数模转换器将其转换为模拟信号,再由模拟正交调制(analog quadrature modulation,aqm)模块对该模拟信号进行正交调制,输出射频信号至第一功放单元和第二功放单元进行功率放大;在合路器将两路射频信号进行合路。具体第一功放单元和第二功放单元的设置方式可以参考上述图17中的第一功放单元和第二功放单元的设置方式,在此不再赘述。

[0160]

为了进一步提高dpa的效率,本技术实施例中,还可以结合其他负载调制技术和电源调制技术,如基于变压器的功率合成网络负载调制、基于class-g的双电源实现电源调制等方式,实现深回退区效率的提升。

[0161]

需要说明的是,本技术中所涉及的连接,描述两个对象的连接关系,可以表示两种连接关系,例如,a和b连接,可以表示:a与b直接连接,a通过c和b连接这两种情况。另外,需要理解的是,在本技术的描述中,“第一”、“第二”等词汇,仅用于区分描述的目的,而不能理解为指示或暗示相对重要性,也不能理解为指示或暗示顺序。此外,本技术实施例中提供的系统结构和业务场景主要是为了解释本技术的技术方案的一些可能的实施方式,不应被解读为对本技术的技术方案的唯一性限定。本领域普通技术人员可以知晓,随着系统的演进,以及更新的业务场景的出现,本技术提供的技术方案对于相同或类似的技术问题仍然可以适用。

[0162]

显然,本领域的技术人员可以对本技术进行各种改动和变型而不脱离本技术的保护范围。这样,倘若本技术的这些修改和变型属于本技术权利要求及其等同技术的范围之内,则本技术也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1