模拟数字转换器装置与校正电路控制方法与流程

1.本揭示内容是有关于一种模拟数字转换器装置与校正电路控制方法,且特别是指一种时间交错式模拟数字转换器装置与校正电路控制方法。

背景技术:

2.模拟数字转换器(analog-to-digital converter,adc)常应用于各种电子装置中,用于转换模拟信号至数字信号以进行信号处理。在实际应用中,adc会因为增益误差、偏移误差或时序误差影响其本身的解析度或线性度。其中,当输入信号微弱(例如,振幅过小或功率过小)时,现有技术针对前述三种误差所进行校正容易受到影响,使得不同通道间的相位误差可能会不正确地收敛。

技术实现要素:

3.本揭示内容的一态样为一模拟数字转换器装置。该模拟数字转换器装置包括多个模拟数字转换电路、一校正电路以及一控制电路。这些模拟数字转换电路用以根据交错的多个时脉信号转换一输入信号,以产生多个第一量化输出。该校正电路用以根据这些第一量化输出执行至少一误差运算来产生至少一校正信息,利用该至少一校正信息校正这些第一量化输出来产生多个第二量化输出,且根据这些第二量化输出分析这些时脉信号的多个时间差信息来产生多个调整信号,其中这些调整信号用以降低这些模拟数字转换电路的一时脉偏斜。该控制电路接收这些第一量化输出,并用以分析这些第一量化输出,以产生至少一控制信号至该校正电路,其中该至少一控制信号用于控制该校正电路选择性地执行该至少一误差运算,以及选择性地分析这些时脉信号的这些时间差信息。

4.于另一实施例中,该控制电路分析第n周期的这些第一量化输出,以产生第n周期的该至少一控制信号,该校正电路根据第n周期的该至少一控制信号选择性地对第n+1周期的这些第一量化输出执行该至少一误差运算,以及选择性地分析第n+1周期的这些时脉信号的这些时间差信息,其中n为正整数。

5.于另一实施例中,当该校正电路对第n+1周期的这些第一量化输出执行该至少一误差运算时,该校正电路利用根据第n+1周期的这些第一量化输出产生的该至少一校正信息校正第n+1周期的这些第一量化输出,来产生第n+1周期的这些第二量化输出。

6.于另一实施例中,当该校正电路未对第n+1周期的这些第一量化输出执行该至少一误差运算时,该校正电路利用先前产生的该至少一校正信息校正第n+1周期的这些第一量化输出,来产生第n+1周期的这些第二量化输出。

7.于另一实施例中,当该校正电路分析第n+1周期的这些时脉信号的这些时间差信息时,该校正电路分析第n+1周期的这些第二量化输出来产生第n+1周期的这些调整信号。

8.于另一实施例中,当该校正电路未分析第n+1周期的这些时脉信号的这些时间差信息时,该校正电路输出第n周期的这些调整信号。

9.于另一实施例中,该控制电路包含:多个绝对值电路,用以接收这些第一量化输出

以输出多个绝对值信号,其中每一绝对值电路用以根据这些第一量化输出中的一对应第一量化输出执行一绝对值运算,以产生这些绝对值信号中的一对应绝对值信号;一平均电路,用以执行一平均运算来平均这些绝对值信号,以产生一平均信号;一滤波电路,用以对该平均信号进行滤波操作;以及一比较电路,用以比较滤波后的该平均信号与至少一临界值,以产生该至少一控制信号。

10.于另一实施例中,该校正电路包含:一偏斜调整电路,用以分析这些第二量化输出来产生这些调整信号至这些模拟数字转换电路。

11.于另一实施例中,该至少一校正信息包含一增益校正信息,该至少一误差运算包含一增益误差运算,该校正电路还包含:一增益校正电路,用以根据这些第一量化输出执行该增益误差运算来产生该增益校正信息,且利用该增益校正信息产生这些第二量化输出。

12.于另一实施例中,该至少一校正信息还包含一偏移校正信息,该至少一误差运算还包含一偏移误差运算,该校正电路还包含:一偏移校正电路,接收这些第一量化输出,用以根据这些第一量化输出执行该偏移误差运算来产生该偏移校正信息,且利用该偏移校正信息校正这些第一量化输出来产生多个第三量化输出,其中该增益校正电路利用该增益校正信息校正这些第三量化输出来产生这些第二量化输出。

13.本案的另一态样为一校正电路控制方法。该校正电路控制方法包含:通过一控制电路接收多个模拟数字转换电路根据交错的多个时脉信号所产生的多个第一量化输出;通过该控制电路分析这些第一量化输出,以产生至少一控制信号至一校正电路;通过该校正电路,根据该至少一控制信号选择性地执行至少一误差运算来产生至少一校正信息,以及选择性地分析这些时脉信号的多个时间差信息来产生多个调整信号,其中这些调整信号用以降低这些模拟数字转换电路的一时脉偏斜;以及通过该校正电路校正这些第一量化输出来产生多个第二量化输出。

14.于另一实施例中,产生该至少一控制信号包含:根据这些第一量化输出中的一对应第一量化输出执行一绝对值运算,以产生多个绝对值信号中的一对应绝对值信号;执行一平均运算来平均这些绝对值信号,以产生一平均信号;对该平均信号进行滤波操作;以及比较滤波后的该平均信号与至少一临界值,以产生该至少一控制信号。

15.于另一实施例中,产生这些调整信号包含:通过该校正电路的一偏斜调整电路分析这些第二量化输出来产生这些调整信号至这些模拟数字转换电路。

16.于另一实施例中,该至少一校正信息包含一增益校正信息,该至少一误差运算包含一增益误差运算,产生这些第二量化输出包含:通过该校正电路的一增益校正电路根据这些第一量化输出执行该增益误差运算来产生该增益校正信息,且利用该增益校正信息产生这些第二量化输出。

17.于另一实施例中,该至少一校正信息还包含一偏移校正信息,该至少一误差运算还包含一偏移误差运算,产生这些第二量化输出还包含:通过该校正电路的一偏移校正电路接收这些第一量化输出;以及通过该偏移校正电路根据这些第一量化输出执行该偏移误差运算来产生该偏移校正信息,且利用该偏移校正信息校正这些第一量化输出来产生多个第三量化输出,其中该增益校正电路利用该增益校正信息校正这些第三量化输出来产生这些第二量化输出。

18.综上,本揭示的adc装置以及校正电路控制方法通过控制电路分析多个模拟数字

转换电路所产生的多个第一量化输出,以产生用于控制校正电路的至少一控制信号。在输入信号微弱(例如,振幅过小或功率过小)的情况下,adc装置通过至少一控制信号控制校正电路根据先前产生的校正信息产生多个第二量化输出(或/及控制校正电路输出先前产生的多个调整信号),以避免校正电路所进行的校正因为输入信号微弱而受影响的问题。如此一来,也可解决多个模拟数字转换电路之间的相位误差不正确地收敛的问题。

附图说明

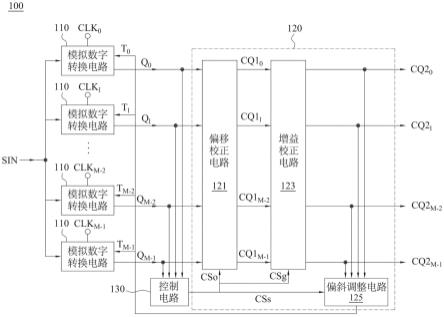

19.图1a是根据本案部分实施例绘示的一种模拟数字转换器装置的示意图;

20.图1b是根据本案部分实施例绘示的图1a中多个时脉信号的波形示意图;

21.图2是根据本案部分实施例绘示的一种模拟数字转换器装置中的控制电路的示意图;

22.图3是根据本案部分实施例绘示的一种校正电路控制方法的流程图。

23.【符号说明】

24.100:模拟数字转换器装置

25.110:模拟数字转换电路

26.120:校正电路

27.121:偏移校正电路

28.123:增益校正电路

29.125:偏斜调整电路

30.130:控制电路

31.131:绝对值电路

32.133:平均电路

33.135:滤波电路

34.137:比较电路

35.300:校正电路控制方法

36.331:第一运算电路

37.333:第二运算电路

38.clk0~clk

m-1

:时脉信号

39.cso,csg,css:控制信号

40.q0~q

m-1

,cq10~cq1

m-1

,cq20~cq2

m-1

:量化输出

41.a0~a

m-1

:绝对值信号

42.t0~t

m-1

:调整信号

43.sin:输入信号

44.avg:平均信号

45.sum:加总信号

46.th:临界值

47.fs:取样频率

48.sp:取样周期

49.s1,s2,s3:取样时间

50.s310~s340:步骤

具体实施方式

51.下文是举实施例配合所附附图作详细说明,但所描述的具体实施例仅用以解释本案,并不用来限定本案,而结构操作的描述非用以限制其执行的顺序,任何由元件重新组合的结构,所产生具有均等功效的装置,皆为本揭示内容所涵盖的范围。

52.在全篇说明书与权利要求书所使用的用词(terms),除有特别注明外,通常具有每个用词使用在此领域中、在此揭示的内容中与特殊内容中的平常意义。

53.关于本文中所使用的“耦接”或“连接”,均可指二或多个元件相互直接作实体或电性接触,或是相互间接作实体或电性接触,亦可指二或多个元件相互操作或动作。

54.请参阅图1a、图1b,图1a为根据本案部分实施例绘示的一种模拟数字转换器(analog-to-digital converter,adc)装置100的示意图。图1b为根据本案部分实施例绘示的图1a中多个时脉信号clk0~clk

m-1

的波形示意图。于部分实施例中,adc装置100操作为具有多通道的一时间交错式(time-interleaved)adc。

55.于部分实施例中,adc装置100包含多个模拟数字转换电路110、校正电路120以及控制电路130。值得注意的是,每一个模拟数字转换电路110操作为单一通道。换言之,adc装置100包含m个通道。于部分实施例中,m为一偶数。如图1a所示,每一个模拟数字转换电路110用以根据多个时脉信号clk0~clk

m-1

的其中的一对输入信号sin进行模拟数字转换,以产生多个量化输出q0~q

m-1

的其中之一。

56.如图1b所示,多个时脉信号clk0~clk

m-1

中两个邻近的时脉信号彼此之间存在有一时间间隔,因此,相邻的2个通道会在不同时间执行取样操作与模拟数字转换。举例而言,第1个通道(即根据时脉信号clk0操作的模拟数字转换电路110)于第1个取样时间s1对输入信号sin进行取样,并进行模拟数字转换,第2个通道(即根据时脉信号clk1操作的模拟数字转换电路110)于第2个取样时间s2对输入信号sin进行取样,并进行模拟数字转换,且第3个通道(即根据时脉信号clk2操作的模拟数字转换电路110)于第3个取样时间s3对输入信号sin进行取样,并进行模拟数字转换。其中,取样时间s1与s2之间的差为取样周期sp(其对应的取样频率为fs,即sp=1/fs)。依此类推,m个通道可根据多个交错时序进行运作。

57.校正电路120耦接至每一个模拟数字转换电路110,以接收多个量化输出q0~q

m-1

。校正电路120可依据量化输出q0~q

m-1

执行至少一误差运算来产生至少一校正信息,以校正多个模拟数字转换电路110中的偏移(offset)与增益(gain)误差,并产生校正后的多个量化输出cq20~cq2

m-1

。此外,校正电路120可根据校正后的量化输出cq20~cq2

m-1

分析多个模拟数字转换电路110之间存在的时脉偏斜(相当于时间差信息),以产生多个调整信号t0~t

m-1

。

58.如图1a所示,校正电路120包含偏移校正电路121、增益校正电路123以及偏斜调整电路125。偏移校正电路121电性耦接至每一个模拟数字转换电路110,以接收多个量化输出q0~q

m-1

。于部分实施例中,偏移校正电路121用以根据多个量化输出q0~q

m-1

执行一偏移误差运算(即前述的至少一误差运算)来产生一偏移校正信息(即前述的至少一校正信息),且利用偏移校正信息降低多个量化输出q0~q

m-1

的偏移误差来产生多个量化输出cq10~cq1

m-1

。

59.承上述,增益校正电路123电性耦接至偏移校正电路121,以接收多个量化输出cq10~cq1

m-1

。于部分实施例中,增益校正电路123用以根据多个量化输出cq10~cq1

m-1

执行一增益误差运算(即前述的至少一误差运算)来产生一增益校正信息(即前述的至少一校正信息),且利用增益校正信息降低多个量化输出cq10~cq1

m-1

的增益误差来产生校正后的多个量化输出cq20~cq2

m-1

。

60.承上述,偏斜调整电路125电性耦接至增益校正电路123,以接收校正后的多个量化输出cq20~cq2

m-1

。于部分实施例中,偏斜调整电路125用以分析校正后的量化输出cq20~cq2

m-1

来产生多个调整信号t0~t

m-1

。于部分实施例中,偏斜调整电路125将多个调整信号t0~t

m-1

分别输出至多个模拟数字转换电路110,多个调整信号t0~t

m-1

用以指示多个模拟数字转换电路110因时脉偏斜所需调整的时序。

61.详细而言,由于量化输出cq20对应第1个取样时间s1且量化输出cq21对应第2个取样时间s2,此两个对应时间之间的期间差为1个取样周期sp,故分析量化输出cq20以及量化输出cq21可得知时脉信号clk0与时脉信号clk1中于1个取样周期sp内的时间差信息。依此类推,通过此设置方式,偏斜调整电路125可分析出时脉信号clk0~clk

m-1

中每一对相邻的时脉信号于1个取样周期sp内的时间差信息。

62.上述分析时脉信号clk0~clk

m-1

中每一对相邻的时脉信号于1个取样周期sp内的时间差信息的设置方式仅用于示例,本揭示并不以此为限。于部分实施例中,偏斜调整电路125可分别分析出偶数项时脉信号clk0、clk2、

…

、clk

m-2

中于2个取样周期sp内的时间差信息以及奇数项时脉信号clk1、clk3、

…

、clk

m-1

中于2个取样周期sp内的时间差信息。

63.于部分实施例中,多个模拟数字转换电路110可根据多个调整信号t0~t

m-1

调整取样操作与/或模拟数字转换操作的执行时序,以等效校正时脉偏斜。于其他部分实施例中,多个时脉信号clk0~clk

m-1

的时序可直接根据多个调整信号t0~t

m-1

被调整,以等效校正时脉偏斜。举例而言,多个调整信号t0~t

m-1

被输入至用于产生多个时脉信号clk0~clk

m-1

的时脉产生器、相位内插器或是一数字延迟控制线,以调整多个时脉信号clk0~clk

m-1

的相位。上述根据调整信号t0~t

m-1

校正时脉偏斜的设置方式仅用于示例,本揭示并不以此为限。

64.又如图1a所示,控制电路130电性耦接至每一个模拟数字转换电路110以及校正电路120,以接收多个量化输出q0~q

m-1

。于部分实施例中,控制电路130用以分析多个量化输出q0~q

m-1

,以产生至少一控制信号(例如图1a所示的cso、csg、css)至校正电路120。关于此处的操作将于后述段落中参照图2详细说明。

65.请参阅图2,图2为根据本案部分实施例绘示的图1a中的控制电路130的电路示意图。于部分实施例中,控制电路130包含多个绝对值电路131、平均电路133、滤波电路135以及比较电路137。

66.多个绝对值电路131分别电性耦接至多个模拟数字转换电路110,以分别接收多个量化输出q0~q

m-1

。于部分实施例中,每一绝对值电路131依据多个量化输出q0~q

m-1

中的一对应量化输出执行一绝对值运算,以产生多个绝对值信号a0~a

m-1

中的一对应绝对值信号。以第1个绝对值电路131为例,第1个绝对值电路131接收量化输出q0,并执行绝对值运算来取得量化输出q0的绝对值,以产生绝对值信号a0。其余绝对值电路131的设置方式与操作可以此类推,故不再重复赘述。于部分实施例中,绝对值电路131可由处理电路或整流电路实现,各种实现绝对值电路131的电路皆为本揭示所涵盖的范围。

67.平均电路133电性耦接至多个绝对值电路131,以接收多个绝对值信号a0~a

m-1

。于部分实施例中,平均电路133用以根据多个绝对值信号a0~a

m-1

执行一平均运算来平均多个绝对值信号a0~a

m-1

,以产生平均信号avg。于部分实施例中,平均电路133可由数字处理电路实现,但本揭示并不以此为限。

68.如图2所示,于部分实施例中,平均电路133包含第一运算电路331以及第二运算电路333。第一运算电路331电性耦接至多个绝对值电路131,以接收多个绝对值信号a0~a

m-1

。于部分实施例中,第一运算电路331用以根据多个绝对值信号a0~a

m-1

执行一加总运算来加总多个绝对值信号a0~a

m-1

,以产生加总信号sum。于部分实施例中,第一运算电路331可由加法器或其他具有相同功能的处理电路实现。各种实现第一运算电路331的电路皆为本揭示所涵盖的范围。

69.承上述,第二运算电路333电性耦接至第一运算电路331,以接收加总信号sum。于部分实施例中,第二运算电路333用以对加总信号sum执行一除法运算,以产生平均信号avg。具体而言,第二运算电路333可将加总信号sum除以m(即为通道的数量)来产生平均信号avg。于部分实施例中,第二运算电路333可由除法器或其他具有相同功能的处理电路实现。各种实现第二运算电路333的电路皆为本揭示所涵盖的范围。

70.滤波电路135电性耦接至平均电路133,以接收平均信号avg。于部分实施例中,滤波电路135用以对平均信号avg进行滤波操作。

71.比较电路137电性耦接至滤波电路135,以接收滤波后的平均信号avg。于部分实施例中,比较电路137用以比较平均信号avg与至少一临界值(例如图2所示的th),以产生至少一控制信号(例如图2所示的cso、csg、css)至校正电路120。

72.由于多个量化输出q0~q

m-1

是通过多个模拟数字转换电路110转换输入信号sin的振幅而产生的,前述根据多个量化输出q0~q

m-1

产生的平均信号avg关联于输入信号sin的振幅。此外,用来与平均信号avg进行比较的临界值th也关联于输入信号sin的振幅。具体而言,平均信号avg可对应至当前输入信号sin的振幅,而临界值th可对应至一预先设定好的振幅大小(例如,20%的输入信号sin的最大振幅)。换言之,于图2所示的实施例中,控制电路130用于根据输入信号sin的振幅大小来产生至少一控制信号,但本揭示并不限于此。于其他实施例中,控制电路130也可用于根据输入信号sin的功率大小来产生至少一控制信号。

73.于部分实施例中,校正电路120根据至少一控制信号可选择性地执行至少一误差运算来产生至少一校正信息。此外,校正电路120根据至少一控制信号可选择性地分析多个模拟数字转换电路110之间存在的时脉偏斜(相当于多个时脉信号clk0~clk

m-1

的时间差信息)来产生多个调整信号t0~t

m-1

。

74.于部分实施例中,输入信号sin的振幅较大(或量化输出q0~q

m-1

中连续多者的数值变化量较大),使得平均信号avg大于或等于临界值th。据此,控制电路130可分别产生三个第一电压位准(例如,高电压位准)的控制信号cso、csg、css至校正电路120,以同时致能偏移校正电路121、增益校正电路123与偏斜调整电路125。换言之,偏移校正电路121根据高电压位准的控制信号cso执行偏移误差运算来产生偏移校正信息,增益校正电路123根据高电压位准的控制信号csg执行增益误差运算来产生增益校正信息,且偏斜调整电路125根据高电压位准的控制信号css分析多个时脉信号clk0~clk

m-1

的时间差信息来产生多个调整

信号t0~t

m-1

。

75.于部分实施例中,输入信号sin振幅较小(或量化输出q0~q

m-1

中连续多者的数值变化量较小),使得平均信号avg小于临界值th。据此,控制电路130可分别产生三个第二电压位准(例如,低电压位准)的控制信号cso、csg、css至校正电路120,以同时禁能偏移校正电路121、增益校正电路123与偏斜调整电路125。换言之,偏移校正电路121根据低电压位准的控制信号cso而不产生偏移校正信息,增益校正电路123根据低电压位准的控制信号csg而不产生增益校正信息,且偏斜调整电路125根据低电压位准的控制信号css不去分析多个时脉信号clk0~clk

m-1

的时间差信息。

76.在偏移校正电路121、增益校正电路123与偏斜调整电路125皆被禁能的情况下,校正电路120会利用先前所产生的校正信息来校正多个量化输出q0~q

m-1

,以产生的多个量化输出cq20~cq2

m-1

。此外,校正电路120会直接输出先前所产生的调整信号t0~t

m-1

来校正时脉偏斜。在一些实施例中,adc装置110包含一记忆体电路(未绘示),记忆体电路用于储存先前所产生的校正信息与先前所产生的调整信号t0~t

m-1

。

77.为便于说明,以下将对应于第n周期的多个时脉信号clk0~clk

m-1

的多个量化输出q0~q

m-1

、多个量化输出cq10~cq1

m-1

以及多个量化输出cq20~cq2

m-1

,分别称为第n周期的多个量化输出q0~q

m-1

、第n周期的多个量化输出cq10~cq1

m-1

以及第n周期的多个量化输出cq20~cq2

m-1

,其余信号的命名亦依此类推。于一实际应用的例子中,多个模拟数字转换电路110输出第n周期的多个量化输出q0~q

m-1

,其中,n为正整数。校正电路120通过偏移校正电路121与增益校正电路123校正第n周期的多个量化输出q0~q

m-1

,以产生第n周期的多个量化输出cq20~cq2

m-1

。此外,校正电路120通过偏斜调整电路125分析第n周期的多个量化输出cq20~cq2

m-1

,以产生第n周期的多个调整信号t0~t

m-1

。

78.承上述,控制电路130分析第n周期的多个量化输出q0~q

m-1

,以产生第n周期的多个控制信号cso、csg、css至校正电路120。据此,校正电路120可根据第n周期的多个控制信号cso、csg、css选择性地对第n+1周期的多个量化输出q0~q

m-1

执行至少一误差运算,且选择性地分析第n+1周期的多个时脉信号clk0~clk

m-1

的时间差信息。

79.举例来说,若第n周期的控制信号cso为高电压位准,则校正电路120中的偏移校正电路121根据第n+1周期的多个量化输出q0~q

m-1

执行偏移误差运算来产生偏移校正信息,且利用偏移校正信息降低第n+1周期的多个量化输出q0~q

m-1

的偏移误差来产生第n+1周期的多个量化输出cq10~cq1

m-1

。反之,若第n周期的控制信号cso为低电压位准,则偏移校正电路121不执行偏移误差运算,且利用先前产生的偏移校正信息(例如,根据第n周期的多个量化输出q0~q

m-1

产生的偏移校正信息)降低第n+1周期的多个量化输出q0~q

m-1

的偏移误差来产生第n+1周期的多个量化输出cq10~cq1

m-1

。

80.若第n周期的控制信号csg为高电压位准,则校正电路120中的增益校正电路123根据第n+1周期的多个量化输出cq10~cq1

m-1

执行增益误差运算来产生增益校正信息,且利用增益校正信息降低第n+1周期的多个量化输出cq10~cq1

m-1

的增益误差来产生第n+1周期的多个量化输出cq20~cq2

m-1

。反之,若第n周期的控制信号csg为低电压位准,则增益校正电路123不执行增益误差运算,且利用先前产生的增益校正信息(例如,根据第n周期的多个量化输出cq10~cq1

m-1

产生的增益校正信息)降低第n+1周期的多个量化输出cq10~cq1

m-1

的增益误差来产生第n+1周期的多个量化输出cq20~cq2

m-1

。

81.若第n周期的控制信号css为高电压位准,则校正电路120中的偏斜调整电路125分析第n+1周期的多个量化输出cq20~cq2

m-1

,以产生第n+1周期的多个调整信号t0~t

m-1

至多个模拟数字转换电路110。反之,若第n周期的控制信号css为低电压位准,则偏斜调整电路125不对第n+1周期的多个量化输出cq20~cq2

m-1

进行分析,且输出先前产生的多个调整信号t0~t

m-1

(例如,根据第n周期的多个量化输出cq20~cq2

m-1

产生的第n周期的多个调整信号t0~t

m-1

)至多个模拟数字转换电路110。

82.于上述实施例中,控制电路130中的比较电路137根据滤波后的平均信号avg与一个临界值th的比较结果来产生多个控制信号cso、csg、css,以同时禁/致能校正电路120中的偏移校正电路121、增益校正电路123与偏斜调整电路125。然而,本揭示并不限于此。于其他实施例中,控制电路130中的比较电路137可根据滤波后的平均信号avg与多个临界值的比较结果来产生不同电压位准的多个控制信号cso、csg、css,以分别禁/致能校正电路120中的偏移校正电路121、增益校正电路123与偏斜调整电路125。

83.例如,比较电路137将平均信号avg与第一临界值th1以及第二临界值th2进行比较,其中,第二临界值th2大于第一临界值th1。若平均信号avg小于第一临界值th1,则控制电路130输出一个高电压位准的控制信号cso以及二个低电压位准的控制信号csg、css,以致能偏移校正电路121,且禁能增益校正电路123与偏斜调整电路125。若平均信号avg大于第一临界值th1但小于第二临界值th2,则控制电路130输出二个高电压位准的控制信号cso、csg以及一个低电压位准的控制信号css,以致能偏移校正电路121与增益校正电路123,且禁能偏斜调整电路125。若平均信号avg大于第二临界值th2,则控制电路130输出三个高电压位准的控制信号cso、csg、css,以致能偏移校正电路121、增益校正电路123与偏斜调整电路125。换言之,输入信号sin的振幅愈小,被控制电路130禁能的电路数量可愈多。

84.请参阅图3,图3为根据本案部分实施例绘示的一种校正电路控制方法300的流程图。为易于理解,校正电路控制方法300将参照前述各附图进行描述。在部分实施例中,校正电路控制方法300可由图1a的adc装置100执行。于一实施例中,校正电路控制方法300首先执行步骤s310,通过校正电路120接收多个模拟数字转换电路110根据多个时脉信号clk0~clk

m-1

所产生的多个量化输出q0~q

m-1

。

85.校正电路控制方法300接着执行步骤s320,通过控制电路130分析多个量化输出q0~q

m-1

,以产生至少一控制信号(例如前述的多个控制信号cso、csg、css)至校正电路120。

86.校正电路控制方法300接着执行步骤s330,通过校正电路120根据至少一控制信号选择性地执行至少一误差运算来产生至少一校正信息,以及选择性地分析多个时脉信号clk0~clk

m-1

的时间差信息来产生多个调整信号t0~t

m-1

。

87.校正电路控制方法300接着执行步骤s340,通过校正电路120校正多个量化输出q0~q

m-1

来产生多个量化输出cq20~cq2

m-1

。前述各个步骤的说明与其实施方式可参考前述各实施例的描述,故于此不再重复赘述。

88.综上,本揭示的adc装置100以及校正电路控制方法300通过控制电路130分析多个模拟数字转换电路110所产生的多个量化输出q0~q

m-1

,以产生用于控制校正电路120的至少一控制信号。在输入信号sin微弱(例如,振幅过小或功率过小)的情况下,adc装置100通过至少一控制信号控制校正电路120根据先前产生的校正信息产生多个量化输出cq20~cq2

m-1

(或/及控制校正电路120输出先前产生的多个调整信号t0~t

m-1

),以避免校正电路

120所进行的校正因为输入信号微弱而受影响的问题。如此一来,也可解决多个模拟数字转换电路110之间的相位误差不正确地收敛的问题。

89.虽然本揭示内容已以实施方式揭露如上,然其并非用以限定本揭示内容,所属技术领域具有通常知识者在不脱离本揭示内容的精神和范围内,当可作各种更动与润饰,因此本揭示内容的保护范围当视所附的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1