基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构的制作方法

1.本发明涉及利用基板的多器件封装设计技术领域,具体涉及一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构。

背景技术:

2.至今许多涉及电子信息系统的设备及终端,需要本地时钟器件,晶体与时钟芯片结合,可提供稳定的数字脉冲信号和时间。根据应用,目前许多产生时间数据的场合,晶振与芯片是分离的,晶振安装在芯片旁边,但晶体与芯片通过pcb母版的链接,长久使用后,在晶振和芯片的管脚周围会生成许多灰尘,这些器件的pin角连线的灰尘会形成微小的寄生电容,进而长时间影响晶振的震荡周期,在与时钟芯片结合时,长时间就会产生时间漂移,影响时间精度。

3.日本epson公司针对上述缺陷,世界上率先开发出了rx8025t芯片。这款芯片最大的特点是采用厚sop14封装,把芯片和圆柱状晶振在引线框架的分别上下面焊接装配好后放入封装摸具中成型,形成了一体化厚sop14封装结构的时钟器件。这种晶振和芯片一体化封装的最大不足和缺点是封装过程复杂、传统的频率为26.768khz圆柱状晶振体积大、不易smt(表贴)焊接在封装框架上,需使用专用圆柱晶振引线打弯机、安装机和人工焊接,影响成品率以及成本高,封装成本。

技术实现要素:

4.为了克服epson公司rx8025t的封装缺点,降低成本、防止晶体外部链接带来的稳定性和时钟精确性的要求,提高可靠性并实现规模化量产需求,本发明提供了一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构。

5.本发明的目的是通过以下技术方案实现的。

6.具体的,根据本发明的一个方面,本发明公开了一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构,包括:

7.多层基板、多层基板信号线、多层基板接地线、底层电极、接地电极;其中,

8.所述多层基板的下表面具有凹嵌空间,所述凹嵌空间内平躺放置至少一颗柱体晶振和至少一颗晶振驱动芯片,空间内形成阶梯状结构,柱体晶振平躺在所述多层基板的凹嵌空间内层基板衬底上;所述芯片焊接在多层基板的凹嵌空间内层基板衬底上;

9.所述多层基板在所述凹嵌空间内具有阶梯状结构,柱体晶振的引线电极无弯曲与所述阶梯状结构上的基板电极平滑焊接,所述基板电极通过所述多层基板信号线连接所述底层电极;所述柱体晶振通过多层基板连线与所述晶振驱动芯片连接;

10.所述晶振驱动芯片通过芯片电极引线分别连接所述柱体晶振和连接电极,并通过所述连接电极连接所述多层基板接地线。

11.优选的,所述晶振驱动芯片为裸芯片。

12.优选的,所述凹嵌空间内进一步填充有封装树脂,以覆盖所述柱体晶振和裸芯片。

13.优选的,所述封装树脂不超过所述多层基板的下表面水平线。

14.优选的,所述晶振驱动芯片为封装芯片,所述芯片电极引线替换为芯片管脚,所述封装芯片通过芯片管脚焊接固定到所述多层基板连线和连接电极。

15.优选的,在所述多层基板上,进一步焊装无源器件,包括以下中的至少一种:表贴电容、电感、电阻、敏感材料器件。

16.优选的,所述多层基板信号线通过对应的层间连线孔连接底层电极,多层基板接地线通过对应的层间连线孔连接接地电极。

17.本发明的最大的特点在于:本发明利用廉价的电路基板,设计出了一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构,这种结构可以很容易通过凹嵌空间的阶梯基板,将柱体晶振和芯片都封装在多层基板的凹嵌内部。

18.该结构有以下优点:

19.1、避免了传统厚sop14封装结构的高昂模具加工费用和新结构的加工周期。基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构只需普通pcb加工工艺即可实现其基板框架。设计灵活、成本低和加工周期短(数天),而定制sip模具一般长达数月。

20.2、成本低。基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构的封装成本只有同等厚sop14结构封装的几分之一。

附图说明

21.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

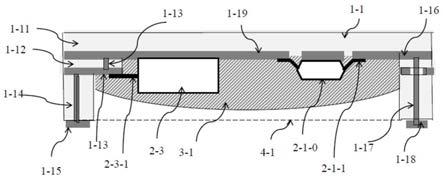

22.图1

‑

1一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构第一实施例示意图;

23.图1

‑

2一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构的上表面俯视示意图;

24.图1

‑

3一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构的上底面仰视示意图;

25.图2一种基于多层凹嵌式基板的柱体晶振与裸芯片单体化封装结构第二实施例示意图。

具体实施方式

26.下面将参照附图更详细地描述本公开的示例性实施方式。虽然附图中显示了本公开的示例性实施方式,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施方式所限制。相反,提供这些实施方式是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

27.本发明利用传统低成本的pcb多层基板,设计出一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构,凹嵌式基板内部空间内形成阶梯状结构,以便于柱体晶体电极线不需打弯便可以安装并焊接在阶梯层基板电极上。内外层设计出以pcb基板为灵活布线的连接方式,在凹嵌式空间来实现晶体和芯片的互联集成,最后点胶成型。

28.本发明在多层基板的背层一部分形成凹嵌空间,使多层基板作为封装母框体,将柱体晶振和芯片安装在内,以点胶形式封装在凹嵌空间内,该发明的最主要的特点是将两者封装成一体化集成结构。

29.如图1

‑

1所示,图1

‑

1是一种基于多层凹嵌式基板的柱体晶振与芯片单体化封装结构示意图,本发明的意图是在多层基板1

‑

1底面加工出一个凹嵌空间4

‑

2。把事先封装成型的晶振驱动芯片2

‑1‑

0焊接在多层基板的内层基板衬底上。根据设计布线要求,通过芯片电极引线2

‑1‑

1、电极1

‑

16和层间连线孔1

‑

17(孔内具有多层基板接地线),接入到基板电极线1

‑

18(也是接地电极)。柱体晶振2

‑

3平躺在基板底部,但柱体晶振中心的电极引线2

‑3‑

1搭焊在凹嵌空间4

‑

2的阶梯基板层1

‑

12的电极1

‑

13上。这里注意,电极引线2

‑3‑

1的几何位置高度尽量与阶梯基板层1

‑

12的电极1

‑

13高度在一个水平面上。晶振驱动芯片2

‑1‑

0与晶振2

‑

3通过链接多层基板连线1

‑

19相连接。当然,电极1

‑

16、多层基板连线1

‑

19、层间连线孔1

‑

17和接地电极1

‑

18等可以根据芯片器件的系统要求,在基板底面自由设计。1

‑

11、1

‑

12为绝缘层,1

‑

14为层间连线孔(孔内具有多层基板信号线)连接底层电极1

‑

15和基板电极1

‑

13。

30.完成芯片和器件的装配及贴装后,在基板的凹嵌空间内填充封装树脂3

‑

1,并加热使树脂固化。

31.此外,要强调的是,该多层基板的凹嵌空间内的封装树脂3

‑

1不得超过凹嵌空间界面4

‑

1。

32.结构图如图1

‑

2和1

‑

3所示,分别表示了一种基于多层凹嵌式基板的柱体晶振与驱动芯片单体化封装结构的实际在设备中的上面图和底面图。上表面是平整基板,基板的底层电极1

‑

15、接地电极1

‑

18等与其他母板焊接,当然,底层电极1

‑

15和接地电极1

‑

18等多个基板外围电极,可以根据芯片器件的信号线、接地线和电源线的系统要求,在基板底面自由设计。

33.在本发明的系统实际设计中,芯片也采购封装好的芯片,如一种基于多层凹嵌式基板的含有已封装芯片的多器件封装单体化结构示意图,即图2所示,器件可以是封装芯片2

‑2‑

0,芯片管脚2

‑2‑

1焊接固定到基板内部凹嵌部金属连接线1

‑

16(也是连接电极)和多层基板连线1

‑

19上。晶振驱动芯片2

‑2‑

0与晶振2

‑

3通过链接多层基板连线1

‑

19相连接。柱体晶振2

‑

3安装时需平躺,其电极2

‑3‑

1与基板电极1

‑

13焊接。在晶振和驱动芯片装配完成之后填装树脂3

‑

1加热固化。

34.本实施例利用廉价的电路基板,设计出了这种结构驱动芯片和柱体晶振装配在多层基板的凹嵌内部,可以在利用基板进行芯片和器件间的辅助电路布设,不用每次新的结构封装的引线框架和封装模具的制作,多基板衬底及引线设计灵活。封装凹嵌式基板内的芯片2

‑1‑

0,可以是裸芯片、也可以是树脂封装好的芯片。可降低费用和制作周期,这是本发明的基本特点和优点。

35.本发明可以低成本地进行灵活的少量试料测试(pilot)。并可以进行快速的系统级的功能和性能的初期、中试评估。各批次芯片的性能离散的特性进行调节,通过安装在凹嵌内部的芯片外围电路器件选择,灵活进行参数配置调节来实现其优化功能。

36.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范

围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1