一种基于FPGA的高速码率兼容DVB-S2的LDPC编码器及编码方法与流程

一种基于fpga的高速码率兼容dvb

‑

s2的ldpc编码器及编码方法

技术领域

1.本发明涉及一种基于fpga的高速码率兼容dvb

‑

s2的ldpc编码器及编码方法。

背景技术:

2.随着空间技术和通信技术的发展,人们对卫星数据传输速率和可靠性的要求不断提高,信道编码是提高数据传输可靠性的关键技术。ldpc码是目前纠错编码领域研究最多且最有前景的编码技术,移动通信(如5g)、光纤、磁介质设备广泛采用ldpc编码技术。各种卫星通信系统均采用了ldpc码,如ccsds标准和欧洲第二代数字卫星电视广播dvb

‑

s2标准,dvb

‑

s2标准提供了一种强大的前向纠错编码方案,该系统的纠错编码采用ldpc与bch级联码,现阶段还对dvb

‑

s2标准的ldpc码进行扩展,形成了dvb

‑

s2x标准,进一步奠定了ldpc码的重要性。

3.现有的dvb

‑

s2文献中,对ldpc译码器的架构和实现关注较多,因为译码器是接收机数字基带部分最复杂的模块。此外,研究人员还致力于从理论上改进波形设计以获得更好的频谱和能量效率。而关于编码器的架构和实现技术的研究相对比较欠缺。值得注意的是,现阶段编码器广泛应用于卫星数据传输系统的发射机和接收机中,是各种卫星载荷中不可缺少的关键技术。因此,对于卫星载荷的fpga/asic资源受限系统,研究资源利用率高且吞吐量高的dvb

‑

s2 ldpc编码器的设计与实现技术显得尤为重要。

4.针对dvb

‑

s2/dvb

‑

s2x的ldpc编码器asic或fpga的实现,中文文献《dvb

‑

s2标准下前向纠错码的编译码研究及fpga实现》,设计的仅支持一个编码速率的编码器,可实现的最大时钟频率为125mhz,对应125mbps的吞吐量。中文文献《基于fpga的dvb

‑

s2 ldpc编码器的设计与实现》,采用每次并行计算360位校验比特,设计实现了一款基于fpga的dvb

‑

s2 ldpc编码器,综合时钟频率为65.5mhz,吞吐量可达2.6gbps。中文专利《一种多码率兼容的高速ldpc编码器的硬件实现》仅给出一种多码率兼容的可适用于dvb

‑

s2 ldpc码的实时编码器硬件实现方法,没有给出设计实例和相应的硬件资源。中文专利《一种基于dvb

‑

s2标准多码率兼容的ldpc编码器》将控制单元和运算单元分离设计了一种基于dvb

‑

s2标准多码率兼容的ldpc编码器,没有关注吞吐量的优化设计问题。英文文献《high

‑

speed ldpc encoder architecture for digital video broadcasting systems》,当时钟频率为100mhz时,其编码吞吐量高达10gbps,但文中没有给出编码器占用的相关硬件资源数量信息。诺斯罗普格鲁曼宇航公司的工程师,采用gpu设计的dvb

‑

s2 ldpc编码器,吞吐量可达几个gbps,但没有可以与fpga进行对比的资源。文献《development of the ldpc coder

‑

decoder of the dvb

‑

s2 standard on fpga》中的编码器结构可支持多种码率,但每种码率的编码器吞吐量均较低,在百兆以下。文献《fpga design and implementation of dvb

‑

s2/s2x ldpc encoder》的编码器实现方法可支持dvb

‑

s2/dvb

‑

s2x所有的码率和帧类型,但没有考虑吞吐量的动态可调和高吞吐量的优化设计问题。

技术实现要素:

5.本发明的技术解决问题是:克服现有技术的不足,提供了一种基于fpga的高速码率兼容dvb

‑

s2的ldpc编码器及编码方法。

6.本发明的技术解决方案是:

7.一种基于fpga的高速码率兼容dvb

‑

s2的ldpc编码器,包括:控制模块、首列校验位地址读取模块、其他列校验位地址计算模块、校验位计算模块及编码码字产生模块;

8.控制模块通过输入的门控信号synin和码率rate产生校验位的选择参数sel、计数器信号cnt和地址信号addr_h,并将地址信号addr_h提供给首列校验位地址读取模块,将计数器信号cnt提供给其他列校验位地址计算模块,将校验位的选择参数sel提供给校验位计算模块及编码码字产生模块;

9.控制模块还将输入的门控信号synin和信息序列msg经过延迟后得到的输出synin_dly和msg_dly送入编码码字产生模块;

10.首列校验位地址读取模块get_ramh产生各种码率情况下的首列校验地址并将输出至其他列校验位地址计算模块,其中,c

max

为兼容n

rate

种码率的dvb

‑

s2的ldpc编码器的首列非零元素的最大个数且有

11.其他列校验位地址计算模块通过输入的首列校验地址计算hc

max

个其他列校验位地址并输出给校验位计算模块;

12.校验位计算模块用来计算dvb

‑

s2 ldpc码的校验位,并输出给编码码字产生模块;

13.编码码字产生模块get_code通过输入的校验位的选择参数sel信号来选择ldpc编码器的最终输出。

14.进一步的,根据输入码率rate产生校验位的选择参数sel,对于一帧dvb

‑

s2ldpc(n,k)码,码字的长度为n比特,信息位的长度为k=rate

×

n;rate是码率;

15.当并行h路进行编码时,校验位的选择参数sel为高电平时对应的时钟周期数为k/h个,对于一帧的其他时间段,校验位的选择参数sel为低电平;

16.当校验位的选择参数sel均为低电平时,计数器信号cnt和地址信号addr_h均为低电平零信号;

17.当输入门控信号synin和校验位的选择参数sel均为高电平时,计数器信号cnt开始从0计数,计数周期为l/h个时钟周期,即当计数值为l/h

‑

1时,计数器信号cnt再次回到0,l是dvb

‑

s2 ldpc码的列分块大小。

18.当校验位的选择参数sel为高电平,且计数器信号cnt从最大值变为0值时,地址信号addr_h才计数,即地址信号addr_h每隔l/h个时钟周期自加一次。

19.进一步的,首列校验位地址读取模块包括存储器romh用来存储不同码率的首列校验位地址值,该存储器romh仅具体读功能,所有码率情况下的首列校验位地址均需存储到存储器romh中,共存储个地址,每个地址占用log2(n

‑

k)比特,k

rate

表示n

rate

种码率的信息位最大长度。

20.进一步的,存储器romh的位宽为深度为

21.进一步的,其他列校验位地址计算模块通过输入的首列校验地址通

过如下公式计算hc

max

个其他列校验位地址q

rate

是dvb

‑

s2 ldpc码率为rate的校验位分块数;

[0022][0023]

进一步的,不同的码率rate对应的q值,当码率兼容dvb

‑

s2 ldpc编码器兼容的ldpc码个数为n

rate

个时,表示所有码率对应q所需要的比特数y如下式所示:

[0024][0025]

对于任意一个ldpc码的码率rate对应的q值表示为二进制序列b=[b0,b1,

…

,b

y

],cnt∈[0,l/h

‑

1]为对l/h取模后的运算,cnt

×

[b0,b1,

…

,b

y

]表示(m mod l)

×

q的计算结果,二进制的乘法运算用或or表示,经过加法器后得到a=r+(m mod l)

×

q,对a进行(n

‑

k)取模运算,即可得到其他列校验位地址

[0026]

进一步的,校验位计算模块包括一个n

‑

k比特的寄存器reg_p,用于存储实时更新的校验位;通过输入的hc

max

个地址从寄存器reg_p中取出相应的hc

max

个校验位信息;

[0027]

输入的校验位的选择参数sel作为控制信号,当该控制信号为低电平时,对并行h路输入的信息序列进行编码,按照公式一个时钟周期计算hq

max

个校验位;采用寄存器reg_p将上一个时钟周期产生的校验块存储后与本周期的校验块异或,即实现待到(n

‑

k)/h个时钟周期,即所有的信息位输入后,计算出所有的校验位p0,p1,

…

,p

n

‑

k

‑1;

[0028]

当控制信号sel为高电平时,每个时钟周期需要从寄存器reg_p中移位h个校验位信息输出给编码码字产生模块。

[0029]

进一步的,当校验位的选择参数sel为低电平时,编码码字产生模块并行输出h路的校验位p,否则输出信息系列msg的延迟信号msg_dly,同时还要输出标识帧开始的synout信号,该信号为输入门控信号synin的延迟信号synin_dly。

[0030]

进一步的,本发明还提出一种编码方法,步骤如下:

[0031]

第一步,控制模块根据输入的门控信号synin和码率rate分别产生:地址信号addr_h输出给首列校验位地址读取模块、计数器信号cnt输出给其他列校验位地址计算模块、校验位的选择参数sel输出给校验位计算模块和编码码字产生模块;控制模块还将输入的门控信号synin和信息序列msg经过延迟后得到的输出synin_dly和msg_dly送入编码码字产生模块;

[0032]

第二步,将信息序列msg并行h路输入,表示为msg=(i1,i2,

…

,i

h

)

t

,首列校验位地址读取模块根据控制模块产生的地址信号addr_h从存储器romh中读出首列校验位地址,通过首列校验地址读取模块同时读出个首列校验位地址,c

max

表示n

rate

种码率的ldpc码的最大c值;同时读取c

max

个首列校验地址以实现n

rate

种码率编码率的dvb

‑

s2ldpc编码器,如果列重d

v

<c

max

,则将首列校验地址置零即可;

[0033]

第三步,其他列校验位地址计算模块通过首列校验位地址读取模块输入的首列校验地址计算hc

max

个其他列校验位地址,计算公式如下

[0034][0035]

第四步,校验位计算模块在输入信息位的时间段,即控制模块输入的校验位的选择参数sel为低电平时,对并行h路输入的信息序列进行编码,按照公式一个时钟周期计算hc

max

个校验位;采用寄存器reg_p将上一个时钟周期产生的校验块存储后与本周期的校验块异或,即可实现待到(n

‑

k)/h个时钟周期后获得所有的校验位p0,p1,

…

,p

n

‑

k

‑1;

[0036]

第五步,编码码字产生模块通过输入的校验位的选择参数sel信号来选择ldpc编码器的最终输出,当sel信号为高电平时输出控制模块输入的信息序列延迟信号msg_dly,否则将校验位计算模块的输出校验位p取出作为ldpc编码器的最终输出;码率兼容dvb

‑

s2 ldpc编码器还将控制模块输入的门控延迟信号synin_dly作为最终的门控信号synout输出。

[0037]

本发明与现有技术相比的有益效果是:

[0038]

本发明提出了一种基于fpga的高速码率兼容dvb

‑

s2 ldpc编码器的设计方法,该方法可以实现对dvb

‑

s2标准所有ldpc码的编码,且可对各种码率编码器的资源进行共享。另外,可以通过改变编码器架构的并行度,来动态调整本发明dvb

‑

s2 ldpc编码器的吞吐量,从而满足不同应用场景的需求。使用这个架构,在xilinx xc4vsx55

‑

10ff1148 fpga上实现了一个五种码率兼容的dvb

‑

s2 ldpc编码器,该编码器时延小,fpga资源利用率高,编码吞吐量高,码率兼容ldpc编码器的总吞吐量高达4gbps。

附图说明

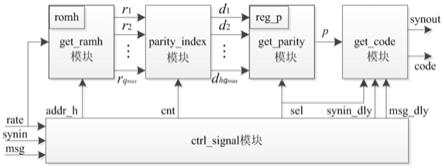

[0039]

图1为码率兼容dvb

‑

s2 ldpc编码器总体框图;

[0040]

图2是dvb

‑

s2 ldpc编码器控制模块输出时序示意图;

[0041]

图3是码率兼容dvb

‑

s2 ldpc编码器首列校验位地址的存储示意图;

[0042]

图4是其他列校验位地址计算的电路框图;

[0043]

图5是校验位计算模块电路框图。

具体实施方式

[0044]

下面结合附图对本发明的具体实施方式进行进一步的详细描述。

[0045]

本发明提出了一种基于fpga的高速码率兼容dvb

‑

s2 ldpc编码器的设计方法,该方法可以实现对dvb

‑

s2标准所有ldpc码的编码,且可对各种码率编码器的资源进行共享。另外,可以通过改变编码器架构的并行度,来动态调整本发明dvb

‑

s2 ldpc编码器的吞吐量,从而满足不同应用场景的需求。使用这个架构,在xilinx xc4vsx55

‑

10ff1148 fpga上实现了一个五种码率兼容的dvb

‑

s2 ldpc编码器,该编码器时延小,fpga资源利用率高,编码吞吐量高,码率兼容ldpc编码器的总吞吐量高达4gbps。

[0046]

一、码率兼容dvb

‑

s2 ldpc编码算法:

[0047]

dvb

‑

s2标准的ldpc(n,k)码是一个系统码,编码器将含有k比特的信息分组i=(i0,i1,

…

,i

k

‑1)编码成一个含有n比特的码字c=(i0,i1,

…

,i

k

‑1,p0,p1,

…

,p

n

‑

k

‑1)。码字的传输从i0开始,以p

n

‑

k

‑1结束。编码器需要根据k个信息比特的分组i=(i0,i1,

…

,i

k

‑1)计算n

‑

k

个校验比特p0,p1,

…

,p

n

‑

k

‑1,其步骤如下:

[0048]

·

初始化:p0=p1=

…

=p

n

‑

k

‑1=0

[0049]

·

对第一个信息比特i0进行累加,对应的校验位地址由查找表的第一行确定

[0050]

·

对接下来的l

‑

1个信息位i

m

,m=1,2,

…

,l

‑

1按如下公式进行累加

[0051][0052]

其中,

[0053]

j=(r+(m mod l)

×

q)mod(n

‑

k)

ꢀꢀ

(2)

[0054]

这里r对应于第一个信息位i0的校验位累加地址,q为常数,其取值依不同的码而不同,q的具体取值见dvb

‑

s2标准。

[0055]

·

对于第l+1个信息位i

l

,进行校验位累加的地址由地址查找表中的第二行给出,其后续l

‑

1个信息位i

m

,m=l,

…

,2l

‑

1的校验位地址同样地通过公式(2)确定。

[0056]

·

采用相同的方法,对接下来的每一组l个信息位,使用地址查找表中新的一行来获得用于累加的校验位地址,这样一直进行下去,直到计算完最后一个信息位。

[0057]

·

从i=1开始,顺序执行下列操作

[0058][0059]

·

经上述步骤后,即可得到所需校验比特p0,p1,

…

,p

n

‑

k

‑1。

[0060]

对于不同码率的dvb

‑

s2 ldpc码,仅需改变l、n、k和q值,即可实现码率兼容的dvb

‑

s2 ldpc编码。

[0061]

二、码率兼容dvb

‑

s2 ldpc编码器fpga硬件实现架构

[0062]

以上面介绍的码率兼容dvb

‑

s2 ldpc编码算法为基础,该编码方法只需要存储每块首列校验地址即可,利用这个特点可以节省大量的存储空间。而位于每块的其他列的校验地址由公式(2)计算得到,获得校验地址后即可将以其对应的信息位累加上去。利用对应这些块的信息位更新完校验位后,再利用公式(3)依次求出最终的校验位。本发明设计了如图1所示的编码器架构,该编码器主要由五个模块构成,包括控制模块ctrl_signal、首列校验位地址读取模块get_ramh、其他列校验位地址计算模块parity_index、校验位计算模块get_parity及编码码字产生模块get_code。

[0063]

三、码率兼容dvb

‑

s2 ldpc编码器各模块的实现

[0064]

1、控制模块ctrl_signal

[0065]

本发明设计的控制模块ctrl_signal通过输入的门控信号synin和码率rate产生校验位的选择参数sel、计数器信号cnt和地址信号addr_h。该控制模块需要产生的信号如图2所示。

[0066]

根据输入码率rate产生校验位的选择参数sel,由第1节编码算法部分可知,对于一帧dvb

‑

s2 ldpc(n,k)码,码字的长度为n比特,信息位的长度为k=rate

×

n。当并行h路进行编码时,sel为高电平时对应的时钟周期数为k/h个,对于一帧的其他时间段,sel为低电平。

[0067]

当校验位的选择参数sel均为低电平时,计数器信号cnt和地址信号addr_h均为低电平零信号。

[0068]

当输入门控信号synin和校验位的选择参数sel均为高电平时,计数器信号cnt开

始从0计数,计数周期为l/h个时钟周期。即当计数值为l/h

‑

1时,cnt再次回到0。

[0069]

当校验位的选择参数sel为高电平,且计数器信号cnt从最大值变为0值时,地址信号addr_h才计数,即地址信号addr_h每隔l/h个时钟周期自加一次。

[0070]

为了保持时序的同步,控制模块ctrl_signal还将输入的门控信号synin和信息序列msg经过延迟后得到的输出synin_dly和msg_dly送入编码码字产生模块get_code。

[0071]

ldpc码的不同码率对应不同的控制模块参数值,从图2的ldpc编码器时序图可以看到,dvb

‑

s2 ldpc码是系统码,所以该编码器架构在接收完所有的信息位后即可将全部校验位计算出来,编码码字产生模块只需要将信息位延迟输出,等所有信息位输出完后将校验位依次输出即可,所以这种架构的编码器是一种实时编码器,不需要对输入数据进行缓存。

[0072]

2、首列校验位地址读取模块get_ramh

[0073]

首列校验位地址读取模块get_ramh用来产生各种码率情况下的首列校验地址兼容n

rate

种码率的dvb

‑

s2的ldpc编码器的该模块包含一个存储器romh用来存储不同码率的首列校验位地址值,该存储器只需要读功能。为了实现码率兼容ldpc编码器,所有码率情况下的首列校验位地址均需要存储到存储器romh中,共需要存储个地址,每个地址占用log2(n

‑

k)比特,k

rate

表示n

rate

种码率的信息位最大长度。

[0074]

为了充分利用fpga的bram资源,本发明设计的码率兼容dvb

‑

s2 ldpc编码器的这部分资源采用了压缩存储的方法,如图3所示。此时存储器romh的位宽为深度为

[0075]

输入地址信号addr_h每隔l/h个时钟周期自加一次,即对于每个校验矩阵的列块,该值保证不变。显然每个校验矩阵列块的其他非零元素可由首列校验位地址来确定,该模块的输出送至其他列校验位地址计算模块parity_index。

[0076]

3、其他列校验位地址计算模块parity_index

[0077]

其他列校验位地址计算模块parity_index通过输入的首列校验地址按照计算公式(4)来计算hc

max

个其他列校验位地址其实现电路如图4所示。

[0078]

不同的码率rate对应的q值,当码率兼容dvb

‑

s2 ldpc编码器兼容的ldpc码个数为n

rate

个时,表示所有码率对应q所需要的比特数y如公式(5)所示:

[0079][0080]

对于任意一个ldpc码的码率rate对应的q值可表示为二进制序列b=[b0,b1,

…

,b

y

],由于cnt∈[0,l/h

‑

1],为对l/h取模后的运算。所以cnt

×

[b0,b1,

…

,b

y

]表示(m mod l)

×

q的计算结果,二进制的乘法运算用或or表示。经过加法器后得到a=r+(m mod l)

×

q。按照公式(2)还需要对a进行(n

‑

k)取模运算,本发明采用比较器、减法器和选择器的实现方法,即可得到其他列校验位地址

[0081]

4、校验位计算模块get_parity

[0082]

校验位计算模块get_parity用来计算dvb

‑

s2 ldpc码的校验位,其实现电路如图5所示。该模块包含一个n

‑

k比特的寄存器reg_p,用来存储实时更新的校验位。通过输入的

hc

max

个地址从寄存器reg_p中取出相应的hc

max

个校验位信息。当控制信号sel为低电平时,对并行h路输入的信息序列进行编码,按照公式一个时钟周期可计算hq

max

个校验位。采用寄存器reg_p将上一个时钟周期产生的校验块存储后与本周期的校验块异或,即可实现待到(n

‑

k)/h个时钟周期,即所有的信息位输入后,可以计算出所有的校验位p0,p1,

…

,p

n

‑

k

‑1。当控制信号sel为高电平时,每个时钟周期需要从寄存器reg_p中移位h个校验位信息输出给编码码字产生模块get_code。

[0083]

5、编码码字产生模块get_code

[0084]

编码码字产生模块get_code,当校验位的选择参数sel为低电平时,并行输出h路的校验位p,否则输出信息系列msg的延迟信号msg_dly。同时还要输出标识帧开始的synout信号,该信号为输入门控信号synin的延迟信号synin_dly。

[0085]

本发明码率兼容dvb

‑

s2 ldpc编码器的编码步骤如下:

[0086]

第一步,控制模块ctrl_signal根据输入的门控信号synin和码率rate分别产生:地址信号addr_h输出给首列校验位地址读取模块get_ramh,计数器信号cnt输出给其他列校验位地址计算模块parity_index,校验位的选择参数sel输出给校验位计算模块get_parity和编码码字产生模块get_code。为了保持时序的同步,控制模块ctrl_signal还将输入的门控信号synin和信息序列msg经过延迟后得到的输出synin_dly和msg_dly送入编码码字产生模块get_code。

[0087]

第二步,将信息序列msg并行h路输入,表示为msg=(i1,i2,

…

,i

h

)

t

的情况,首列校验位地址读取模块get_ramh根据控制模块ctrl_signal产生的地址信号addr_h从romh中读出首列校验位地址,通过首列校验地址读取模块get_ramh可同时读出个首列校验位地址,c

max

表示n

rate

种码率的ldpc码的最大c值。为了实现n

rate

种码率编码率的dvb

‑

s2 ldpc编码器,需要同时读取c

max

个首列校验地址如果列重d

v

<c

max

,只需将首列校验地址置零即可。

[0088]

第三步,其他列校验位地址计算模块parity_index通过首列校验位地址读取模块get_ramh输入的首列校验地址来计算hc

max

个其他列校验位地址,计算公式如下

[0089][0090]

第四步,校验位计算模块get_parity在输入信息位的时间段,即控制模块ctrl_signal输入的校验位的选择参数sel为低电平时,对并行h路输入的信息序列进行编码,按照公式一个时钟周期可计算hc

max

个校验位。采用寄存器reg_p将上一个时钟周期产生的校验块存储后与本周期的校验块异或,即可实现待到(n

‑

k)/h个时钟周期后可以获得所有的校验位p0,p1,

…

,p

n

‑

k

‑1。

[0091]

第五步,编码码字产生模块get_code通过输入的校验位的选择参数sel信号来选择ldpc编码器的最终输出,当sel信号为高电平时输出控制模块ctrl_signal输入的信息序列延迟信号msg_dly,否则将get_parity模块的输出校验位p取出作为ldpc编码器的最终输出。码率兼容dvb

‑

s2 ldpc编码器还将ctrl_signal输入的门控延迟信号synin_dly作为最终的门控信号synout输出。

[0092]

码率兼容dvb

‑

s2 ldpc编码器设计实例:

[0093]

下面给出了采用本发明的方法实现的一个基于fpga的高速码率兼容dvb

‑

s2 ldpc编码器的实例。本发明从dvb

‑

s2标准中选取了五个码长为16200的ldpc码进行码率兼容编码器的fpga实现,这五个码的码率分别为2/5、3/5、2/3、7/9和8/9,q的取值如表1所示。

[0094]

表1.短帧ldpc码在不同码率时的对应的q值

[0095]

码率2/53/52/37/98/9q值271815105c值12121334

[0096]

这五个码的(n,k)参数分别为(16200,6480),(16200,9720),(16200,10800),(16200,12600)和(16200,14400)。所以它们对应的校验位的位数分别为9720,6480,5400,3600和1800。分块大小l=360。

[0097]

此时存储器romh的位宽为深度为占用6块18k的bram资源。

[0098]

对于本发明提出的这种编码器架构,在xilinx xc4vsx55

‑

10ff1148 fpga上实现了一个兼容五种码率的dvb

‑

s2 ldpc编码器。

[0099]

为了实现高吞吐量dvb

‑

s2 ldpc编码器,采用h=20路并行输入情况,综合和布局布线采用xilinx ise 14.7,加上5ns的时钟约束,可满足要求,对应200mhz的时钟主频。此时编码器的吞吐量为200

×

20=4gbps。五种码率兼容dvb

‑

s2 ldpc编码器的fpga实现结果及资源占用如表2所示。

[0100]

表2.五种码率兼容dvb

‑

s2 ldpc编码器的fpga资源占用

[0101]

资源类型flip flops4input lutsslices18kbits bram编码器资源17058(34%)15582(32%)13454(54%)6(1%)

[0102]

本发明设计的dvb

‑

s2 ldpc编码器架构的并行度为h。通过增大并行度h即可提高dvb

‑

s2 ldpc编码器的吞吐量,改变并行度为h即可动态调节编码器的吞吐量,从而满足不同应用场景的需求。另外,该架构可兼容不同的码率,在硬件资源共享的情况下实现速率和码率动态可调性。

[0103]

本发明针对现有文献在吞吐量的灵活性和对不同码率dvb

‑

s2的兼容性架构方面的研究不足,重点研究吞吐量可调节且码率兼容dvb

‑

s2 ldpc编码器的设计方法,可有效实现吞吐量与编码器资源的有效折中,提出的编码器架构灵活性好,仅通过提高并行路数,即可提高编码器的吞吐量。提出的ldpc码时延小,fpga资源利用率高,吞吐量高,码率兼容ldpc编码器总吞吐量高达4gbps。

[0104]

本发明说明书中未作详细描述的内容属于本领域的公知技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1