一种交错信号产生电路和集成芯片的制作方法

1.本发明涉及电路技术领域,特别涉及一种交错信号产生电路和集成芯片。

背景技术:

2.目前芯片设计领域日益注重高集成度、多功能性、低功耗、小型化等技术指标。随着芯片产业的各项技术不断革新,以及系统应用设计的简单化和设计功能多样化的要求出现,使芯片电路设计变得更加复杂,因此,对于信号产生电路灵活性、功能多样性的要求日益提高。

3.芯片电路设计领域常用到交错信号,交错信号可以分为等间隔等脉宽交错信号、非等间隔等脉宽交错信号、等间隔非等脉宽交错信号和非等间隔非等脉宽交错信号。现有中产生交错信号的电路只能产生一种类型的交错信号,不够灵活。

技术实现要素:

4.本发明提供一种交错信号产生电路和集成芯片,用以解决现有技术中存在的交错信号产生电路不够灵活的问题。

5.第一方面,本发明实施例提供一种交错信号产生电路,包括:

6.脉冲产生电路,用于根据延时信号和初始信号,生成第一周期脉冲信号和第二周期脉冲信号;

7.计数电路,用于对所述第一周期脉冲信号和所述第二周期脉冲信号进行计数,生成上升沿触发信号和下降沿触发信号;

8.信号产生电路,用于根据输入的上升沿触发信号和输入的下降沿触发信号,生成交错脉冲信号。

9.在一种可能的实现方式中,所述信号产生电路包括多个信号产生子电路;

10.每个信号产生子电路,用于根据输入的上升沿触发信号和输入的下降沿触发信号,生成交错脉冲子信号;

11.其中,多个所述交错脉冲子信号组成所述交错脉冲信号。

12.在一种可能的实现方式中,所述信号产生子电路包括sr锁存器、第一非门和第二非门:

13.所述sr锁存器的第一输入端用于输入上升沿触发信号,所述sr锁存器的第二输入端用于输入下降沿触发信号,所述sr锁存器的第三输入端用于输入上升沿交错使能信号,所述sr锁存器的输出端与所述第一非门的输入端连接;

14.所述第一非门的输出端与所述第二非门的输入端连接;

15.所述第二非门的输出端用于输出所述交错脉冲子信号。

16.在一种可能的实现方式中,若输入到多个所述信号产生子电路中相邻的信号产生子电路的上升沿计数信号的时间间隔相同,则所述交错脉冲信号为等间隔的交错脉冲信号;

17.若输入到多个所述信号产生子电路中相邻的信号产生子电路的上升沿计数信号的时间间隔不同,则所述交错脉冲信号为非等间隔的交错脉冲信号;

18.若输入到每个所述信号产生子电路中的上升沿计数信号和与其对应的下降沿计数信号的时间间隔相同,则所述交错脉冲信号为等脉宽的交错脉冲信号;

19.若输入到每个所述信号产生子电路中的上升沿计数信号和与其对应的下降沿计数信号的时间间隔不同,则所述交错脉冲信号为非等脉宽的交错脉冲信号。

20.在一种可能的实现方式中,所述脉冲产生电路包括第一周期脉冲信号产生电路和第二周期脉冲信号产生电路;

21.所述第一周期脉冲信号产生电路,用于根据所述延时信号、所述初始信号、上升沿交错使能信号、上升沿交错调整延迟信号和上升沿交错调整延迟反信号,生成所述第一周期脉冲信号;

22.所述下降沿时钟信号产生电路,用于根据所述延时信号、所述初始信号、下降沿交错使能信号、所述上升沿交错调整延迟信号和所述上升沿交错调整延迟反信号,生成所述第二周期脉冲信号。

23.在一种可能的实现方式中,所述上升沿时钟信号产生电路包括:第一振荡器和第三非门;

24.所述第一振荡器的第一输入端用于输入所述初始信号,所述第一振荡器的第二输入端用于输入所述上升沿交错使能信号,所述第一振荡器的第三输入端用于输入所述上升沿交错调整延迟信号,所述第一振荡器的第四输入端用于输入所述上升沿交错调整延迟反信号,所述第一振荡器的第五输入端用于输入所述延时信号,所述第一振荡器的输出端与所述第三非门的输入端连接,用于输出上升沿时钟信号;所述第三非门的输出端用于输出所述第一周期脉冲信号;

25.所述下降沿时钟信号产生电路包括第二振荡器、第四非门和第一与非门;

26.所述第四非门的输入端用于输入所述初始信号,所述第四非门的输出端与所述第二振荡器的第一输入端连接;

27.所述第二振荡器的第二输入端用于输入所述下降沿交错使能信号,所述第二振荡器的第三输入端用于输入所述上升沿交错调整延迟信号,所述第二振荡器的第四输入端用于输入所述上升沿交错调整延迟反信号,所述第二振荡器的第五输入端用于输入所述延时信号,所述第二振荡器的输出端与所述第一与非门的第一输入端连接,用于输出所述下降沿时钟信号;

28.所述第一与非门的第二输入端用于输入下降沿使能信号,所述第一与非门的输出端用于输出所述第二周期脉冲信号。

29.在一种可能的实现方式中,还包括第五非门和触发器;

30.所述第五非门的输入端与所述触发器的clk端连接,用于输入actenplan,所述第五非门的输出端与所述触发器的clkn端连接;

31.所述触发器的d端接地,所述触发器的rn端用于输入所述上升沿交错使能信号,所述触发器的q端用于输出所述下降沿使能信号。

32.在一种可能的实现方式中,还包括第二与非门、第三与非门、第四与非门、第六非门、第七非门、第八非门、第九非门、第十非门和脉冲转换单元;

33.所述第二与非门的第一输入端用于输入fncoreactallbnk,所述第二与非门的第二输入端用于输入burnin,所述第二与非门的输出端与所述第六非门的输入端连接;

34.所述第六非门的输出端用于输出上升沿交错使能信号;

35.所述第三与非门的第一输入端用于输入rosenbnki,所述第三与非门的第二输入端用于输入所述上升沿交错使能信号,所述第三与非门的输出端与所述第七非门的输入端连接;

36.所述第七门的输出端与脉冲转换单元的输入端连接,用于输出所述初始信号;

37.所述脉冲转换单元的输出端与所述第四与非门的第一输入端连接;

38.所述第四与非门的第二输入端用于输入所述上升沿交错使能信号,所述第四与非门的输出端与所述第八非门的输入端连接;

39.所述第八非门的输出端用于输出所述下降沿交错使能信号;

40.所述第九非门的输入端用于输入actstaggerdly,所述第九非门的输出端与所述第十非门的输入端连接,用于输出所述上升沿交错调整延迟反信号;

41.所述第十非门的输出端用于输出所述上升沿交错调整延迟信号。

42.在一种可能的实现方式中,所述计数电路包括多个串联的上升沿触发信号产生电路和多个串联的下降沿触发信号产生电路;

43.上升沿触发信号产生电路,用于根据所述第一周期脉冲信号、上升沿交错使能延时信号、所述上升沿交错使能信号、vss和与所述上升沿触发信号产生电路连接的上一个上升沿计数信号产生电路输出的上升沿计数信号,生成所述上升沿触发信号;

44.下降沿触发信号产生电路,用于根据所述第二周期脉冲信号、下降沿交错使能延时信号、所述下降沿交错使能信号、vss和与所述下降沿触发信号产生电路连接的上一个下降沿计数信号产生电路输出的下降沿计数信号,生成所述下降沿触发信号。

45.在一种可能的实现方式中,所述上升沿计数信号包括第一计数器和第十一非门;

46.所述第一计数器的第一输入端用于输入所述第一周期脉冲信号,所述第一计数器的第二输入端用于输入所述上升沿交错使能延时信号,所述第一计数器的第三输入端用于输入vss或与所述第一计数器连接的上一个第一计数器输出的上升沿计数信号,所述第一计数器的第四输入端用于输入所述上升沿交错使能信号,所述第一计数器的第五输入端用于输入vss,所述第一计数器的输出端和下一个第一计数器的第三输入端、所述第十一非门的输入端连接,用于输出上升沿计数信号;

47.所述第十一非门的输出端用于输出所述上升沿触发信号;

48.所述下降沿计数信号电路包括第二计数器和第十二非门;

49.所述第二计数器的第一输入端用于输入所述第二周期脉冲信号,所述第二计数器的第二输入端用于输入所述下降沿交错使能延时信号,所述第二计数器的第三输入端用于输入vss或与所述第二计数器连接的上一个第二计数器输出的下降沿计数信号,所述第二计数器的第四输入端用于输入下降沿交错使能信号,所述第二计数器的第五输入端用于输入vss,所述第二计数器的输出端与所述第十二非门的输入端连接,用于输出下降沿计数信号;

50.所述第十二非门的输出端用于输出所述下降沿触发信号。

51.在一种可能的实现方式中,还包括第一延时器、第二延时器、第三延时器、第四延

时器、第五延时器、第六延时器、第七延时器、第八延时器、或非门和第十三非门;

52.所述第一延时器的输入端用于输入所述初始信号,所述第一延时器的输出端与所述第二延时器的输入端连接,所述第二延时器的输出端与所述第三延时器的输入端连接,所述第三延时器的输出端与所述第四延时器的输入端连接,所述第四延时器的输出端用于输出所述上升沿交错使能延时信号;

53.所述或非门的第一输入端用于输入所述初始信号,所述或非门的第二输入端用于输入所述下降沿使能信号,所述或非门的输出端与所述第十三非门的输入端连接,所述第十三非门的输出端与所述第五延时器的输入端连接,所述第五延时器的输出端与所述第六延时器的输入端连接,所述第六延时器的输出端与所述第七延时器的输入端连接,所述第七延时器的输出端与所述第八延时器的输入端连接,所述第八延时器的输出端用于输出所述下降沿交错使能延时信号。

54.第二方面,本发明实施例提供一种集成芯片,包括第一方面任一所述的交错信号产生电路。

55.本发明有益效果如下:

56.本发明实施例中,计数电路对第一周期脉冲信号和第二周期脉冲信号进行计数,生成上升沿时钟计数反信号和下降沿触发信号,信号产生电路根据输入的上升沿触发信号和输入的下降沿触发信号,生成交错脉冲信号,由于输入到每个信号产生电路的上升沿触发信号之间的间隔可以相同,也可以不同,输入到每个信号产生电路的上升沿触发信号和下降沿触发信号之间的间隔可以相同,也可以不同,因此得到的交错脉冲信号的脉宽和间距可以灵活设置,进而提高交错脉冲信号产生电路的灵活性。

附图说明

57.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简要介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

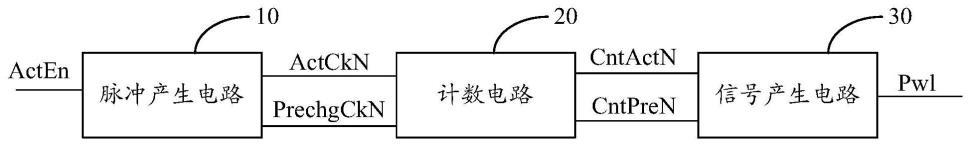

58.图1为本发明实施例提供的一种交错信号产生电路的结构示意图;

59.图2为本发明实施例提供的一种第一周期脉冲信号产生电路的结构示意图;

60.图3为本发明实施例提供的一种下降沿时钟信号产生电路的结构示意图;

61.图4为本发明实施例提供的一种振荡器的结构示意图;

62.图5为本发明实施例提供的另一种交错信号产生电路的结构示意图;

63.图6为本发明实施例提供的一种上升沿交错使能信号产生电路的结构示意图;

64.图7为本发明实施例提供的一种下降沿交错使能信号产生电路的结构示意图;

65.图8为本发明实施例提供的一种上升沿交错调整延迟信号和上升沿交错调整延迟反信号产生电路;

66.图9为本发明实施例提供的一种信号的波形图;

67.图10为本发明实施例提供的一种上升沿触发信号产生电路的结构示意图;

68.图11为本发明实施例提供的一种上升沿触发信号产生电路的结构示意图;

69.图12为本发明实施例提供的一种计数器的结构示意图;

70.图13为本发明实施例提供的一种上升沿交错使能延时信号产生电路的结构示意图;

71.图14为本发明实施例提供的一种下降沿交错使能延时信号产生电路的结构示意图;

72.图15为本发明实施例提供的一种信号产生子电路的结构示意图;

73.图16为本发明实施例提供的又一种信号产生子电路的结构示意图;

74.图17为本发明实施例提供的一种交错信号的波形图;

75.图18为本发明实施例提供的又一种信号产生子电路的结构示意图;

76.图19为本发明实施例提供的又一种交错信号的波形图;

77.图20为本发明实施例提供的又一种信号产生子电路的结构示意图;

78.图21为本发明实施例提供的又一种交错信号的波形图;

79.图22为本发明实施例提供的又一种信号产生子电路的结构示意图;

80.图23为本发明实施例提供的又一种交错信号的波形图。

具体实施方式

81.为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作进一步地详细描述,显然,所描述的实施例仅仅是本发明一部份实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

82.本技术实施例提供一种交错信号产生电路和集成芯片,以解决现有技术中交错信号产生电路灵活性差的问题。

83.其中,交错信号产生电路和集成芯片是基于同一发明构思的,由于交错信号产生电路与集成芯片解决技术问题的原理相似,因此,信号交错产生电路与集成芯片的实施可以相互参见,重复之处不再赘述。

84.下述实施例的具体介绍中,需要说明的是,本技术中所涉及的多个,是指两个或两个以上。本技术中所涉及的术语“或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。本技术中所涉及的连接,描述两个对象的连接关系,可以表示两种连接关系,例如,a和b连接,可以表示:a与b直接连接,a通过c和b连接这两种情况。另外,需要理解的是,在本技术的描述中,“第一”、“第二”“第三

”…

等词汇,仅用于区分描述的目的,而不能理解为指示或暗示相对重要性,也不能理解为指示或暗示顺序。

85.如图1所示,为本发明实施例提供的一种交错信号产生电路的结构示意图,包括脉冲产生电路10、计数电路20和信号产生电路30。

86.脉冲产生电路10,用于根据初始信号acten,生成第一周期脉冲信号actckn和第二周期脉冲信号prechgckn;

87.计数电路20,用于对所述第一周期脉冲信号actckn和所述第二周期脉冲信号prechgckn进行计数,生成上升沿触发信号cntactn和下降沿触发信号cntpren;

88.信号产生电路30,用于根据输入的上升沿触发信号cntactn和输入的下降沿触发信号cntprechgn,生成交错脉冲信号pwl。

89.本发明实施例中,计数电路对第一周期脉冲信号和第二周期脉冲信号进行计数,生成上升沿触发信号和下降沿触发信号,信号产生电路根据输入的上升沿触发信号和输入的下降沿触发信号,生成交错脉冲信号,由于输入到每个信号产生电路的上升沿触发信号之间的间隔可以相同,也可以不同,输入到每个信号产生电路的上升沿触发信号和下降沿触发信号之间的间隔可以相同,也可以不同,因此得到的交错脉冲信号的脉宽和间距可以灵活设置,进而提高交错脉冲信号产生电路的灵活性。

90.在具体实施中,脉冲产生电路10可以包括第一周期脉冲信号产生电路和第二周期脉冲信号产生电路。

91.第一周期脉冲信号产生电路,用于根据初始信号acten和第一控制信号,生成第一周期脉冲信号actckn;

92.下降沿时钟信号产生电路,根据初始信号acten和第二控制信号,生成第二周期脉冲信号prechgckn。

93.其中,第一控制信号可以包括上升沿交错使能信号fnstaggeracten、上升沿交错调整延时信号fnadjactstaggerdly和上升沿交错调整延迟反信号fnadjactstaggerdlyn,第二控制信号可以包括下降沿交错使能信号fnstaggerprechgen、上升沿交错调整延时信号fnadjactstaggerdly、上升沿交错调整延迟反信号fnadjactstaggerdlyn和下降沿使能信号preen。

94.具体的,如图2所示,为本发明实施例提供的第一周期脉冲信号产生电路的结构示意图。

95.上升沿时钟信号产生电路可以包括第一振荡器201和第三非门inv3;

96.第一振荡器201的第一输入端用于输入初始信号acten,第一振荡器201的第二输入端用于输入上升沿交错使能信号fnstaggeracten,第一振荡器201的第三输入端用于输入上升沿交错调整延迟信号fnadjactstaggerdly,第一振荡器201的第四输入端用于输入上升沿交错调整延迟反信号fnadjactstaggerdlyn,第一振荡器201的输出端与第三非门inv3的输入端连接,用于输出上升沿时钟信号actclk;第三非门inv3的输出端用于输出第一周期脉冲信号actckn。

97.如图3所示,为本发明实施例提供的一种第二周期脉冲信号产生电路的结构示意图。

98.第二周期脉冲信号产生电路可以包括第二振荡器202、第四非门inv4和第一与非门an1;

99.第四非门inv4的输入端用于输入初始信号acten,第四非门inv4的输出端与第二振荡器202的第一输入端连接,用于输出初始信号反信号prechgen;

100.第二振荡器202的第二输入端用于输入所述下降沿交错使能信号fnstaggerpreen,第二振荡器202的第三输入端用于输入上升沿交错调整延迟信号fnadjactstaggerdly,第二振荡器202的第四输入端用于输入上升沿交错调整延迟反信号fnadjactstaggerdlyn,第二振荡器202的输出端与第一与非门an1的第一输入端连接,用于输出下降沿时钟信号prechgclk;

101.第一与非门an1的第二输入端用于输入下降沿使能信号preen,第一与非门an1的输出端用于输出第二周期脉冲信号prechgckn。

102.本发明实施例中,第一振荡器201和第二振荡器202的具体结构可以相同,具体的,可以参照图4所示的振荡器结构。

103.如图4所示,为本发明实施例提供的一种振荡器的结构示意图。

104.振荡器可以包括第五与非门an5、第六与非门an6、第十四非门inv14、第十五非门inv15、第十六非门inv16、第十七非门inv17、第十八非门inv18、第十九非门inv19、第二十非门inv20、第二十一非门inv21、第二十二非门inv22、第一选择器mul1、第二选择器mul2、第三选择器mul3、第一触发器dff1、第二触发器dff2、第三触发器dff3、第九延时器409、第十延时器410、第十一延时器411第十二延时器412和第一脉冲转换单元413;

105.第五与非门an5的第一输入端与第十六非门inv16的输出端连接,第五与非门an5的第二输入端作为振荡器的第一输入端,第五与非门an5的输出端与第六与非门an6的第一输入端连接,用于输出延时信号osc0;第六与非门an6的第二输入端、第一触发器dff1的rn端、第二触发器dff2的rn端和第三触发器dff3的rn端作为振荡器的第二输入端,第六与非门an6的输出端与第十四非门inv14的输入端连接;第十四非门inv14的输出端与第十五非门inv15的输入端连接,用于输出延时反信号osc0n;第十五非门inv15的输出端与第一选择器mul1的第一输入端、第九延时器409的输入端连接;第九延时器409的输出端与第一选择器mul1的第二输入端连接;第一选择器mul1的输出端与第二选择器mul2的第一输入端、第十延时器410的输入端连接,第一选择器mul1的第一控制端作为振荡器的第三输入端,用于输入第一个上升沿交错调整延迟信号fnadjactstaggerdly《0》,第一选择器mul1的第二控制端作为振荡器的第四输入端,用于输入第一个上升沿交错调整延迟反信号fnadjactstaggerdlyn《0》;第十延时器410的输出端与第二选择器mul2的第二输入端连接;第二选择器mul2的输出端与第十一延时器411的输入端连接,第二选择器mul2的第一控制端作为振荡器的第三输入端,用于输入第二个上升沿交错调整延时信号fnadjactstaggerdly《1》,第二选择器mul2的第二控制端作为振荡器的第四输入端,用于输入第二个上升沿交错调整延迟反信号fnadjactstaggerdlyn《1》;第十一延时器411的输出端与第十二延时器412的输入端连接;第十二延时器412的输出端与第十六非门inv16的输入端连接;

106.第一触发器dff1的d输入端与第十七非门inv17的输出端、第二触发器dff2的clkn端连接,第一触发器dff1的clk端,用于输入延时信号osc0,第一触发器dff1的clkn端用于输入延时反信号osc0n,第一触发器dff1的q端与第十七非门inv7的输入端、第二触发器dff2的clk端连接;第二触发器dff2的d端与第十八非门inv18的输出端、第三触发器dff3的clkn端连接,第二触发器dff2的q端与第十八非门inv18的输入端、第三触发器dff3的clk端、第三选择器mul3的第一输入端连接;第三触发器dff3的d端与第十九非门inv19的输出端连接,第三触发器dff3的q端与第十九非门inv19的输入端、第三选择器mul3的第二输入端连接;第三选择器mul3的输出端与第一脉冲转换单元413的输入端连接,第一脉冲转换单元413的输出端与第二十非门inv20的输入端连接,第三选择器mul3的第一控制端作为振荡器的第三输入端,用于输入第三个上升沿交错调整延时信号fnadjactstaggerdly《2》,第三选择器mul3的第二控制端作为振荡器的第四输入端,用于输入第三个上升沿交错调整延迟反信号fnadjactstaggerdlyn《2》;第二十非门inv20的输出端与第二十一非门inv21的输入端连接;第二十一非门inv21的输出端与第二十二非门inv22的输入端连接;第二十二非门

inv22的输出端作为振荡器的输出端。

107.在一种实施例中,如图5所示,本发明实施例提供的交错信号产生电路还可以包括第五非门inv5和第四触发器dff4;

108.第五非门inv5的输入端与第四触发器dff4的时钟clk端连接,用于输入第一原始信号actenplan,第五非门inv5的输出端与第四触发器dff4的反相时钟clkn端连接;

109.第四触发器dff4的输入d端接地,第四触发器dff4的异步复位rn端用于输入上升沿交错使能信号fnstaggeracten,第四触发器dff4的输出q端用于输出下降沿使能信号preen。

110.在具体实施中,本发明实施例还包括上升沿交错使能信号产生电路、下降沿交错使能信号产生电路、上升沿交错调整延迟信号和上升沿交错调整延迟反信号产生电路。

111.上升沿交错使能信号电路,用于根据第二原始信号fncoreactallbnk和第三原始信号burnin,生成上升沿交错使能信号fnstaggeracten;

112.下降沿交错使能信号产生电路,用于根据第四原始信号rosenbnki和上升沿交错使能信号fnstaggeracten,生成下降沿交错使能信号fnstaggerpreen;

113.上升沿交错调整延迟信号和上升沿交错调整延迟反信号产生电路,用于根据上升沿交错延迟信号actstaggerdly,生成上升沿交错调整延迟反信号fnadjactstaggerdlyn和上升沿交错调整延迟信号fnadjactstaggerdly。

114.如图6所示,为本发明实施例提供的一种上升沿交错使能信号产生电路的结构示意图。

115.上升沿交错使能信号产生电路包括第二与非门an2和第六非门inv6;

116.第二与非门an2的第一输入端用于输入第二原始信号fncoreactallbnk,第二与非门an2的第二输入端用于输入第三原始信号burnin,第二与非门an2的输出端与第六非门inv6的输入端连接;第六非门inv6的输出端用于输出上升沿交错使能信号fnstageracten。

117.如图7所示,为本发明实施例提供的一种下降沿交错使能信号产生电路的结构示意图。

118.下降沿交错使能信号产生电路包括第三与非门an3、第四与非门an4、第七非门inv7、第八非门inv8和脉冲转换单元1011;

119.第三与非门an3的第一输入端用于输入第四原始信号rosenbnki,第三与非门an3的第二输入端用于输入上升沿交错使能信号fnstaggeracten,第三与非门an3的输出端与第七非门inv7的输入端连接;

120.第七非门inv7的输出端与脉冲转换单元1011的输入端连接,用于输出初始信号acten;

121.脉冲转换单元1011的输出端与第四与非门an4的第一输入端连接;

122.第四与非门an4的第二输入端用于输入上升沿交错使能信号fnstaggeracten,第四与非门an4的输出端与第八非门inv8的输入端连接;

123.第八非门inv8的输出端用于输出下降沿交错使能信号fnstagepreen。

124.如图8所示,为本发明实施例提供的一种上升沿交错调整延迟信号和上升沿交错调整延迟反信号产生电路。

125.上升沿交错调整延迟信号和上升沿交错调整延迟反信号产生电路包括第九非门

inv9和第十非门inv10;

126.第九非门inv9的输入端用于输入actstaggerdly,第九非门inv9的输出端与第十非门inv10的输入端连接,用于输出上升沿交错调整延迟反信号fnadjactstaggerdlyn,第十非门inv10的输出端用于输出上升沿交错调整延迟信号fnadjactstaggerdly。

127.下面结合波形图对初始信号acten、上升沿时钟信号actclk、下降沿时钟信号prechgclk、第一周期脉冲信号actckn和第二周期脉冲信号prechgckn进行说明。

128.如图9所示,初始信号acten包括一个上升沿和一个下降沿,上升沿时钟信号actclk中的第一个脉冲在初始信号acten的上升沿处,然后在每个延时时间处,产生一个脉冲,同理,下降沿时钟信号preclk的第一个脉冲在初始信号acten的下降沿处,然后每在一个延时时间处,产生一个脉冲。其中,上升沿时钟信号actclk中的第一个脉冲和最后一个脉冲之间的时间间隔与初始信号acten的上升沿和下降沿之间的时间间隔相同,下降沿时钟信号preclk的第一个脉冲和最后一个脉冲之间的间隔与初始信号acten的上升沿和下降沿之间的时间间隔相同。

129.从图9中可以看出,第一周期脉冲信号actckn为上升沿时钟信号actclk的反相信号,第二周期脉冲信号为下降沿时钟信号preclk的反相信号。

130.上述实施例,根据初始信号,生成第一周期脉冲信号和第二周期脉冲信号,再通过对第一周期脉冲信号和第二周期脉冲信号进行计数,下面对如何对第一周期脉冲信号和第二周期脉冲信号进行计数进行说明。

131.本发明实施例提供的计数电路包括可以多个串联的上升沿触发信号产生电路和多个下降沿触发信号产生电路。

132.上升沿触发信号产生电路的个数与下降沿触发信号产生电路的个数相同。

133.针对每个上升沿触发信号产生电路,用于根据第一周期脉冲信号actckn、上升沿交错使能延时信号fnstaggeractendly、上升沿交错使能信号fnstaggeracten、供电电压和与该上升沿触发信号产生电路连接的上一个上升沿触发信号产生电路输出的上升沿计数信号cntact,生成上升沿触发信号cntactn;

134.针对每个下降沿触发信号产生电路,用于根据第二周期脉冲信号prechgckn、下降沿交错脉冲延时信号fnstaggerprechgendly、下降沿交错使能信号fnstaggerprechgen、供电电压和与该下降沿触发信号产生电路串联连接的上一个下降沿触发信号产生电路输出的下降沿计数信号cntpre,生成下降沿触发信号cntpren。

135.下面对上升沿触发信号产生电路和下降沿触发信号产生电路进行详细说明。

136.如图10所示,为本发明实施例提供的上升沿触发信号产生电路的结构示意图。

137.上升沿触发信号产生电路可以包括第一计数器101和第十一非门inv11;

138.第一计数器101的第一输入端用于输入第一周期脉冲信号actckn,第一计数器101的第二输入端用于输入上升沿交错使能延时信号fnstaggeractendly,第一计数器101的第三输入端用于输入供电电压vss或与第一计数器101连接的上一个第一计数器101输出的上升沿计数信号cntact,第一计数器101的第四输入端用于输入上升沿交错使能信号fnstaggeracten,第一计数器101的第五输入端用于输入供电电压vss,第一计数器101的输出端和下一个第一计数器101的第三输入端、第十一非门inv11的输入端连接,用于输出上升沿计数信号cntact;

139.第十一非门inv11的输出端用于输出上升沿触发信号cntactn。

140.需要说明的是,图10中cntact《7:0》代表有8个cntact,即cntact《0》、cntact《1》、cntact《2》、cntact《3》、cntact《4》、cntact《5》、cntact《6》、cntact《7》,也就是有8个上升沿时钟计数电路,第一个上升沿计数电路中的第一计数器的第三输入端,也即in端,输入供电电压vss,第二个上升沿计数电路中的第一计数器的输出端与第一个上升沿触发信号产生电路中的第一计数器的第三输入端连接,依此类推。

141.如图11所示,为本发明实施例提供的下降沿触发信号产生电路的结构示意图。

142.下降沿触发信号产生电路可以包括第二计数器102和第十二非门inv12;

143.第二计数器102的第一输入端用于输入第二周期脉冲信号preckn,第二计数器102的第二输入端用于输入下降沿交错使能延时信号fnstaggerpreendly,第二计数器102的第三输入端用于输入供电电压vss或与该第二计数器102连接的上一个第二计数器102输出的下降沿计数信号cntpre,第二计数器102的第四输入端用于输入下降沿交错使能信号fnstaggerpreen,第二计数器102的第五输入端用于输入供电电压vss,第二计数器102的输出端与第十二非门inv12的输入端连接,用于输出下降沿计数信号cntpre;

144.第十二非门inv12的输出端用于输出下降沿触发信号cntpren。

145.需要说明的是,图11中cntpre《7:0》代表有8个cntpre,即cntpre《0》、cntpre《1》、cntpret《2》、cntpre《3》、cntpre《4》、cntpre《5》、cntpre《6》、cntpre《7》,也就是有8个下降沿触发信号产生电路,第一个下降沿触发信号产生电路中的第二计数器的第三输入端,也即in端,输入vss,第二个下降沿触发信号产生电路中的第二计数器的输出端与第一个下降沿触发信号产生电路中的第二计数器的第三输入端连接,依此类推。

146.在具体实施中,第一计数器101和第二计数器102可以为相同的计数器,如图12所示,该计数器可以包括第二十四非门inv24、第二十五非门inv25、第二十六非门inv26、第二十七非门inv27、第五触发器dff5和第四选择器mul4。

147.第二十四非门的输入端和第四选择器mul4的第二控制端作为计数器的en端,第二十四非门inv27的输出端与第四选择器mul4的第一控制端连接,第二十五非门inv25的输入端作为计数器的in端,第二十五非门inv25的输出端与第四选择器mul4的第一输入端连接,第二十六非门inv26的输入端作为计数器的temp端,第二十六非门inv26的输出端与第四选择器mul4的第二输入端连接,第二十七非门inv27的输入端和第五触发器dff5的clk端作为计数器的clk端,第二十七非门inv27的输出端与第五触发器dff5的clkn端连接,第五触发器dff5的rn端作为计数器的rn端,第五触发器dff5的q端作为计数器的cnt端。

148.上述实施例中,计数电路对第一周期脉冲信号和第二周期脉冲信号进行计数,生成上升沿触发信号和下降沿触发信号,信号产生电路根据输入的上升沿触发信号和输入的下降沿触发信号,生成交错脉冲信号。

149.本发明实施例提供的交错脉冲信号产生电路,还可以包括上升沿交错使能延时信号产生电路和下降沿交错使能延时信号产生电路;

150.如图13所示,上升沿交错使能延时信号产生电路可以包括第一延时器1301、第二延时器1302、第三延时器1303和第四延时器1304;

151.第一延时器1301的输入端用于输入初始信号acten,第一延时器1301的输出端与第二延时器1302的输入端连接,第二延时器1302的输出端与第三延时器1303的输入端连

接,第三延时器1303的输出端与第四延时器1304的输入端连接,第四延时器1304的输出端用于输出上升沿交错使能延时信号fnstaggeractendly。

152.如图14所示,下降沿交错使能延时信号产生电路可以包括第五延时器1305、第六延时器1306、第七延时器1307、第八延时器1308、或非门1309和第十三非门inv13;

153.或非门1309的第一输入端用于输入初始信号acten,或非门1309的第二输入端用于输入下降沿使能信号preen,或非门1309的输出端与第十三非门inv13的输入端连接,第十三非门inv13的输出端与第五延时器1305的输入端连接,第五延时器1305的输出端与第六延时器1306的输入端连接,第六延时器1306的输出端与第七延时器1307的输入端连接,第七延时器1307的输出端与第八延时器1308的输入端连接,第八延时器1308的输出端用于输出下降沿交错使能延时信号fnstaggerpreendly。

154.下面对信号产生电路进行详细说明。

155.本发明实施例提供的信号产生电路可以包括多个信号产生子电路,每个信号产生子电路,用于根据输入的上升沿触发信号和输入的下降沿触发信号,生成交错脉冲子信号,多个交错脉冲子信号组成交错脉冲信号。

156.在具体实施中,如果输入到多个信号产生子电路中相邻的信号产生子电路的上升沿触发信号的间隔相同,则产生的交错脉冲信号为等间隔的交错脉冲信号;

157.如果输入到多个所述信号产生子电路中相邻的信号产生子电路的上升沿触发信号的间隔不同,则生成的交错脉冲信号为非等间隔的交错脉冲信号;

158.如果输入到每个信号产生子电路中的上升沿触发信号和下降沿触发信号间隔的时钟周期相同,则生成的交错脉冲信号为等脉宽的交错脉冲信号;

159.如果输入到每个信号产生子电路中的上升沿触发信号和对应的下降沿触发信号间隔的时钟周期不同,则生成的交错脉冲信号为非等脉宽的交错脉冲信号。

160.如图15所示,为本发明实施例提供的信号产生子电路的结构示意图。

161.信号产生子电路可以包括sr锁存器1051、第一非门inv1和第二非门inv2;

162.sr锁存器1051的第一输入端用于输入上升沿触发信号cntactn,sr锁存器1051的第二输入端用于输入下降沿触发信号cntpren,sr锁存器1051的第三输入端用于输入上升沿交错使能信号fnstaggeracten,sr锁存器1051的输出端与第一非门inv1的输入端连接;第一非门inv1的输出端与第二非门inv2的输入端连接;第二非门inv2的输出端输出交错脉冲子信号pwl(n)。

163.为了便于理解,下面分别对交错脉冲信号为等间隔等脉冲、等间隔非等脉冲、非等间隔等脉冲和非等间隔非等脉冲进行说明。

164.实施例一:

165.如图16所示,输入到第一个信号产生子电路中的上升沿触发信号为cntactn《0》,下降沿触发信号为cntpren《0》,输入到第二个信号产生子电路中的上升沿触发信号为cntactn《1》,下降沿触发信号为cntpren《1》,输入到第三个信号产生子电路中的上升沿触发信号为cntactn《2》,下降沿触发信号为cntpren《2》。

166.cntactn《0》和cntactn《1》之间的时间间隔为第一周期脉冲信号的一个周期,cntactn《1》和cntactn《2》的时间间隔为第一周期脉冲信号的一个周期,因此,产生的交错脉冲信号为等间隔的交错脉冲信号;

167.cntactn《0》和cntpren《0》之间的时间间隔为初始信号acten的一个周期,cntactn《1》和cntpren《1》之间的时间间隔为初始信号acten的一个周期,cntactn《2》和cntpren《2》之间的时间间隔为初始信号acten的一个周期,因此,产生的交错脉冲信号为等脉冲的交错脉冲信号。

168.需要说明的是,输出交错子信号pwl(1)的电路和输出交错子信号pwl(2)的电路为相邻的信号产生子电路。输出交错子信号pwl(2)的电路和输出交错子信号pwl(3)的电路为相邻的信号产生子电路;cntactn《0》和cntactn《1》为输入到相邻的信号产生子电路中的上升沿触发信号,cntactn《1》和cntactn《2》也为输入到相邻的信号产生子电路中的上升沿触发信号;cntactn《0》和cntpren《0》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《1》和cntpren《1》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《2》和cntpren《2》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号。

169.如图17所示,为基于图16产生的信号的波形图。

170.假设第一周期脉冲信号的时钟周期为t,初始信号的周期为t,则交错脉冲信号之间的间隔为t,脉宽为t。从图17中也可以看出,该交错脉冲信号为等间隔等脉冲的交错脉冲信号。

171.实施例二:

172.如图18所示,输入到第一个信号产生子电路中的上升沿触发信号为cntactn《0》,下降沿触发信号为cntpren《0》,输入到第二个信号产生子电路中的上升沿触发信号为cntactn《2》,下降沿触发信号为cntpren《1》,输入到第三个信号产生子电路中的上升沿触发信号为cntactn《5》,下降沿触发信号为cntpren《2》。

173.cntactn《0》和cntactn《2》之间的时间间隔为第一周期脉冲信号的两个周期,cntactn《2》和cntactn《5》的时间间隔为第一周期脉冲信号的三个周期,因此,产生的交错脉冲信号为非等间隔的交错脉冲信号;

174.cntactn《0》和cntpren《0》之间的时间间隔为初始信号acten的一个周期,cntactn《2》和cntpren《1》之间的时间间隔为初始信号acten的一个周期减去一个下降沿反信号的时钟周期,cntactn《5》和cntpren《2》之间的时间间隔为初始信号acten的一个周期减去三个下降沿反信号的时钟周期,因此,产生的交错脉冲信号为非等脉冲的交错脉冲信号。

175.需要说明的是,输出交错子信号pwl(1)的电路和输出交错子信号pwl(2)的电路为相邻的信号产生子电路。输出交错子信号pwl(2)的电路和输出交错子信号pwl(3)的电路为相邻的信号产生子电路;cntactn《0》和cntactn《2》为输入到相邻的信号产生子电路中的上升沿触发信号,cntactn《2》和cntactn《5》也为输入到相邻的信号产生子电路中的上升沿触发信号;cntactn《0》和cntpren《0》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《2》和cntpren《1》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《5》和cntpren《2》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号。

176.如图19所示,为基于图18产生的信号的波形图。

177.假设第一周期脉冲信号的时钟周期为t,下降沿反信号的时钟周期也为t,初始信号的周期为t。从图17中也可以看出,该交错脉冲信号为非等间隔非等脉冲的交错脉冲信

号。

178.实施例三:

179.如图20所示,输入到第一个信号产生子电路中的上升沿触发信号为cntactn《0》,下降沿触发信号为cntpren《0》,输入到第二个信号产生子电路中的上升沿触发信号为cntactn《1》,下降沿触发信号为cntpren《2》,输入到第三个信号产生子电路中的上升沿触发信号为cntactn《2》,下降沿触发信号为cntpren《5》。

180.cntactn《0》和cntactn《1》之间的时间间隔为第一周期脉冲信号的一个周期,cntactn《1》和cntactn《2》的时间间隔为第一周期脉冲信号的一个周期,因此,产生的交错脉冲信号为等间隔的交错脉冲信号;

181.cntactn《0》和cntpren《0》之间的时间间隔为初始信号acten的一个周期,cntactn《1》和cntpren《2》之间的时间间隔为初始信号acten的一个周期加上一个下降沿反信号的时钟周期,cntactn《5》和cntpren《2》之间的时间间隔为初始信号acten的一个周期加上三个下降沿反信号的时钟周期,因此,产生的交错脉冲信号为非等脉冲的交错脉冲信号。

182.需要说明的是,输出交错子信号pwl(1)的电路和输出交错子信号pwl(2)的电路为相邻的信号产生子电路。输出交错子信号pwl(2)的电路和输出交错子信号pwl(3)的电路为相邻的信号产生子电路;cntactn《0》和cntactn《1》为输入到相邻的信号产生子电路中的上升沿触发信号,cntactn《1》和cntactn《2》也为输入到相邻的信号产生子电路中的上升沿触发信号;cntactn《0》和cntpren《0》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《1》和cntpren《2》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《5》和cntpren《2》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号。

183.如图21所示,为基于图20产生的信号的波形图。

184.假设第一周期脉冲信号的时钟周期为t,下降沿反信号的时钟周期也为t,初始信号的周期为t。从图21中也可以看出,该交错脉冲信号为等间隔非等脉冲的交错脉冲信号。

185.实施例四:

186.如图22所示,输入到第一个信号产生子电路中的上升沿触发信号为cntactn《0》,下降沿触发信号为cntpren《0》,输入到第二个信号产生子电路中的上升沿触发信号为cntactn《1》,下降沿触发信号为cntpren《1》,输入到第三个信号产生子电路中的上升沿触发信号为cntactn《4》,下降沿触发信号为cntpren《4》。

187.cntactn《0》和cntactn《1》之间的时间间隔为第一周期脉冲信号的一个周期,cntactn《1》和cntactn《4》的时间间隔为第一周期脉冲信号的三个周期,因此,产生的交错脉冲信号为非等间隔的交错脉冲信号;

188.cntactn《0》和cntpren《0》之间的时间间隔为初始信号acten的一个周期,cntactn《1》和cntpren《1》之间的时间间隔为初始信号acten的一个周期,cntactn《4》和cntpren《4》之间的时间间隔为初始信号acten的一个周期,因此,产生的交错脉冲信号为等脉冲的交错脉冲信号。

189.需要说明的是,输出交错子信号pwl(1)的电路和输出交错子信号pwl(2)的电路为相邻的信号产生子电路。输出交错子信号pwl(2)的电路和输出交错子信号pwl(3)的电路为相邻的信号产生子电路;cntactn《0》和cntactn《1》为输入到相邻的信号产生子电路中的上

升沿触发信号,cntactn《1》和cntactn《4》也为输入到相邻的信号产生子电路中的上升沿触发信号;cntactn《0》和cntpren《0》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《1》和cntpren《1》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号,cntactn《4》和cntpren《4》为输入到同一个信号产生子电路中的上升沿触发信号和与其对应的下降沿触发信号。

190.如图23所示,为基于图22产生的信号的波形图。

191.假设第一周期脉冲信号的时钟周期为t,下降沿反信号的时钟周期也为t,初始信号的周期为t。从图23中也可以看出,该交错脉冲信号为非等间隔等脉冲的交错脉冲信号。

192.本发明实施例提供的交错脉冲信号产生电路,计数电路对第一周期脉冲信号和第二周期脉冲信号进行计数,生成上升沿触发信号和下降沿触发信号,信号产生电路根据输入的上升沿触发信号和输入的下降沿触发信号,生成交错脉冲信号,由于输入到每个信号产生电路的上升沿触发信号之间的间隔可以相同,也可以不同,输入到每个信号产生电路的上升沿触发信号和下降沿触发信号之间的间隔可以相同,也可以不同,因此得到的交错脉冲信号的脉宽和间距可以灵活设置,进而提高交错脉冲信号产生电路的灵活性。

193.基于相同的发明构思,本发明实施例还提供一种集成芯片,该集成芯片包括上述任一一种交错信号产生电路。

194.集成芯片的具体实施可以参见交错信号产生电路的实施,此处不再赘述。

195.显然,本领域的技术人员可以对本公开进行各种改动和变型而不脱离本公开的精神和范围。这样,倘若本公开的这些修改和变型属于本公开权利要求及其等同技术的范围之内,则本公开也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1