数字控制信号生成电路及电子设备的制作方法

1.本技术属于电子技术领域,尤其涉及一种数字控制信号生成电路及电子设备。

背景技术:

2.不同公司出品的微处理器芯片会采用不同的数字控制信号进行复位或上电启动。有些芯片要求这上电启动信号和复位信号平时处在低电平,需要复位或上电启动时为高电平;有些芯片正好相反,要求这上电启动信号和复位信号平时处在高电平而在需要复位或上电启动时为低电平。现有方案为了配合这两种不同的芯片,上电启动信号生成电路或复位信号生成电路需要配置两颗不同的芯片,其缺点是会增加开发成本和流片成本,同时给生产和和库存管理带来麻烦。

3.故亟待提供一种数字控制信号生成电路,以支持上述两种不同的数字信号电平的输出。

技术实现要素:

4.本技术的目的在于提供一种数字控制信号生成电路及电子设备,以实现兼容高电平和低电平两种不同的数字信号电平输出。

5.本技术实施例提供了一种数字控制信号生成电路,包括从机,所述从机包括:通用输出电路,配置为将第一数字信号转换为第二数字信号以驱动上下拉电路;所述上下拉电路,与所述通用输出电路连接,配置为根据所述第二数字信号将所述上下拉电路的输出端进行上拉或者下拉以改变所述上下拉电路的输出端的电平状态。

6.在其中一个实施例中,所述数字控制信号生成电路还包括电阻组件;所述电阻组件的第一端与所述上下拉电路的输出端连接,所述电阻组件的第二端上拉至第一电压或者下拉至电源地;当所述上下拉电路的输出端为高阻态时,所述上下拉电路的输出电平由所述电阻组件的第二端连接的电压决定。

7.在其中一个实施例中,所述数字控制信号生成电路还包括:第一通信电路,与所述通用输出电路连接,配置为接收单线通信信号,并对所述单线通信信号进行解码以输出所述第一数字信号;所述通用输出电路具体配置为对所述第一数字信号进行锁存以输出所述第二数字信号。

8.在其中一个实施例中,所述第一通信电路、所述通用输出电路以及所述上下拉电路集成于一个芯片中,所述电阻组件设置在所述芯片之外。

9.在其中一个实施例中,所述数字控制信号生成电路还包括:控制电路,与所述第二通信电路连接,配置为输出控制信号;第二通信电路,与所述控制电路和所述第一通信电路连接,配置为根据所述控制信号从线路发送所述单线通信信号。

10.在其中一个实施例中,所述通用输出电路包括第一d触发器和第二d触发器;所述第一d触发器的数据输入端和所述第二d触发器的数据输入端d连接至所述通用输出电路的第一数字信号输入端,所述第一d触发器的时钟端和所述第二d触发器的时钟端共同连接至所述通用输出电路的时钟端,所述第一d触发器的反相数据锁存输出端和所述第二d触发器的数据锁存输出端共同连接至所述通用输出电路的第二数字信号输出端。

11.在其中一个实施例中,所述上下拉电路包括第一场效应管和第二场效应管;所述第一场效应管为pmos,第二场效应管为nmos;所述第一场效应管的源极与第一电源连接,所述第一场效应管的栅极和所述第二场效应管的栅极共同连接至所述上下拉电路的第二数字信号输入端,所述第一场效应管的漏极和所述第二场效应管的漏极共同连接至所述上下拉电路的输出端,所述第二场效应管的源极与电源地连接。

12.在其中一个实施例中,所述第一场效应管和所述第二场效应管都处于截止状态时,如果所述电阻组件上拉至所述第一电压,所述上下拉电路的输出端被所述电阻组件上拉到所述第一电压,以使所述上下拉电路输出高电平的数字控制信号;如果所述电阻组件下拉至电源地,则所述上下拉电路的输出端被所述电阻组件下拉到电源地,以使所述上下拉电路输出低电平的数字控制信号。

13.在其中一个实施例中,所述第二数字信号为第一状态或者停止所述第二数字信号输入时,所述第一场效应管和所述第二场效应管均处于截止状态。

14.在其中一个实施例中,所述第二数字信号为第二状态,且所述电阻组件上拉至所述第一电压时,所述第一场效应管根据所述第二状态的所述第二数字信号截止,所述第二场效应管根据所述第二状态的所述第二数字信号导通至电源地,所述上下拉电路的输出端下拉至电源地以使所述上下拉电路输出低电平的数字控制信号。

15.在其中一个实施例中,所述第二数字信号为第三状态,且所述电阻组件下拉至电源地时,所述第二场效应管根据所述第三状态的所述第二数字信号截止,所述第一场效应管根据所述第三状态的所述第二数字信号导通至所述第一电压,所述上下拉电路的输出端上拉至所述第一电压以使所述上下拉电路输出高电平的所述数字控制信号。

16.本技术实施例还提供一种电子设备,所述电子设备包括上述的数字控制信号生成电路。

17.本发明实施例与现有技术相比存在的有益效果包括:由于可以改变上下拉电路的输出端的电平状态,对有不同复位电平或上电启动逻辑电平需求的微处理器,仅需开发一个数字控制信号生成电路(一个芯片),即可以达到同时支持不同类型的上述微处理器芯片的目的,降低了开发成本,同时便于生产和和库存管理。

附图说明

18.为了更清楚地说明本发明实施例中的技术发明,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

19.图1为本技术一实施例提供的数字控制信号生成电路的一种结构示意图;

图2为本技术一实施例提供的数字控制信号生成电路的另一种结构示意图;图3为本技术一实施例提供的数字控制信号生成电路的另一种结构示意图;图4为本技术一实施例提供的数字控制信号生成电路的另一种结构示意图;图5为本技术一实施例提供的数字控制信号生成电路的另一种结构示意图;图6为本技术一实施例提供的数字控制信号生成电路的一种示例电路原理图;图7为本技术一实施例提供的数字控制信号生成电路的另一种示例电路原理图。

具体实施方式

20.为了使本技术所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

21.需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

22.需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

23.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

24.相关技术的tws蓝牙耳机系统通常包含一个充电舱和两只蓝牙耳机。

25.充电舱内含有第一电池、放电电路、微处理器以及其它电路(如第一充电电路)。蓝牙耳机包括第二电池、第二充电电路以及蓝牙芯片等元件。当耳机进入或者离开充电舱时,蓝牙耳机的内部电路需要产生一个复位信号或一个上电启动信号。在蓝牙耳机进入充电舱时,往往需要一个预设电平的复位信号以使蓝牙芯片复位,确保蓝牙芯片的程序处在正常的工作状态。当蓝牙耳机在充电舱里面时,蓝牙耳机处于关机状态以省电。在蓝牙耳机被取出充电舱时,蓝牙耳机需要开机,从而可以自动和手机的蓝牙连接,蓝牙耳机内通常包括一个电路,在耳机出舱时发送一个预设电平的上电启动信号以达到开启蓝牙芯片的目的。

26.然而该技术有以下缺点:不同公司出品的蓝牙芯片或微处理器芯片会采用不同电平进行复位或开机,故预设电平可能为高电平,也可能为低电平,从而需要配置两颗不同的芯片,增加了开发成本和流片成本,同时给生产和和库存管理带来不便。

27.图1示出了本技术较佳实施例提供的数字控制信号生成电路的结构示意图,为了便于说明,仅示出了与本实施例相关的部分,详述如下:上述数字控制信号生成电路包括通用输出电路12和上下拉电路13。

28.通用输出电路12,配置为将第一数字信号转换为第二数字信号以驱动上下拉电路13。

29.上下拉电路13,与通用输出电路12连接,配置为根据第二数字信号将上下拉电路

13的输出端进行上拉或者下拉以改变上下拉电路13的输出端的电平状态,或者根据第二数字信号将上下拉电路的输出端既不上拉也不下拉,使上下拉电路的输出端处于高阻态。

30.如图2所示,数字控制信号生成电路还包括电阻组件14。

31.电阻组件14的第一端与上下拉电路13的输出端连接,电阻组件14的第二端上拉至第一电压或者下拉至电源地。当上下拉电路的输出端为高阻态时,上下拉电路的输出电平由电阻组件的第二端连接的电压决定。

32.相关技术方案通过控制电路发送控制信号至逻辑芯片,以使逻辑芯片生成与蓝牙芯片或微处理器芯片匹配电平的数字控制信号,然而,在逻辑芯片上电后的初始阶段,由于逻辑芯片没有控制信号输入而使输出端处于高阻态,蓝牙芯片或微处理器芯片的上电启动信号端口或复位信号端口处于非稳态,导致配置该数字控制信号生成电路的设备误开机或误复位,系统稳定性差。

33.本技术当没有第二数字信号输入时,由于电阻组件14下拉至电源地或者上拉至第一电压,故上下拉电路13的输出端为稳态的电平,提高了系统的稳定性。且配合芯片外的电阻组件,相同的芯片内电路可以同时支持背景技术中的不同的微处理器对不同复位或上电启动数字信号的要求,故仅需开发一个数字控制信号生成芯片,即可以达到同时支持不同类型的微处理器目的,降低了开发成本,同时便于生产和和库存管理。

34.如图3所示,数字控制信号生成电路还包括第一通信电路11。

35.第一通信电路11,与通用输出电路12连接,配置为接收单线通信信号,并对单线通信信号进行解码以输出第一数字信号;通用输出电路12具体配置为对第一数字信号进行锁存以输出第二数字信号。

36.值得注意的是,第一通信电路11、通用输出电路12以及上下拉电路13可以集成于一个芯片中,电阻组件14设置在该芯片之外。

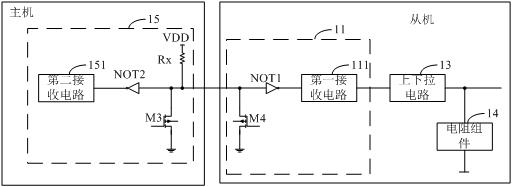

37.如图4所示,数字控制信号生成电路还包括第二通信电路15和控制电路16。

38.控制电路16,配置为输出控制信号;第二通信电路15,与控制电路16和第一通信电路11连接,配置为根据控制信号从线路发送单线通信信号。

39.可以理解的是,当数字控制信号生成电路应用于耳机系统或雾化装置时,耳机系统包括主机(充电盒)及从机(耳机),雾化装置也包括主机(充电盒)及从机(如电子烟的烟杆)。第二通信电路15和控制电路16可以设置在主机中,电阻组件14、第一通信电路11、通用输出电路12以及上下拉电路13可以设置在从机中。

40.通过设置第二通信电路15和第一通信电路11,实现了主机和从机间的通信,以及通过主机侧的控制电路16控制数字控制信号的输出。

41.单线通信指通过除地线以外的一根信号线(单线总线)实现半双工的通讯。如图5所示,单线通信涉及主机(如充电盒)和从机(如耳机或烟杆)。无论主机还是从机,当需要发送信息时,连接在单线总线上的开源的场效应管会被一数字发送信号驱动。以主机侧发送信号为例,主机侧的单线通信信号(数字发送信号)驱动第三场效应管m3,当该第三场效应管m3导通时,单线总线上信号为低;当该第三场效应管关断时,单线总线上信号被上拉电阻rx拉到高电平vdd。单线总线的信号被从机中连接在总线上的第一非门not1接收,第一非门not1的输出端连接至第一接收电路151,第一接收电路151根据接收到的数字信号进行解码

并输出第一数字信号。当从机需要发送信号时,也通过其接到单线总线上的第四场效应管m4发送,信号会被主机里的第二非门not2接收并送到主机的第二接收电路111。

42.图6示出了本发明实施例提供的数字控制信号生成电路的一种示例电路结构,图7示出了本发明实施例提供的数字控制信号生成电路的另一种示例电路结构,为了便于说明,仅示出了与本发明实施例相关的部分,详述如下:通用输出电路12包括第一d触发器u1和第二d触发器u2。

43.第一d触发器u1的数据输入端d和第二d触发器u2的数据输入端d共同连接至通用输出电路12的第一数字信号输入端,第一d触发器u1的时钟端和第二d触发器u2的时钟端共同连接至通用输出电路12的时钟端,第一d触发器u1的反相数据锁存输出端/q和第二d触发器u2的数据锁存输出端q共同连接至通用输出电路12的第二数字信号输出端。

44.因为单线通信信号解码后生成的信号需要存储后,才能输出稳定的数字信号,故设置了该第一d触发器u1和第二d触发器u2对第一数字信号进行锁存。

45.上下拉电路13包括第一场效应管m1和第二场效应管m2。第一场效应管为p型金属

‑

氧化物半导体场效应晶体管(positive channel metal oxide semiconductor,pmos),第二场效应管为n型金属

‑

氧化物半导体场效应晶体管(n

‑

metal

‑

oxide

‑

semiconductor,nmos。

46.第一场效应管m1的源极与第一电源vbb连接,第一场效应管m1的栅极和第二场效应管m2的栅极共同连接至上下拉电路13的第二数字信号输入端,第一场效应管m1的漏极和第二场效应管m2的漏极共同连接至上下拉电路13的输出端,第二场效应管m2的源极与电源地连接。

47.电阻组件14包括第一电阻r1。

48.可以理解的是,第一场效应管和第二场效应管共用三种状态。

49.第一种状态描述如下:第一场效应管和第二场效应管都处于截止状态时,如果电阻组件上拉至第一电压,上下拉电路的输出端被电阻组件上拉到第一电压,以使上下拉电路输出高电平的数字控制信号;如果电阻组件下拉至电源地,则上下拉电路的输出端被电阻组件下拉到电源地,以使上下拉电路输出低电平的数字控制信号。

50.具体实施中,第二数字信号为第一状态或者停止第二数字信号输入时,第一场效应管和第二场效应管均处于截止状态。

51.平时没有第二数字信号输入时,第一场效应管和第二场效应管都处于截止状态。如果与数字控制信号生成电路连接的微处理器芯片的复位端口或者上电启动端口平时处在低电平则电阻组件下拉至电源地,则上下拉电路的输出端被电阻组件下拉到电源地,以使上下拉电路输出低电平的数字控制信号。如果与数字控制信号生成电路连接的微处理器芯片的复位端口或者上电启动端口平时处在高电平则电阻组件上拉到第一电压,上下拉电路的输出端被电阻组件上拉到第一电压,以使上下拉电路输出高电平的数字控制信号。

52.第二种状态描述如下:第二数字信号为第二状态,且电阻组件上拉至第一电压时,如图6所示,第一场效应管根据第二状态的第二数字信号截止,第二场效应管根据第二状态的第二数字信号导通至电源地,上下拉电路的输出端下拉至电源地以使上下拉电路输出低电平的数字控制信号。

53.当与数字控制信号生成电路连接的微处理器芯片的复位端口或者上电启动端口

平时处在高电平,在需要复位或上电启动时输入低电平时,控制电路通过第二通信电路发送单线通信信号给第一通信电路,以使第一通信电路输出第一数字信号,通用输出电路将第一数字信号转换为第三状态的第二数字信号,此时电阻组件上拉至第一电压时,第一场效应管根据第二状态的第二数字信号截止,第二场效应管根据第二状态的第二数字信号导通至电源地,上下拉电路的输出端下拉至电源地以使上下拉电路输出低电平的数字控制信号。待微处理器芯片的复位或上电启动完成后,控制电路再通过第二通信电路发送单线通信信号给第一通信电路,以使第一通信电路输出第一数字信号,通用输出电路将第一数字信号转换为第一状态的第二数字信号,使第一场效应管和第二场效应管都处于截止状态,恢复平时状态。

54.第三种状态描述如下:第二数字信号为第三状态,电阻组件下拉至电源地时,如图7所示,第二场效应管根据第三状态的第二数字信号截止,第一场效应管根据第三状态的第二数字信号导通至第一电压,上下拉电路的输出端上拉至第一电压以使上下拉电路输出高电平的数字控制信号。

55.当与数字控制信号生成电路连接的微处理器芯片的复位端口或者上电启动端口平时处在低电平,在需要复位或上电启动时需要输入高电平时,控制电路通过第二通信电路发送单线通信信号给第一通信电路,以使第一通信电路输出第一数字信号,通用输出电路将第一数字信号转换为第三状态的第二数字信号,此时电阻组件下拉至电源地时,第二场效应管根据第三状态的第二数字信号截止,第一场效应管根据第三状态的第二数字信号导通至第一电压,上下拉电路的输出端上拉至第一电压以使上下拉电路输出高电平的数字控制信号。待微处理器芯片的复位或上电启动完成后,控制电路再通过第二通信电路发送单线通信信号给第一通信电路,以使第一通信电路输出第一数字信号,通用输出电路将第一数字信号转换为第一状态的第二数字信号,使第一场效应管和第二场效应管都处于截止状态,恢复平时状态。

56.以下结合工作原理对图6和图7所示的作进一步说明:在图6中,平时没有第二数字信号输入时,第一场效应管m1和第二场效应管m2都处于截止状态,由于第一电阻r1下拉至电源地,上下拉电路的输出端被第一电阻r1上拉到第一电压,以使上下拉电路输出高电平的数字控制信号。与数字控制信号生成电路连接的微处理器芯片的复位端口或者上电启动端口平时处在高电平,在需要复位或上电启动时需要输入低电平时,第一通信电路11接收单线通信信号,并对单线通信信号进行解码以输出第二状态的第一数字信号(第二状态的第一数字信号包括低电平的第三子数字信号和高电平的第四子数字信号);第一d触发器u1的数据输入端d接收低电平的第三子数字信号,第一d触发器u1根据低电平的第三子数字信号从第一d触发器u1的反相数据锁存输出端/q输出高电平的第一子数字信号;第二d触发器u2的数据输入端d接收高电平的第四子数字信号,第二d触发器u2根据高电平的第四子数字信号从第二d触发器u2的数据锁存输出端q输出高电平的第二子数字信号;其中,第一子数字信号和第二子数字信号共同构成第二数字信号。第二场效应管m2根据高电平的第二子数字信号导通至电源地,第一场效应管m1根据高电平的第一子数字信号截止,以使上下拉电路13的输出端下拉至电源地,上下拉电路13的输出端输出低电平的数字控制信号。可以理解的是,待微处理器芯片的复位或上电启动完成后,控制电路再通过第二通信电路发送单线通信信号给第一通信电路,以使第一通信电路输出第

一数字信号,通用输出电路将第一数字信号转换为第一状态的第二数字信号(第一状态的第一数字信号包括低电平的第三子数字信号和低电平的第四子数字信号),第一d触发器u1根据低电平的第三子数字信号从第一d触发器u1的反相数据锁存输出端/q输出高电平的第一子数字信号;第二d触发器u2根据低电平的第四子数字信号从第二d触发器u2的数据锁存输出端q输出低电平的第二子数字信号;第二场效应管m2根据低电平的第二子数字信号截止,第一场效应管m1根据高电平的第一子数字信号截止,以使第一场效应管和第二场效应管都处于截止状态,恢复平时状态。从而在输入单总线通信信号时,实现了低电平脉冲的数字控制信号的输出。

57.在图7中,平时没有第二数字信号输入时,第一场效应管m1和第二场效应管m2都处于截止状态,由于第一电阻r1下拉至电源地,上下拉电路的输出端被第一电阻r1下拉到电源地,以使上下拉电路输出低电平的数字控制信号。与数字控制信号生成电路连接的微处理器芯片平时处在低电平,在需要复位或上电启动时需要输入高电平时,第一通信电路11接收单线通信信号,并对单线通信信号进行解码以输出第三状态的第一数字信号(第三状态的第一数字信号包括高电平的第三子数字信号和低电平的第四子数字信号);第一d触发器u1的数据输入端d接收高电平的第三子数字信号,第一d触发器u1根据高电平的第三子数字信号从第一d触发器u1的反相数据锁存输出端/q输出低电平的第一子数字信号;第二d触发器u2的数据输入端d接收低电平的第四子数字信号,第二d触发器u2根据低电平的第四子数字信号从第二d触发器u2的数据锁存输出端q输出低电平的第二子数字信号;其中,第一子数字信号和第二子数字信号共同构成第二数字信号。第二场效应管m2根据低电平的第二子数字信号截止,第一场效应管m1根据低电平的第一子数字信号导通至第一电压,以使上下拉电路13的输出端上拉至第一电压,上下拉电路13的输出端输出高电平的数字控制信号。可以理解的是,待微处理器芯片的复位或上电启动完成后,控制电路再通过第二通信电路发送单线通信信号给第一通信电路,以使第一通信电路输出第一数字信号,通用输出电路将第一数字信号转换为第一状态的第二数字信号(第一状态的第一数字信号包括低电平的第三子数字信号和低电平的第四子数字信号),第一d触发器u1根据低电平的第三子数字信号从第一d触发器u1的反相数据锁存输出端/q输出高电平的第一子数字信号;第二d触发器u2根据低电平的第四子数字信号从第二d触发器u2的数据锁存输出端q输出低电平的第二子数字信号;第二场效应管m2根据低电平的第二子数字信号截止,第一场效应管m1根据高电平的第一子数字信号截止,以使第一场效应管和第二场效应管都处于截止状态,恢复平时状态。从而在输入单总线通信信号时,实现了高电平脉冲的数字控制信号的输出。

58.本技术实施例还提供一种电子设备,包括上述的数字控制信号生成电路。电子设备可以为耳机系统或者雾化装置或其它配置有数字控制信号生成电路的电子设备,此处不做限定。上述雾化装置包括电子烟。

59.本发明实施例通过通用输出电路将第一数字信号转换为第二数字信号以驱动上下拉电路;上下拉电路根据第二数字信号将上下拉电路的输出端进行上拉或者下拉以改变上下拉电路的输出端的电平状态,或者根据第二数字信号将上下拉电路的输出端既不上拉也不下拉,使上下拉电路的输出端处于高阻态;由于可以改变上下拉电路的输出端的电平状态,对有不同复位电平或上电启动逻辑电平需求的微处理器,仅需开发一个数字控制信号生成电路(一个芯片),即可以达到同时支持不同类型的上述微处理器芯片的目的,降低

了开发成本,同时便于生产和和库存管理。

60.应理解,上述实施例中各步骤的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。

61.以上实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1