半导体结构及其制备方法与流程

本申请属于半导体,具体涉及一种位线结构及其制备方法、半导体结构及其制备方法。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)是一种半导体存储器,主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit)是1还是0。

2、近来,在半导体工业中,为了提高集成度,正在开发40nm以下的动态随机存取存储器。但是,目前开发的40nm以下的动态随机存取存储器,却存在随着集成度越高,信号传输性能下降的问题。

技术实现思路

1、本申请的目的是提供一种位线结构及其制备方法、半导体结构及其制备方法以解决现有技术中高集成度动态随机存取存储器信号传输性能差的问题。

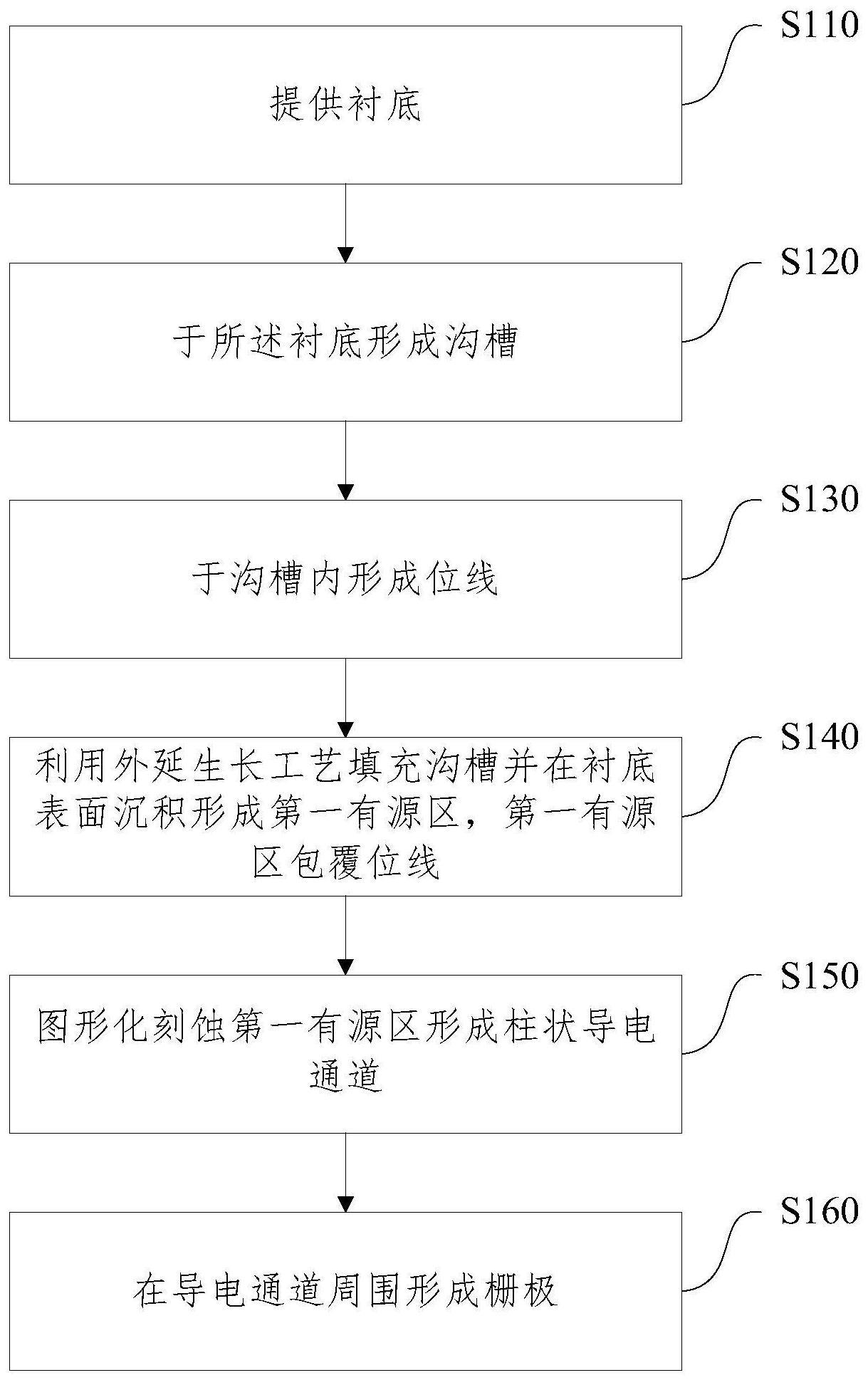

2、根据本申请实施例的第一方面,提供了一种半导体结构的制备方法,该方法可以包括:

3、提供衬底,衬底上形成有纵横交错的隔绝层;

4、于衬底形成沟槽,沟槽穿越隔绝层;

5、于沟槽内形成位线;

6、利用外延生长工艺填充沟槽并在衬底表面沉积形成第一有源区,第一有源区包覆位线;

7、图形化刻蚀第一有源区形成柱状导电通道;

8、在导电通道周围形成栅极。

9、在本申请的一些可选实施例中,于衬底形成沟槽,具体可以为:

10、利用干法刻蚀工艺于衬底形成沟槽。

11、在本申请的一些可选实施例中,于沟槽内形成位线,可以包括:

12、利用沉积工艺于沟槽内依次沉积位线金属层及第一牺牲层,得到充满沟槽的第一填充结构;

13、刻蚀去除第一填充结构靠近沟槽侧壁的区域,以使第一填充结构与沟槽侧壁之间留有间隙;

14、刻蚀去除第一牺牲层,得到位线。

15、在本申请的一些可选实施例中,位线金属层包括层叠的第一阻挡层、金属层及第二阻挡层;

16、利用沉积工艺于沟槽内依次沉积位线金属层及第一牺牲层,得到充满沟槽的第一填充结构,具体可以为:

17、利用沉积工艺于沟槽内部依次沉积第一阻挡层、位线金属、第二阻挡层及第一牺牲层,得到充满沟槽的第一填充结构。

18、在本申请的一些可选实施例中,在利用沉积工艺于沟槽内依次沉积位线金属层及第一牺牲层,得到充满沟槽的第一填充结构之前,于沟槽内形成位线,还可以包括:

19、于沟槽内沉积形成第二牺牲层;

20、在刻蚀去除第一填充结构靠近沟槽侧壁的区域,以使第一填充结构与沟槽侧壁之间留有间隙之后,半导体结构的制备方法还包括:

21、刻蚀去除部分第二牺牲层,第二牺牲层的剩余部分用以支撑位线金属层。

22、在本申请的一些可选实施例中,刻蚀去除部分第二牺牲层,具体可以为:

23、利用湿法刻蚀去除部分第二牺牲层。

24、在本申请的一些可选实施例中,刻蚀去除第一填充结构靠近沟槽侧壁的区域,以使第一填充结构与沟槽侧壁之间留有间隙,具体可以为:

25、利用干法刻蚀去除第一填充结构靠近沟槽侧壁的区域,以使第一填充结构与沟槽侧壁之间留有间隙。

26、在本申请的一些可选实施例中,沉积工艺可以为:

27、化学气相沉积工艺;或

28、原子层沉积工艺。

29、在本申请的一些可选实施例中,导电通道为多个,在导电通道周围形成栅极,可以包括:

30、于柱状导电通道的侧壁沉积形成栅氧介质层;

31、于多个导电通道之间填充导电层,栅氧介质层与导电层构成栅极。

32、在本申请的一些可选实施例中,在导电通道周围形成栅极之后,半导体结构的制备方法,还可以包括:

33、利用外延生长工艺于导电层上沉积形成第二有源区。

34、在本申请的一些可选实施例中,在利用外延生长工艺于导电层上沉积形成第二有源区之后,半导体结构的制备方法,还可以包括:

35、图形化刻蚀第二有源区形成柱状有源区结构。

36、根据本申请实施例的第二方面,提供一种半导体结构,该半导体结构可以包括:

37、衬底,衬底上有纵横交错的隔绝层和沟槽,沟槽穿越沟槽;

38、位线,位线位于沟槽内;

39、第一有源区,第一有源区包覆位线并填充沟槽;

40、多个柱状导电通道,柱状导电通道位于第一有源区;

41、栅极,柱状栅极位于多个柱状导电通道之间。

42、在本申请的一些可选实施例中,还可以包括:

43、第二有源区,第二有源区位于柱状导电通道之上。

44、在本申请的一些可选实施例中,第二有源区可以呈柱状。

45、在本申请的一些可选实施例中,第一有源区与第二有源区的材料可以为:

46、掺杂n型杂质的硅材料;

47、掺杂p型杂质的硅材料;

48、掺杂n型杂质的硅锗材料;或

49、掺杂p型杂质的硅锗材料。

50、本申请的上述技术方案具有如下有益的技术效果:

51、本申请实施例方法通过提供衬底;于衬底形成沟槽;于沟槽内形成位线;利用外延生长工艺填充沟槽并在衬底表面沉积形成第一有源区,第一有源区包覆位线;图形化刻蚀第一有源区形成柱状导电通道;在导电通道周围形成栅极。这样有第一源区就可以包绕在位线的周围,增大了第一有源区与位线的接触面积,减小了第一有源区与位线之间的接触电阻,进而提高电荷传输速度,保证了信号传输性能。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述于所述衬底形成沟槽,具体为:

3.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述于所述沟槽内形成位线,包括:

4.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述位线金属层包括层叠的第一阻挡层、金属层及第二阻挡层;

5.根据权利要求3所述的半导体结构的制备方法,其特征在于,在所述利用沉积工艺于所述沟槽内依次沉积位线金属层及第一牺牲层,得到充满所述沟槽的第一填充结构之前,所述于所述沟槽内形成位线,还包括:

6.根据权利要求5所述的半导体结构的制备方法,其特征在于,所述刻蚀去除部分所述第二牺牲层,具体为:

7.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述刻蚀去除所述第一填充结构靠近所述沟槽侧壁的区域,以使所述第一填充结构与所述沟槽侧壁之间留有间隙,具体为:

8.根据权利要求3所述的半导体结构的制备方法,其特征在于,所述沉积工艺为:

9.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述导电通道为多个,所述在所述导电通道周围形成栅极,包括:

10.根据权利要求1-9任一项所述的半导体结构的制备方法,其特征在于,在所述导电通道周围形成栅极之后,所述半导体结构的制备方法,还包括:

11.根据权利要求10所述的半导体结构的制备方法,其特征在于,在所述利用外延生长工艺于所述导电层上沉积形成第二有源区之后,所述半导体结构的制备方法,还包括:

12.一种半导体结构,其特征在于,包括:

13.根据权利要求12所述的半导体结构,其特征在于,还包括:

14.根据权利要求13所述的半导体结构,其特征在于,所述第二有源区呈柱状。

15.根据权利要求13所述的半导体结构,其特征在于,所述第一有源区与所述第二有源区的材料为:

技术总结

本申请公开了一种半导体结构及其制备方法,属于半导体技术领域,其中,半导体结构的制备方法,包括:提供衬底;于衬底形成沟槽;于沟槽内形成位线;利用外延生长工艺填充沟槽并在衬底表面沉积形成第一有源区,第一有源区包覆位线;图形化刻蚀第一有源区形成柱状导电通道;在导电通道周围形成栅极。该方法制备得到的半导体结构第一源区就可以包绕在位线的周围,增大了第一有源区与位线的接触面积,减小了第一有源区与位线之间的接触电阻,进而提高电荷传输速度,保证了信号传输性能。

技术研发人员:张俊逸,李新,应战

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!