一种漏电补偿结构的锁相环电路的制作方法

1.本发明涉及一种漏电补偿结构的锁相环电路,属于半导体集成电路技术领域。

背景技术:

2.锁相环电路广泛应用于各种芯片中,在射频微波领域、数模混合领域和纯数字领域都是不可缺少的核心电路。锁相环的功能和性能对整颗芯片的成败有着决定性作用。在片上集成系统(soc)或多通道接口电路中,往往需要多个锁相环提供分布式频率源,用于射频本振频谱搬移、系统时钟、音频视频时钟以及模数转换采样时钟等。随着soc的发展,芯片的时钟需求变得越来越复杂,导致了锁相环数量的增加,然而锁相环中需要的环路滤波电容和物理尺寸有关,并不会随着工艺演进而缩小,如何减小锁相环的面积成为业界难题。

3.图1所示为传统锁相环结构,包含鉴频鉴相器、电荷泵、环路滤波器、压控振荡器和分频器,基于环形结构压控振荡器的锁相环其环路滤波器往往占据三分之一甚至二分之一的面积,虽然电容密度高的低压晶体管做环路滤波电容可以有效减小环路滤波电容面积,但是低压晶体管的漏电问题将会严重恶化锁相环的性能,更为严重的是环路滤波电容的漏电随着极板电压、工艺角以及温度变化而变化,这进一步增加了漏电问题处理的难度,虽然随着工艺不断发展,各种结构晶体管的出现一定程度上解决了晶体管关断时漏极和源极间的漏电问题,但是环路滤波电容所面对的栅极漏电问题依然未得到有效解决。因此,业界不得不依然采用电容密度低但漏电小的高压管电容或mom电容作为环路滤波电容。

4.由此可见环路滤波电容的漏电问题极大限制了电容可用类型,特别是限制了高电容密度的低压晶体管电容,解决环路滤波电容的漏电难题,提升环路滤波器的电容密度,是本领域技术人员亟待解决的技术问题。

5.现有技术中如图2所示为专利《带电容漏电补偿的电荷泵电路及锁相环电路》中提出的漏电补偿技术方案,该方案主要缺点有:a.只用固定电流来补偿漏电无法追踪工艺角和温度变化,漏电补偿效果差; b. 当温度、频率发生变化时,其中的节点vc电压会发生变化,进一步恶化漏电补偿效果。

6.如图3所示为专利《动态补偿压控振荡器中v2i管栅极漏电的锁相环》中所提出的漏电补偿技术方案,该方案主要缺点有:a.当vctrl电压(对应图3中v2i栅极电压)变化时,漏电补偿精度难以保证(例如vctrl电压升高,v2i和滤波器电容cz漏电均会因为vctrl电压增加而增加,但补偿电容c1~cn却会因为vctrl电压增加而减小);b.补偿电容c1~cn漏电直接按1:1补偿给v2i和滤波器电容cz,cz通常面积很大,这导致c1~cn面积较大。

7.现有技术《a fully integrated phase-locked loop with leakage current compensation in 65-nm cmos technology》中所提出漏电补偿技术方案,如图4所示,该方案主要缺点有:a.需要双cp来实现补偿,浪费了额外的面积和功耗;b.双cp以及lcc的匹配问题影响补偿精度,难以控制。优点有:采用双cp能够追踪vctrl电压变化,解决vctrl变化恶化补偿精度的问题。

array,用于调节压控振荡器vco的频率;压控振荡器vco的输出端构成锁频与vctrl钳位模块的输出端,压控振荡器vco的电源端连接预设电源电压,压控振荡器vco的接地端接地。

13.作为本发明的一种优选技术方案:所述滤波器模块包括电容cz、电容cp3、电阻r;其中,电容cp3的上极板与电阻r的其中一端相连构成内部节点vres,并作为滤波器模块的输入端;电阻r的另一端对接电容cz的上极板,且该相对接端构成滤波器模块的输出端;电容cz的下极板与电容cp3的下极板相连,且该相连端接地。

14.作为本发明的一种优选技术方案:所述鉴频鉴相器与电荷泵模块包括鉴频鉴相器pfd、第一电流源a1、第二电流源a2、以及第一电流源a1、第二电流源a2分别所对应的开关;其中,第一电流源a1的其中一端连接预设电源电压,第一电流源a1的另一端依次串联第一电流源a1、第二电流源a2分别所对应的开关后,对接第二电流源a2的其中一端,第二电流源a2的另一端接地;鉴频鉴相器pfd的两个输入端构成鉴频鉴相器与电荷泵模块的两个输入端,分别用于接入参考时钟refclk、以及来自分频器分频后的反馈时钟fbclk;鉴频鉴相器pfd的两个输出端分别一一对应连接第一电流源a1、第二电流源a2所对应的开关,用于对各开关的控制,两开关之间相连位置构成鉴频鉴相器与电荷泵模块的输出端。

15.本发明所述一种漏电补偿结构的锁相环电路,采用以上技术方案与现有技术相比,具有以下技术效果:本发明所设计一种漏电补偿结构的锁相环电路,采用全新结构设计,包括鉴频鉴相器与电荷泵模块、滤波器模块、漏电监测补偿模块、逐次逼近补偿电容模块、锁频与vctrl钳位模块、分频器,利用逐次逼近方式,结合配套的环路控制,通过漏电流监测、校准、补偿的方式抵消环路滤波电容的漏电流,解决了传统锁相环电路中环路滤波器的漏电问题,可广泛应用于各类锁相环中,为电容密度高、且存在漏电的低压晶体管类型电容作为环路滤波电容提供了可行性方案,以及可作为减小锁相环面积和成本的有效方法,并且设计漏电补偿方法能够克服工艺角和温度的变化,对漏电失配进行校准,整个电路设计直观,结构简单,易于实现。

附图说明

16.图1为现有传统锁相环示意图;图2为现有一种漏电补偿结构示意图;图3为现有一种v2i漏电补偿电路示意图;图4为现有一种双电荷泵漏电补偿示意图;图5为本发明漏电补偿型锁相环电路结构图;图6 为本发明锁相环电路对应的校准算法流程图。

具体实施方式

17.下面结合说明书附图对本发明的具体实施方式作进一步详细的说明。

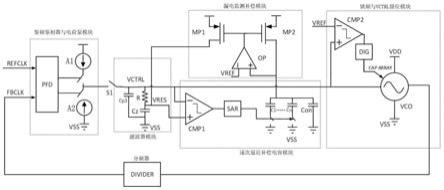

18.本发明设计了一种漏电补偿结构的锁相环电路,如图5所示,包括鉴频鉴相器与电荷泵模块、滤波器模块、漏电监测补偿模块、逐次逼近补偿电容模块、锁频与vctrl钳位模块、分频器。

19.其中,鉴频鉴相器与电荷泵模块的其中一输入端用于接入参考时钟refclk,鉴频

鉴相器与电荷泵模块的输出端经开关s1连接节点vctrl,且节点vctrl分别对接滤波器模块的输入端、逐次逼近补偿电容模块的其中一输入端、锁频与vctrl钳位模块的输入端;滤波器模块的内部节点vres构成滤波器模块的输出端,且节点vres分别对接漏电监测补偿模块的输出端、逐次逼近补偿电容模块的另一输入端;逐次逼近补偿电容模块的输出端对接漏电监测补偿模块的输入端。

20.锁频与vctrl钳位模块的输出端对接分频器的输入端,同时锁频与vctrl钳位模块的输出端用于为目标电路提供调整后的频率和相位;分频器的输出端对接鉴频鉴相器与电荷泵模块的另一输入端,由分频器为鉴频鉴相器与电荷泵模块提供分频后的反馈时钟fbclk。

21.如图5所示,所述鉴频鉴相器与电荷泵模块包括鉴频鉴相器pfd、第一电流源a1、第二电流源a2、以及第一电流源a1、第二电流源a2分别所对应的开关;其中,第一电流源a1的其中一端连接预设电源电压,第一电流源a1的另一端依次串联第一电流源a1、第二电流源a2分别所对应的开关后,对接第二电流源a2的其中一端,第二电流源a2的另一端接地;鉴频鉴相器pfd的两个输入端构成鉴频鉴相器与电荷泵模块的两个输入端,分别用于接入参考时钟refclk、以及来自分频器分频后的反馈时钟fbclk;鉴频鉴相器pfd的两个输出端分别一一对应连接第一电流源a1、第二电流源a2所对应的开关,用于对各开关的控制,两开关之间相连位置构成鉴频鉴相器与电荷泵模块的输出端。

22.如图5所示,所述滤波器模块包括电容cz、电容cp3、电阻r;其中,电容cp3的上极板与电阻r的其中一端相连构成内部节点vres,并作为滤波器模块的输入端;电阻r的另一端对接电容cz的上极板,且该相对接端构成滤波器模块的输出端;电容cz的下极板与电容cp3的下极板相连,且该相连端接地。

23.如图5所示,所述逐次逼近补偿电容模块包括比较器cmp1、逐次逼近逻辑sar、补偿电容阵列;其中,比较器cmp1的负向输入端构成逐次逼近补偿电容模块的其中一输入端,用于对接所述节点vctrl;比较器cmp1的正向输入端构成逐次逼近补偿电容模块的另一输入端,用于对接所述节点vres。

24.补偿电容阵列包括补偿电容con、补偿电容c1至cn、以及与补偿电容c1至cn分别一一对应的开关,其中,补偿电容c1至cn的下极板分别串联对应开关后接地,补偿电容con的下极板直接接地,补偿电容con的上极板与补偿电容c1至cn的上极板彼此相连,且该相连端构成逐次逼近补偿电容模块的输出端;比较器cmp1的输出端对接逐次逼近逻辑sar的输入端,逐次逼近逻辑sar的输出端分别对接补偿电容c1至cn所对应的开关。

25.补偿电容c1至cn和滤波器模块中电容cz的比值为1:n,这样可以把较小电容的漏电通过电流镜放大n倍之后,再注入回电容cz,以节约面积,补偿电容con与补偿电容c1至cn所构成的漏电补偿电容阵列和电容cz以相同的最小单元组成,并且版图画在一起,节约面积,并且从而使得漏电补偿电容可以很好的追踪滤波器模块中电容cz漏电的工艺角和温度变化,以提高漏电补偿精度。

26.所述漏电监测补偿模块如图5所示,包括电流监测p型晶体管mp2、电流补偿p型晶体管mp1、电压钳位运放op;其中,电流监测p型晶体管mp2的漏极连接电压钳位运放op的正向输入端,且该两者之间相连位置构成漏电监测补偿模块的输入端;电压钳位运放op的负向输入端用于接入预设参考电压vref;电压钳位运放op的输出端、电流监测p型晶体管mp2

的栅极、电流补偿p型晶体管mp1的栅极三者相连,电流补偿p型晶体管mp1的漏极构成漏电监测补偿模块的输出端,电流监测p型晶体管mp2的源极、电流补偿p型晶体管mp1的源极分别接入预设电源电压。

27.锁频与vctrl钳位模块如图5所示,包括钳位比较器cmp2、数字逻辑dig电路、压控振荡器vco;其中,钳位比较器cmp2的负向输入端用于接入预设参考电压vref,钳位比较器cmp2的正向输入端与压控振荡器vco的电压控制频率端相连,且该相连位置构成锁频与vctrl钳位模块的输入端;钳位比较器cmp2的输出端对接数字逻辑dig电路的输入端,数字逻辑dig电路的输出端对接压控振荡器vco中的负载电容阵列cap array,用于调节压控振荡器vco的频率;压控振荡器vco的输出端构成锁频与vctrl钳位模块的输出端,压控振荡器vco的电源端连接预设电源电压,压控振荡器vco的接地端接地。

28.环路滤波电容漏电问题严重恶化锁相环性,漏电问题难以处理主要表现在两方面,第一:受限于芯片制造工艺,业界被迫只能采用电容密度低但漏电很小的电容来做环路滤波电容,这会造成面积利用率低;第二:由于锁相环锁定后压控振荡器的控制电压值vctrl会随工艺和环境变化而变化,并且电容漏电与极板电压之间呈现非线性关系,导致影响漏电的变量很多,难以处理。

29.本发明设计漏电补偿结构的锁相环电路主要原理为:如图5所示,首先应用开关s1断开鉴频鉴相器和电荷泵与节点vctrl的连接,即将节点vctrl的电压偏置在参考电压vref上,打开锁频与vctrl钳位模块,通过调节cap array进行压控振荡器vco的频率调节,同时监测滤波器模块中电阻r两端的压降(vctrl-vres),环路滤波电容cz的漏电流直接反映在电阻压降(vctrl-vref)上,比较器cmp1比较vctrl电压和vres电压、并通过逐次逼近逻辑调节补偿电容阵列,漏电监测补偿模块监测补偿电容阵列电流并注入回节点vres,以补偿电容cz的漏电,通过逐次逼近逻辑调节补偿电容阵列电容大小,当节点vctrl电压和节点vres电压之间差值最小时,即实现最优漏电补偿。电容阵列校准完成后,关闭开关s1将鉴频鉴相器与电荷泵接入锁相环路,进行相位锁定,同时cmp2保持开启,通过监测节点vctrl的电压并实时动态调节压控振荡器vco的cap array,让vctrl始终处于参考电压vref附近,从而避免滤波器中电容cz极板电压随工艺和温度变化的不确定性,以提高漏电补偿电流的准确性。

30.上述电容阵列校准完成后,关闭开关s1,鉴频鉴相器和电荷泵接入环路进行相位锁定。同时,vctrl钳位比较器cmp2始终监测vctrl节点电压,并动态调节压控振荡器的电容阵列cap array,从而实现锁定后vctrl电压始终约等于vref电压,通过和钳位运放op的配合,不仅可以提高电流镜mp1和mp2之间的匹配度,而且可以减小vctrl节点电压变化而引入的电容cz漏电流变化,通过这种方式进一步提升了漏电流补偿精度,解决了漏电和电容极板电压之间非线性关系而导致的漏电补偿精度难题。

31.本发明结构通过漏电流补偿电容阵列(c1至cn)复制滤波器模块中电容cz的漏电,并且由逐次逼近逻辑调节校准该电容阵列,实现了电容cz漏电流的补偿,补偿电容阵列(c1至cn)和滤波器电容的比值为1:n;电流监测补偿模块中的mp1和mp2的镜像比例为n:1,并且补偿电容阵列中电容和环路滤波电容cz均由相同的最小电容单元模块组合而成,并进行版图的匹配,从而补偿电容阵列能够和环路滤波电容保持相同的工艺角偏移和温度系数,从而提高了漏电补偿的抗温度和工艺角变化能力,这解决了上述第一方面的问题。通过钳位

比较器cmp2的实时动态调节vco的负载电容cap array,让vctrl电压始终约等于vref电压,减小了电容漏电随极板电压的波动,从而降低了电容漏电流的非线性影响因素和电流监测补偿模块电流镜镜像的非线性影响因素,提高了漏电流补偿的精度,这解决了上述第二方面的问题。具体频率校准、漏电校准和相位锁定三个模式的算法控制如图6。注意到在锁相环滤波器模块中电容cz最大,并且占据主要面积,所以本发明方案针对电容cz进行漏电补偿,通过对cz漏电补偿让电容密度高但存在较大漏电流的电容在锁相环中的使用提供有效方案,可以减小锁相环面积。

32.上述技术方案所设计一种漏电补偿结构的锁相环电路,采用全新结构设计,包括鉴频鉴相器与电荷泵模块、滤波器模块、漏电监测补偿模块、逐次逼近补偿电容模块、锁频与vctrl钳位模块、分频器,利用逐次逼近方式,结合配套的环路控制,通过漏电流监测、校准、补偿的方式抵消环路滤波电容的漏电流,解决了传统锁相环电路中环路滤波器的漏电问题,可广泛应用于各类锁相环中,为电容密度高、且存在漏电的低压晶体管类型电容作为环路滤波电容提供了可行性方案,以及可作为减小锁相环面积和成本的有效方法,并且设计漏电补偿方法能够克服工艺角和温度的变化,对漏电失配进行校准,整个电路设计直观,结构简单,易于实现。

33.下面结合附图对本发明的实施方式作了详细说明,但是本发明并不限于上述实施方式,在本领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下做出各种变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1