时间交错式模拟数字转换器的制作方法

本发明是关于时间交错式模拟数字转换器(time interleaved analog-to-digital converter,tiadc),尤其是关于时间交错式模拟数字转换器的取样时间偏斜(sampling timing skew)所导致的时间偏斜音调(timing skew tone)的抑制。

背景技术:

1、时间交错式adc包含多个子模拟数字转换器(analog-to-digital converter,以下简称adc),每个子adc根据相同频率但不同相位的取样时钟对输入信号进行取样,并且轮流产生各自的数字输出码,作为时间交错式adc的输出。举例来说,当时间交错式adc包含四个子adc(adc1、adc2、adc3及adc4),且依照adc1→adc2→adc3→adc4→adc1→adc2→…的顺序依序取样输入信号,则adc1的取样时钟与adc2的取样时钟的相位差为90度、adc2的取样时钟与adc3的取样时钟的相位差为90度、adc3的取样时钟与adc4的取样时钟的相位差为90度,以及adc4的取样时钟与adc1的取样时钟的相位差为90度。如果时间交错式adc的工作时钟的频率是fs(即时间交错式adc每1/fs秒输出一个数字输出码),则adc1、adc2、adc3及adc4的取样时钟的频率是fs/4。

2、由于走线长度、元件不匹配等因素,子模拟数字转换器adc2、adc3及adc4的取样时钟与子模拟数字转换器adc1的取样时钟的相位差不会正好分别是90度、180度、270度,而是90+x度、180+y度、270+z度(x、y、z为有理数)。文献「behzad razavi.designconsiderations for interleaved adcs.ieee journal of solid-state circuits,vol.48,no.8,august 2013」提供一种求得x、y及z的数值的方法。

3、习知的一种校正时间交错式adc的方法使用三个滤波器分别根据x、y及z的数值来分别调整子模拟数字转换器adc2、adc3及adc4的数字输出码,以补偿或修正因为相位误差(即x、y、z)所造成的错误。此方法的缺点之一是收敛速度慢。此方法的另一缺点是,校正后的时间交错式adc在频域上常存在残余的时间偏斜音调、增益音调(gain tone)及偏置音调(offset tone),其中最难处理的是残余的时间偏斜音调,其成因乃残余的时间偏斜音调,代表校正后的取样时钟的相位差仍非90度、180度、270度,例如等效于校正后的相位差分别是90+x1度、180+y1度、270+z1度,x1、y1、z1为残余值。非期望的时间偏斜音调的发生是因为残余值x1、y1、z1是非零的定值,而非期望的时间偏斜音调会造成时间交错式adc的品质下降,甚至导致其他电路发生错误。

技术实现思路

1、鉴于先前技术的不足,本发明的目的之一在于提供一种时间交错式模拟数字转换器,以改善先前技术的不足。

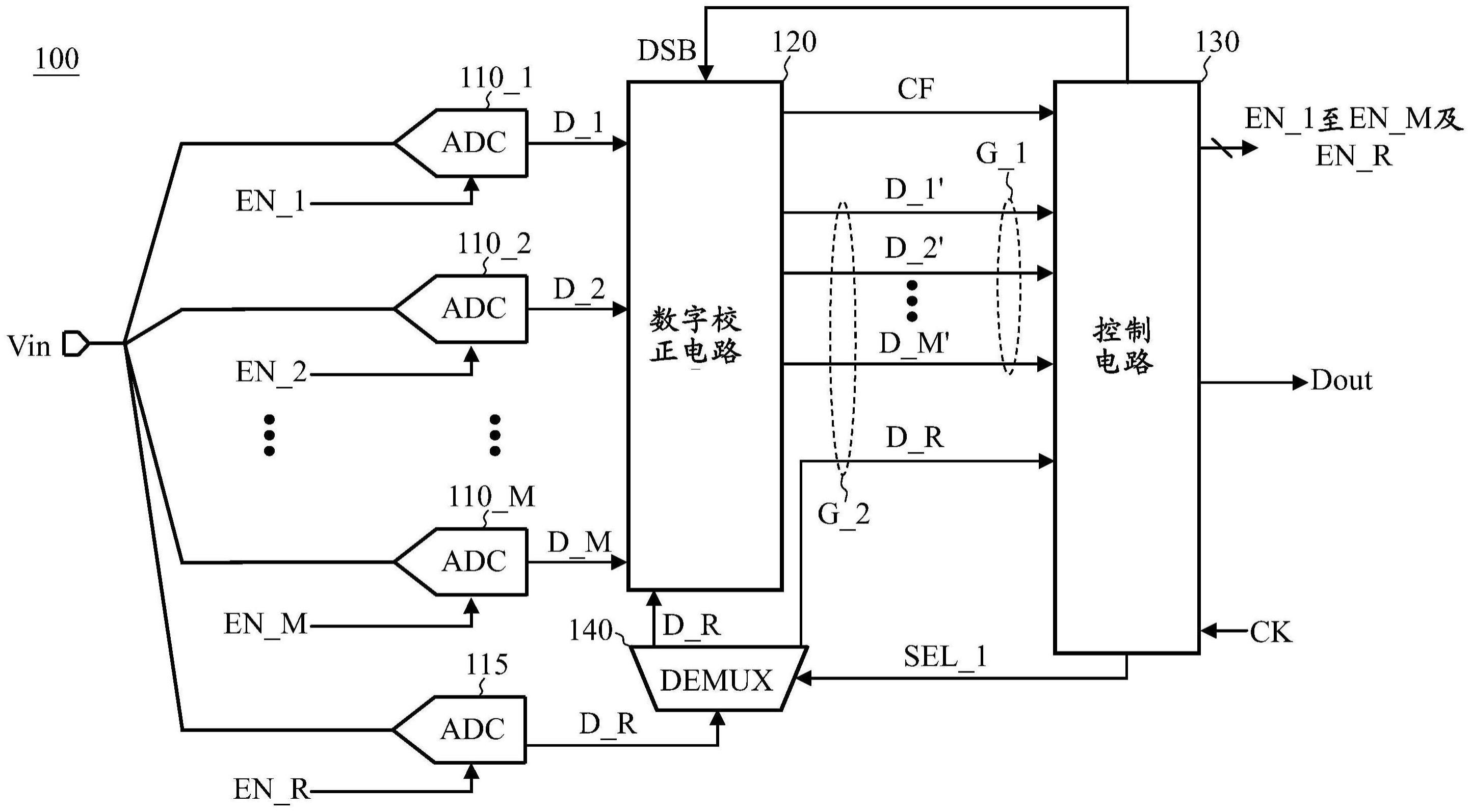

2、本发明的一个实施例提供一种时间交错式模拟数字转换器,操作于第一模式或第二模式,包含:m个模拟数字转换器、参考模拟数字转换器、数字校正电路以及控制电路。m个模拟数字转换器根据m个致能信号取样以输入信号以产生m个数字输出码,m为大于1的整数。参考模拟数字转换器根据参考致能信号取样该输入信号以产生参考数字输出码。数字校正电路用来校正该m个数字输出码,以产生m个校正数字输出码。控制电路用来根据时钟产生该m个致能信号以及该参考致能信号。于该第一模式中,该控制电路轮流输出该m个校正数字输出码,但不输出该参考数字输出码。于该第二模式中,该控制电路随机输出该m个校正数字输出码及该参考数字输出码。

3、本发明的另一个实施例提供一种时间交错式模拟数字转换器,操作于第一模式或第二模式,用来将输入信号转换成数字输出信号,包含:第一模拟数字转换器、第二模拟数字转换器、第三模拟数字转换器、第四模拟数字转换器、参考模拟数字转换器、数字校正电路以及控制电路。第一模拟数字转换器接收该输入信号,并且根据第一致能信号取样该输入信号以产生第一数字输出码。第二模拟数字转换器接收该输入信号,并且根据第二致能信号取样该输入信号以产生第二数字输出码。第三模拟数字转换器接收该输入信号,并且根据第三致能信号取样该输入信号以产生第三数字输出码。第四模拟数字转换器接收该输入信号,并且根据第四致能信号取样该输入信号以产生第四数字输出码。参考模拟数字转换器接收该输入信号,并且根据参考致能信号取样该输入信号以产生参考数字输出码。数字校正电路用来校正该第一数字输出码、该第二数字输出码、该第三数字输出码及该第四数字输出码,以分别产生第一校正数字输出码、第二校正数字输出码、第三校正数字输出码及第四校正数字输出码。控制电路用来根据时钟产生该第一致能信号、该第二致能信号、该第三致能信号、该第四致能信号以及该参考致能信号。于该第一模式中,该数字输出信号选自包含该第一校正数字输出码、该第二校正数字输出码、该第三校正数字输出码及该第四校正数字输出码的第一数字输出码群组。于该第二模式中,该数字输出信号选自包含该第一校正数字输出码、该第二校正数字输出码、该第三校正数字输出码、该第四校正数字输出码及该参考数字输出码的第二数字输出码群组。

4、本发明的时间交错式adc能够抑制时间偏斜音调、增益音调及偏置音调,并且可以加快收敛速度。

5、有关本发明的特征、实作与功效,兹配合图式作实施例详细说明如下。

技术特征:

1.一种时间交错式模拟数字转换器,操作于第一模式或第二模式,包含:

2.如权利要求1所述的时间交错式模拟数字转换器,其中,在该第一模式中,该m个致能信号的周期是该时钟的周期的m倍,而该参考致能信号的周期是该时钟的周期的m+1倍;在该第二模式中,该m个致能信号及该参考致能信号的周期非固定。

3.如权利要求2所述的时间交错式模拟数字转换器,其中,于该第二模式中,该控制电路是从该m个模拟数字转换器及该参考模拟数字转换器的其中二者中随机选择其中之一。

4.如权利要求2所述的时间交错式模拟数字转换器,其中,该时间交错式模拟数字转换器输出数字输出信号,该控制电路包含:

5.如权利要求2所述的时间交错式模拟数字转换器,其中,当该时间交错式模拟数字转换器操作于该第一模式的时间超过阈值时,该控制电路控制该时间交错式模拟数字转换器操作于该第二模式。

6.如权利要求2所述的时间交错式模拟数字转换器,其中,当该数字校正电路指示该m个校正数字输出码的至少其中一者的错误量小于阈值时,该控制电路控制该时间交错式模拟数字转换器操作于该第二模式。

7.如权利要求2所述的时间交错式模拟数字转换器,其中,该时间交错式模拟数字转换器输出数字输出信号,该控制电路对该数字输出信号执行快速傅立叶变换,并且当快速傅立叶变换的结果大于阈值时,该控制电路控制该时间交错式模拟数字转换器操作于该第二模式。

8.如权利要求2所述的时间交错式模拟数字转换器,其中,当该控制电路侦测到该时间交错式模拟数字转换器的操作电压及环境温度的至少其中一者发生变化时,该控制电路控制该时间交错式模拟数字转换器操作于该第一模式。

9.一种时间交错式模拟数字转换器,操作于第一模式或第二模式,用来将输入信号转换成数字输出信号,包含:

10.如权利要求9所述的时间交错式模拟数字转换器,其中,在该第一模式中,该第一致能信号、该第二致能信号、该第三致能信号及该第四致能信号的周期是该时钟的周期的四倍,而该参考致能信号的周期是该时钟的周期的五倍;在该第二模式中,该第一致能信号、该第二致能信号、该第三致能信号、该第四致能信号及该参考致能信号的周期非固定。

技术总结

本公开涉及时间交错式模拟数字转换器。一种时间交错式模拟数字转换器,操作于第一模式或第二模式,并且包含M个模拟数字转换器、参考模拟数字转换器、数字校正电路及控制电路,M为大于1的整数。M个模拟数字转换器根据M个致能信号取样以输入信号以产生M个数字输出码。参考模拟数字转换器根据参考致能信号取样该输入信号以产生参考数字输出码。数字校正电路校正该M个数字输出码,以产生M个校正数字输出码。控制电路根据时钟产生该M个致能信号以及该参考致能信号。

技术研发人员:黄诗雄,杨军,陈昱璋

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!