一种高速高稳态电平位移电路的制作方法

1.本发明涉及模拟集成电路技术领域,特别涉及一种高速高稳态电平位移电路。

背景技术:

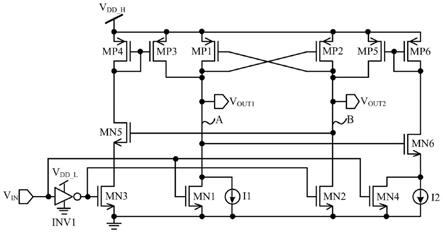

2.在高压多电源供电芯片中,电平位移(level shift)电路用于实现驱动模块中控制信号在不同电源域之间的转换,其通过将低压逻辑控制信号转换为高压驱动控制信号后,最终实现对高压功率管的开启及关断控制。level shift连接低压控制及高压驱动输出电路,为高压多电源供电芯片中关键模块,其决定了整个芯片性能和可靠性上限。传统level shift受其设计架构固有缺陷影响,无法在转换速度、静态电流和工作稳定性等多方面达到良好的综合平衡,仅可针对某一特定性能指标进行优化,普遍具有初始状态不定、转换延时大、静态电流高、电路结构复杂和适用电压域受限等问题。

3.传统电平位移电路架构如图1所示,其采用可加速控制信号转换的交叉耦合形式。v

in

为低压逻辑控制信号,v

dd_l

为低电压域模块供电电源,v

dd_h

为高电压域模块供电电源。v

in

利用反向器inv11在mos管mn11和mn12的栅端产生一对互补的低压逻辑控制信号。

4.传统交叉耦合架构电平位移电路工作过程为:当v

in

从gnd上升至与v

dd_l

相等时,mn12开启且mn11关断,此时mn12、mp11分别对b、a两点寄生电容进行放电和充电操作,此过程持续至v

out2

=gnd且v

out1

=v

dd_h

,此时mp12被关断且mp11处于深度线性区。当v

in

从v

dd_l

下降至与gnd相等时,则电路中器件工作状态与以上描述相反,最终mp11被关断且mp12处于深度线性区。

5.传统交叉耦合架构电平位移电路的缺陷是上拉管(mp11与mp12)和下拉管(mn11和mn12)之间存在竞争。具体表现为当v

dd_l

不断降低至一个nmos管开启阈值电压时,mn11和mn12管下拉能力变弱,此时受mp11和mp12上拉管影响,输出将无法依据输入状态进行正确翻转。虽可通过增大下拉管尺寸、增大上拉pmos管阈值电压绝对值等方式对传统交叉耦合架构电平位移电路进行一定程度优化,但会导致增加电路延时、静态电流和设计工艺复杂度等问题。

技术实现要素:

6.本发明的目的在于提供一种高速高稳态电平位移电路,以解决背景技术中的问题。

7.为解决上述技术问题,本发明提供了一种高速高稳态电平位移电路,包括nmos管mn1~mn6、pmos管mp1~mp6、电流源i1~i2以及反向器inv1;其中,

8.nmos管mn1的漏端接pmos管mp1的漏端,nmos管mn1的栅端接低压逻辑控制信号v

in

;nmos管mn2的漏端接pmos管mp2的漏端,nmos管mn2的栅端接反相器inv1的输出端;nmos管mn3的漏端接nmos管mn5的源端,nmos管mn3的栅端接反相器inv1的输出端;nmos管mn4的漏端接电流源i2的上端,栅端接低压逻辑控制信号v

in

;

9.nmos管mn5的漏端接pmos管mp4的漏端,nmos管mn5的栅端接nmos管mn2的漏端,

nmos管mn5的源端接nmos管mn3的漏端;

10.nmos管mn6的漏端接pmos管mp6的漏端,nmos管mn6的栅端接nmos管mn1的漏端,nmos管mn6的源端接nmos管mn4的漏端;

11.pmos管mp1的漏端接nmos管mn1的漏端,pmos管mp1的栅端接pmos管mp2的漏端;pmos管mp2的漏端接nmos管mn2的漏端,pmos管mp2的栅端接pmos管mp1的漏端;pmos管mp3的漏端接pmos管mp1的漏端,pmos管mp3的栅端接pmos管mp4的栅端;pmos管mp4的漏端接nmos管mn5的漏端,pmos管mp4的栅端接pmos管mp3的栅端;pmos管mp5的漏端接nmos管mn2的漏端,pmos管mp5的栅端接pmos管mp6的栅端;pmos管mp6的漏端接nmos管mn6的漏端,pmos管mp6的栅端接pmos管mp5的栅端;

12.电流源i1的上端接nmos管mn1的漏端,下端接低gnd;电流源i2的上端接nmos管mn4的漏端,下端接地gnd;反相器inv1的输入端接低压逻辑控制信号v

in

,输出端接nmos管mn3的栅端。

13.可选的,所述nmos管mn1~mn4的源端均接地gnd。

14.可选的,所述pmos管mp1~mp6的源端均接高电压域模块供电电源v

dd_h

。

15.可选的,所述pmos管mp4的漏端与其自身栅端互连,所述pmos管mp6的漏端与其自身栅端互连。

16.在本发明提供的高速高稳态电平位移电路,具有以下有益效果:

17.(1)电路初始状态明确,且电平转换过程中可保持高稳态,具有高可靠特性;

18.(2)电路响应速度快,所用瞬态增强结构可减小传输延时,加速信号转换;

19.(3)电路具有低功耗特性,所用瞬态增强结构在电平位移电路稳态时不工作,可减小静态电流。

附图说明

20.图1是传统交叉耦合电平位移电路架构示意图;

21.图2是本发明提供的高速高稳态电平位移电路架构示意图。

具体实施方式

22.以下结合附图和具体实施例对本发明提出的一种高速高稳态电平位移电路作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

23.本发明提供了一种高速高稳态电平位移电路,其结构如图2所示,包括nmos管mn1~mn6、pmos管mp1~mp6、电流源i1~i2以及反向器inv1;其中,nmos管mn1的漏端接pmos管mp1的漏端,nmos管mn1的栅端接低压逻辑控制信号v

in

;nmos管mn2的漏端接pmos管mp2的漏端,nmos管mn2的栅端接反相器inv1的输出端;nmos管mn3的漏端接nmos管mn5的源端,nmos管mn3的栅端接反相器inv1的输出端;nmos管mn4的漏端接电流源i2的上端,栅端接低压逻辑控制信号v

in

;nmos管mn5的漏端接pmos管mp4的漏端,nmos管mn5的栅端接nmos管mn2的漏端,nmos管mn5的源端接nmos管mn3的漏端;nmos管mn6的漏端接pmos管mp6的漏端,nmos管mn6的栅端接nmos管mn1的漏端,nmos管mn6的源端接nmos管mn4的漏端;所述nmos管mn1~

mn4的源端均接地gnd。

24.pmos管mp1的漏端接nmos管mn1的漏端,pmos管mp1的栅端接pmos管mp2的漏端;pmos管mp2的漏端接nmos管mn2的漏端,pmos管mp2的栅端接pmos管mp1的漏端;pmos管mp3的漏端接pmos管mp1的漏端,pmos管mp3的栅端接pmos管mp4的栅端;pmos管mp4的漏端接nmos管mn5的漏端,pmos管mp4的栅端接pmos管mp3的栅端;pmos管mp5的漏端接nmos管mn2的漏端,pmos管mp5的栅端接pmos管mp6的栅端;pmos管mp6的漏端接nmos管mn6的漏端,pmos管mp6的栅端接pmos管mp5的栅端;所述pmos管mp1~mp6的源端均接高电压域模块供电电源v

dd_h

。所述pmos管mp4的漏端与其自身栅端互连,所述pmos管mp6的漏端与其自身栅端互连。

25.电流源i1的上端接nmos管mn1的漏端,下端接低gnd;电流源i2的上端接nmos管mn4的漏端,下端接地gnd;反相器inv1的输入端接低压逻辑控制信号v

in

,输出端接nmos管mn3的栅端。

26.pmos管mp3、mp4和pmos管mp5、mp6为两组瞬态增强结构,利用其可实现当输入低压逻辑控制信号v

in

跳变时输出电平的快速转换。pmos管mp3、mp4、mp5和mp6在电路稳态时退出工作,降低了电路静态电流。

27.pmos管mp1和mp2采用正反馈连接形式,可加速输出电平的转换速度,稳定的将处于gnd~v

dd_l

电源域的低压逻辑控制信号转换为gnd~v

dd_h

电源域的高压驱动信号。

28.电流源i1和i2用于在上电过程中确定电路初始状态,防止因低压逻辑控制信号v

in

相对于低电压域模块供电电源v

dd_l

状态不确定,导致电路中其余mos管状态无法确定,最终电平位移电路输出也状态不定。假设电路初始不定态为v

out1

=v

dd_h

,v

out2

=gnd。则此时nmos管mn6开启,电流源i2通过pmos管mp5和mp6构成的电流镜对b点进行充电使v

out2

上升,电流源i1直接对a点放电使v

out1

下降。最终电路初始状态被固定为v

out1

=gnd,v

out2

=v

dd_h

,增加了电路应用时的可靠性。

[0029]vin

从gnd升至v

dd_l

时电路状态转换过程:

[0030]vin

=gnd时,v

out1

=v

dd_h

,v

out2

=gnd。此时电路静态电流由以下三条之路产生,1、处于深线性区的pmos管mp1和电流源i1;2、处于深线性区的nmos管mn2和经电流镜mp5、mp6镜像所得电流i2;3、流过nmos管mn6的电流i2。则v

in

=gnd时,电路总静态电流i

total

为:

[0031]itotal

=i1+2i2ꢀꢀ

(1)

[0032]vin

从gnd升至v

dd_l

时电路状态转换过程可按v

dd_h-|v

th(mp2)

|≤v

out1

《v

dd_h

、v

ds(mn4)

+v

gs(mn6)

≤v

out1

《v

dd_h-|v

th(mp2)

|和v

out1

《v

ds(mn4)

+v

gs(mn6)

分为三个阶段;其中v

th(mp2)

为pmos管mp2的阈值电压、v

ds(mn4)

为nmos管mn4饱和过驱动电压、v

gs(mn6)

为nmos管mn6开启时栅源压差。

[0033]

当v

dd_h-|v

th(mp2)

|≤v

out1

《v

dd_h

时,nmos管mn6保持开启状态,pmos管mp2保持关闭状态,nmos管mn1、mn4逐渐开启,nmos管mn2、mn3逐渐关闭。此时v

out2

的上拉电流i

out2_up

和v

out1

的下拉电流i

out1_down

分别为:

[0034]iout2_up

=i

mn4

+i2ꢀꢀ

(2)

[0035]imn4

为nmos管mn4开启时电流。

[0036]iout1_down

=i

mn1

+i1ꢀꢀ

(3)

[0037]imn1

为nmos管mn1开启时电流。

[0038]

当v

ds(mn4)

+v

gs(mn6)

≤v

out1

《v

dd_h-|v

th(mp2)

|时,nmos管mn6保持开启状态,pmos管mp2开启,nmos管mn1、mn4逐渐开启,nmos管mn2、mn3逐渐关闭。pmos管mp2开启后,受益于pmos管

mp1和mp2采用的正反馈连接形式电路对b点上拉能力增加,v

out2

的加速上升可使pmos管mp1被快速关闭,从而降低a点处上拉电流,防止因pmos管mp1管上拉能力强于i

out1_down

而导致v

out1

电位无法降低,出现亚稳态情况。此时v

out2

的上拉电流i

out2_up

和v

out1

的下拉电流i

out1_down

分别为:

[0039]iout2_up

=i

mn4

+i2+i

mp2

ꢀꢀ

(4)

[0040]imp2

为pmos管mp2开启时电流。

[0041]iout1_down

=i

mn1

+i1ꢀꢀ

(5)

[0042]

当v

out1

《v

ds(mn4)

+v

gs(mn6)

时,nmos管mn6关闭,pmos管mp2处于深线性区,nmos管mn1、mn4处于深线性区,nmos管mn2、mn3逐渐关闭。最终v

out2

=v

dd_h

,v

out1

=gnd。此时v

out2

的上拉电流i

out2_up

和v

out1

的下拉电流i

out1_down

分别为:

[0043]iout2_up

=i

mp2

ꢀꢀ

(6)

[0044]iout1_down

=i

mn1

+i1ꢀꢀ

(7)

[0045]

由于瞬态增强结构中mp5镜像mp6的电流,则当v

ds(mn4)

+v

gs(mn6)

≤v

out1

《v

dd_h

时节点b处始终存在两股上拉电流,实现了瞬态增强机制,最终使v

out2

加速上升且v

out1

加速下降。

[0046]vin

从v

dd_l

降至gnd时电路状态转换过程:

[0047]vin

=v

dd_l

时,v

out1

=gnd,v

out2

=v

dd_h

。此时不存在电源与地之间的电流通路,电路总静态电流i

total

为:

[0048]itotal

=0

ꢀꢀ

(8)

[0049]vin

从v

dd

_

l

降至gnd时电路状态转换过程可按v

dd

_

h-|v

th(mp1)

|≤v

out2

《v

dd

_h、v

ds(mn3)

+v

gs(mn5)

≤v

out2

《v

dd

_

h-|v

th(mp1)

|和v

out2

《v

ds(mn3)

+v

gs(mn5)

分为三个阶段。其中v

th(mp1)

为pmos管mp1的阈值电压、v

ds(mn3)

为nmos管mn3的饱和过驱动电压、v

gs(mn5)

为nmos管mn5开启时栅源压差。

[0050]

当v

dd

_

h-|v

th(mp1)

|≤v

out2

《v

dd

_h时,nmos管mn5保持开启状态,pmos管mp1保持关闭状态,nmos管mn1、mn4逐渐关闭,nmos管mn2、mn3逐渐开启。此时v

out1

的上拉电流i

out1_up

和v

out2

的下拉电流i

out2_down

分别为:

[0051]iout1_up

=i

mp3

ꢀꢀ

(9)

[0052]imp3

为pmos管mp3开启时电流。

[0053]iout2_down

=i

mn2

ꢀꢀ

(10)

[0054]imn2

为nmos管mn2开启时电流。

[0055]

当v

ds(mn3)

+v

gs(mn5)

≤v

out2

《v

dd

_

h-|v

th(mp1)

|时,nmos管mn5保持开启状态,pmos管mp1开启,nmos管mn1、mn4逐渐关闭,nmos管mn2、mn3逐渐开启。pmos管mp1开启后,受益于pmos管mp1和mp2采用的正反馈连接形式电路对a点上拉能力增加,v

out1

的加速上升可使pmos管mp2被快速关闭,从而降低b点处上拉电流,防止因pmos管mp2管上拉能力强于i

out2_down

而导致v

out2

电位无法降低,出现亚稳态情况。此时v

out1

的上拉电流i

out1_up

和v

out2

的下拉电流i

out2_down

分别为:

[0056]iout1_up

=i

mp3

+i

mp1

ꢀꢀ

(11)

[0057]imp1

为pmos管mp1开启时电流。

[0058]iout2_down

=i

mn2

ꢀꢀ

(12)

[0059]

当v

out2

《v

ds(mn3)

+v

gs(mn5)

时,nmos管mn5关闭,pmos管mp1处于深线性区,nmos管mn1、

mn4逐渐关闭,nmos管mn2、mn3处于深线性区。最终v

out1

=v

dd_h

,v

out2

=gnd。此时v

out1

的上拉电流i

out1_up

和v

out2

的下拉电流i

out2_down

分别为:

[0060]iout1_up

=i

mp1

ꢀꢀ

(13)

[0061]iout2_down

=i

mn2

ꢀꢀ

(14)

[0062]

由于瞬态增强结构中pmos管mp3镜像mp4的电流,则当v

ds(mn3)

+v

gs(mn5)

≤v

out2

《v

dd_h

时节点a处始终存在两股上拉电流,实现了瞬态增强机制,最终使v

out1

加速上升且v

out2

加速下降。

[0063]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1