高速电路以及制造低干扰差分走线的方法与流程

1.本发明涉及一种高速差分走线。更具体地,本发明涉及一种具有返回路径的高速差分走线,以减少在多频带中的干扰辐射。

背景技术:

2.高速差分信号走线广泛用于服务器/存储产品的设计中。许多服务器/存储产品包括一个机箱,用于安装电子装置的不同印刷电路板。印刷电路板包括各种信号走线,以提供信号至板上的装置。对于特定的信号线,信号走线通常以差分走线对的形式排列。在印刷电路板上的这种差分走线具有不同的模式,包括差模(differential mode)、共模(common mode)、以及在传输期间于差分信号之间的模式转换。由于越来越多的产品应用包括在不同电路板之间或在电路板与电缆之间的差分信号转变,因此,共模能量将通过连接器在这些转变期间辐射到机箱中的孔。共模能量在两个差分走线上产生一个信号。因此,共模能量会产生噪声以干扰在走线上信号传输,并引发干扰问题。

3.图1表示在印刷电路板12上的现有返回电流电路走线10的一示例。印刷电路板12附接到一接地平面层14。电流电路走线10包括在印刷电路板12的一表面20上的两条差分走线22和24。接地平面层14接触印刷电路板12的相对表面。箭头30表示差分走线22中的插入电流。箭头32表示差分走线24中的感应电流。箭头34表示在差分走线22下方的接地平面层14中所产生的返回电流。如图1所示,共模能量通过箭头30所表示的插入电流减去耦合项(coupling term)所产生。

4.图2是来自服务器机箱中的信号的电子信号干扰图。服务器机箱包括具有类似于图1所示的差分走线的多个板块。服务器机箱有数个电路板。不同电路板之间的转变允许共模能量通过机箱中的孔辐射。线50是一fcc class a数字装置中允许的走线噪声,线60是一fcc class a-av装置中允许的系统噪声。可以看出,对于更现代的class a-av装置,允许的噪声程度。尖波80代表在大约8ghz的频率下不可接受的噪声辐射,其是由诸如服务器机箱之类的示例系统所产生。

5.为了减少由共模能量引起的辐射,需要减少共模能量的走线设计,同时保持差分信号的总能量恒定。由于高速走线可用于在不同频率下传输数据,因此还需要减少在感兴趣的不同传输频率上的干扰和噪声。

技术实现要素:

6.术语实施例和类似术语,例如实现、配置、方面、示例和选项,旨在广泛地指代本发明和以下权利要求的所有主题。包含这些术语的陈述应被理解为不限制本文描述的标的或限制以下权利要求的含义或范围。此处所涵盖的本发明的实施例由以下权利要求而不是本发明内容所限定。本发明内容是本发明的各个方面的上位概述并且介绍了在以下实施方式部分中进一步描述的一些概念。本发明内容并非旨在确定所请求的标的的关键或基本特征。本发明内容也非旨在单独用于确定所请求的标的范围。应该通过参考本发明的整个说

明书的适当部分、任何或所有附图、以及每个权利要求来理解本标的。

7.根据本发明的某些方面,一高速电路包括一印刷电路板、一接地平面层、一对的一第一差分走线以及一第二差分走线、以及一串接(cascading)共模滤波器。印刷电路板具有一第一表面以及相对于第一表面的一第二表面。接地平面层具有一第一表面,且接地平面层的第一表面接触印刷电路板的第二表面。此对第一差分走线以及第二差分走线位于印刷电路板的第一表面。第一差分走线以及第二差分走线带有一电子信号。串接共模滤波器包括一外部共模滤波器以及一内部共模滤波器。外部共模滤波器包括位于接地平面层的第一表面的一u型空隙区段。内部共模滤波器包括位于接地平面层的第一表面的一h型空隙区段。h型空隙区段位于u型空隙区段附近。

8.在一实现方式中,u型空隙区段包括一第一空隙区段、一第二空隙区段、以及一第三空隙区段,且第一空隙区段与第二空隙区段通过第三空隙区段连接。h型空隙区段包括一第四空隙区段、一第五空隙区段、以及一第六空隙区段。第一四隙区段与第五空隙区段通过第六空隙区段连接。第六空隙区段将第四空隙区段分成具有一第一长度的一第一部分以及具有一第二长度的一第二部分。第一空隙区段与二空隙区段具有相同的形状。在一实施方式中,第四空隙区段与第五空隙区段具有相同的形状。在一实施方式中,第二空隙区段的长度取决于消除在一第一辐射频率下的噪声,第四空隙区段的第二部分的第二长度取决于消除在一第二辐射频率下的噪声,以及第二辐射频率是第一辐射频率的谐波。在一实施方式中,第三空隙区段与第六空隙区段之间的间隔大于当消除在一目标辐射频率处的噪声时一空隙区段的理想长度。在一实施方式中,第一空隙区段的长度以及第二空隙区段的长度由以下限制来确定:

9.l1=l

x-l

4x

10.2l

4x

≥l2≥l

4x

11.l3≤l

4x

12.l4=l

2x

13.其中,l1为第一空隙区段的长度与第二空隙区段的长度,l2为第三空隙区段与第六空隙区段之间的间隔,l3为第四空隙区段的第一部分的第一长度,l

x

=1/(4f

×

td),td为关于在第一差分走线与第二差分走线上传播的一差分信号的每密耳(mil)长度的时间延迟,且f为目标辐射频率。

14.在一实施方式中,在第一空隙区段与第一差分走线之间的距离相同于在第二空隙区段与第二差分走线之间的距离。在一实施方式中,在第四空隙区段与第一差分走线之间的距离相同于在第五空隙区段与第二差分走线之间的距离。在一实施方式中,在第一空隙区段与第一差分走线之间的距离大于在第四空隙区段与第一差分走线之间的距离。在一实施方式中,h型空隙区段的宽度小于u型空隙区段的宽度。

15.根据本发明的某些方面,一制造低干扰差分走线的方法包括在一印刷电路板的一第一表面形成一第一差分走线以及一第二差分走线。一第一空隙区段形成在一接地平面层中。接地平面层连接印刷电路板的一第二表面,且印刷电路板的第二表面相对于其第一表面。通过以下多个步骤,在接地平面层上形成一串接共模滤波器,这些步骤包括:(a)根据一第一目标辐射频率来确定一第二空隙区段的长度,且连接第一空隙区段与第二空隙区段以形成具有一u型的一外部共模滤波器;(b)根据一第二目标辐射频率来决定一第五空隙区段

的一第一部分的长度,且第二目标辐射频率与第一目标辐射频率之间具有谐波相关性;以及(c)通过一第六空隙区段将第五空隙区段连接至一第四空隙区段,以形成具有一h型的一内部共模滤波器。h型的宽度小于u型的宽度。

16.在一实施方式中,第一空隙区段与第二空隙区段具有相同的形状。在一实施方式中,第四空隙区段与第五空隙区段具有相同的形状。在一实施方式中,第二目标辐射频率为第一目标辐射频率的两倍。在一实施方式中,第一空隙区段通过一第三空隙区段连接第二空隙区段,且第一空隙区段的长度以及第二空隙区段的长度由以下限制来确定:

17.l1=l

x-l

4x

18.2l

4x

≥l2≥l

4x

19.l3≤l

4x

20.l4=l

2x

21.其中,l1为第一空隙区段的长度与第二空隙区段的长度,l2为第三空隙区段与第六空隙区段之间的间隔,l3为第四空隙区段的第一部分的第一长度,l

x

=1/(4f

×

td),td为关于在第一差分走线与第二差分走线上传播的一差分信号的每密耳(mil)长度的时间延迟,且f为目标辐射频率。

22.在一实施方式中,在第一空隙区段与第一差分走线之间的距离相同于在第二空隙区段与第二差分走线之间的距离。在一实施方式中,在第四空隙区段与第一差分走线之间的距离相同于在第五空隙区段与第二差分走线之间的距离。在一实施方式中,在第一空隙区段与第一差分走线之间的距离大于在第四空隙区段与第一差分走线之间的距离。

23.以上发明内容并非旨在代表本发明的每个实施例或每个方面。相反,前述发明内容仅提供了在此阐述的一些新颖方面和特征的示例。当结合附图和所附权利要求时,从用于实施本发明的代表性实施例和模式的以下详细描述,上述特征和优点以及本发明的其他特征和优点将变得显而易见。鉴于参考附图做出的各种实施例的详细描述,本发明的其他方面对于本领域普通技术人员将是显而易见的,下面提供了其简要描述。

附图说明

24.从以下对代表性实施例的描述连同参考附图,将更好地理解本发明及其优点和附图。这些附图仅描绘了代表性实施例,因此不应被视为对各种实施例或权利要求的范围的限制。

25.图1表示印刷电路板上的现有技术差分走线的示例图;

26.图2是来自机箱中现有技术差分走线的信号在特定频率下的电子信号干扰的示意图;

27.图3是本发明的某些方面的包括多个电路板的电子设备的后视图,这些电路板包括具有示例性减少干扰返回路径的走线;

28.图4是本公开的某些方面的具有返回路径以减少共模能量的示例差分走线的透视图;

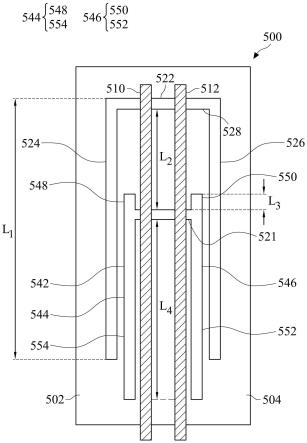

29.图5是在本发明的某些方面,根据本发明的一些实施方式而具有共模滤波器的示例差分走线的上视图;

30.图6是本发明的某些方面,在图5的示例差分走线的第一种的返回电流特性的曲线

图;

31.图7是本发明的某些方面,在图5的示例差分走线的第二种的返回电流特性的曲线图。

32.符号说明

33.10:返回电流电路走线

34.12:印刷电路板

35.14:接地平面层

36.20:表面

37.22:差分走线

38.24:差分走线

39.30:箭头(插入电流)

40.32:箭头(感应电流)

41.34:箭头(返回电流)

42.50:线(走线噪声)

43.60:线(系统噪声)

44.80:尖波(噪声辐射)

45.100:电子装置

46.110:机箱

47.120:组件

48.130:电源单元

49.140:组件

50.200:走线配置

51.202:印刷电路板

52.204:第一表面

53.206:第二表面

54.208:接地平面层

55.210:走线

56.212:走线

57.220:第一表面

58.222:u型电流返回路径图案

59.224:第一空隙区段

60.226:第二空隙区段

61.228:第三空隙区段

62.232:箭头(插入电流)

63.234:箭头(感应电流)

64.236:箭头(返回电流)

65.238:虚线(被消除的返回电流)

66.500:串接共模滤波器

67.502:印刷电路板

68.504:第一表面

69.510:差分走线

70.512:差分走线

71.521:第六空隙区段

72.522:外部共模滤波器

73.524:第一空隙区段

74.526:第二空隙区段

75.528:第三空隙区段

76.542:内部共模滤波器

77.544:第四空隙区段

78.546:第五空隙区段

79.548:第四空隙区段的第一部分

80.552:第五空隙区段的第二部分

81.554:第四空隙区段的第二部分

82.550:第五空隙区段的第一部分

83.700:曲线图

84.800:曲线图

85.l1~l4:长度

具体实施方式

86.为使本发明的上述目的、特征和优点能更明显易懂,下文特举一优选实施例,并配合所附的附图,作详细说明如下。

87.本发明提供一种用于减少信号辐射的共模滤波器。共模滤波器在印刷电路板布线中实现,且可用于减少在多个频带的信号辐射。在需要多数据速率支持的应用中,例如快捷周边组件互连介面(peripheral component interconnect express,pcie)、sas等,被设计成用于一缩减频带的共模滤波器不足,以降低辐射风险。因此,本发明的各种实施例提供的共模滤波器利用串接技术来实现多个辐射带的辐射减少。

88.参考附图描述了各种实施例,其中贯穿附图使用相同的参考数字标记来表示相似或等效的元件。附图不一定按比例绘制并且仅被提供以说明本发明的方面和特征。尽管本案所属技术领于中具有通常知识者将认识到本发明的某些方面和特征可以在没有一个或多个具体细节、具有其他关系或其他方法的情况下实践,但本案还是阐述了许多具体细节、关系、和方法以提供对这些某些方面和特征的充分理解。在某些情况下,出于说明的目的,没有详细显示出众所周知的结构或操作。此处揭露的各种实施例不一定受所说明的动作或事件的顺序限制,因为一些动作可能在不同的顺序下发生以及/或与其他动作或事件同时发生。此外,并非所有图示的动作或事件都是实现本发明的某些方面和特征所必需的。

89.为了本详细描述的目的,除非特别声明,并且在适当的情况下,单数包括多个,反之亦然。“包括”一词的意思是“包括但不限于”。此外,诸如“大约”、“几乎”、“实质上”、“大概”等近似词在本文中可用于表示“在”、“接近”、“几乎在”、“在3~5%以内”、“在可接受的制造容限范围内”或其任何逻辑组合。类似地,术语“垂直”或“水平”旨在分别另外包括垂直

或水平方向的“3~5%内”。此外,诸如“顶部”、“底部”、“左”、“右”、“上方”和“下方”等方向词旨在与参考附图中所描述的等效方向相关联、从被引用的目标或元件上下文中理解(例如从目标或元件的常用位置)、或如本文中的其他说明。

90.参阅图3,提供了一示例电子装置100。电子装置100为一服务器,其包括包含在机箱110中的多个不同组件。例如,一组组件120安装在位于两个电源单元130上方机箱110的一侧上。另一组部件140安装在机箱110中的垂直槽中。两组组件120和140中的每个组件包括印刷电路板。这些印刷电路板包括多个差分走线,其连接板上电子组件并在组件之间传导信号。机箱110可以具有多个孔,组件120和140的电路板产生的噪声可能通过这些孔发出。

91.图2是显示通过具有已知差分走线电路的机箱110中的孔的输出噪声的曲线图。如图2所示,在此示例中,输出噪声出现在大约8ghz处。由于来自在机箱中电路板上差分走线的共模能量,因而产生了输出噪声。

92.为了减少这种干扰,组件120和140(显示在图3中)的每个电路板都包括多个差分走线,这些差分走线在接地平面层中合并一返回路径设计,这降低了在目标频率5ghz处的共模能量。此走线的合并从而降低了由电子装置100所产生的电子噪声。目标频率是由机箱110的干扰测试来确定。目标频率取决于在机箱110中的板上传输的走线数据速率。

93.设计一返回走线以减少共模能量的过程依赖于以下事实:可使用一四端口s-参数(four port s-parameter)对差分走线进行建模。对于一四端口(2个信号走线)s-参数,有插入项(insertion term)s

31

和s

42

以及感应项(induction term)s

41

和s

32

。根据楞次定律(lenz’s law),感应项与插入项的方向相反。基于混合模式s-参数公式,差分信号的差模输出(s

dd21

)为:

[0094][0095]

差分信号的共模输出(s

cc21

)则为:

[0096][0097]

为了减少共模输出能量,需要增加耦合项(coupling term)。如图1,在走线22正下方的接地平面14中将存在由箭头34表示的一差分信号的一返回电流。以箭头34表示的返回电流与在走线22中以箭头30表示的电流以相反的方向流动。因此,可以设计一返回电流路径,其导致在目标频率处的相消干扰。在这种情况下,一附近的走线,例如走线24,将成为返回电流的新路径。这个新的返回电流路径增加了耦合项。因此,共模将大大减少。新返回电流路径长度的等式为:

[0098]

l

x

=1/(4f

×

td)

ꢀꢀꢀ

(式3)

[0099]

在这个等式中,l

x

是表示新路径的长度。td表示是关于在走线中传播的差分信号的每密耳(mil)长度的时间延迟,f则是表示目标辐射频率。

[0100]

图4是根据式3中指示的上述标准设计的示例走线配置200的透视图。图4中的走线配置200形成在印刷电路板202上。印刷电路板202具有第一表面204和相对的第二表面206。第二表面206接触接地平面层208。两条平行走线210和212形成在印刷电路板202的第一表面204上。接地平面层208具有第一表面220,其接触印刷电路板202的第二表面206。一u型电

是第四空隙区段544的第一部分548的长度。在一些实施方式中,第四空隙区段544的第一部分548与第五空隙区段546的第一部分550具有相同的长度。l4是第四空隙区段544的第二部分554的长度。在一些实施方式中,第五空隙区段546的第二部分552和第四空隙区段544的第二部分554具有相同的长度。

[0106]

串接共模滤波器500具有围绕不同长度l1、l2、l3、与l4的设计限制,用于滤除在多个频率的返回电流。串接共模滤波器500提供额外的电感和电容,并且作为用于在多个频率下返回电流的lc滤波器。

[0107]

在图5中,内部共模滤波器542和外部共模滤波器522的尺寸由以下等式4a~4d所限制。

[0108]

l1=l

x-l

4x

ꢀꢀꢀ

(式4a)

[0109]

2l

4x

≥l2≥l

4x

ꢀꢀꢀ

(式4b)

[0110]

l3≤l

4x

ꢀꢀꢀ

(式4c)

[0111]

l4=l

2x

ꢀꢀꢀ

(式4d)

[0112]

在等式4a~4d中,l

x

是用以减少在如等式3中定义的基频处辐射的共模滤波器(例如,图4的u型电流返回路径图案)的路径长度。l

2x

是用以减少两倍基频处辐射的一共模滤波器的长度,以及l

4x

是用以减少四倍基频处辐射的一共模滤波器的长度等式3可用于确定l

x

、l

2x

、与和l

4x

。从等式4a与4d中,l1和l4分别基于所选的频率而固定。也就是说,l1是为基频所确定的路径长度与为等于四倍基频的频率所确定的路径长度之间的差值。l4采用等于两倍基频的频率的路径长度值。然后,可以选择l2和l3以满足等式4b与4c的限制。

[0113]

图6与图7提供根据本发明的一些实施方式,使用等式4a~4d的设计限制以选择一串接共模滤波器的模拟结果。图6是在图5的示例差分走线的第一种的返回电流特性的曲线图600。在图5中的示例差分走线是具有差分走线510和512的微带结构(micro-strip structure)。对于微带结构,l

x

=526mil(用于4ghz),l

2x

=263密耳(mil)(用于8ghz),l

4x

=132.5mil(用于16ghz)。在本示例中,l1=396mil,l2=132mil,l3=30mil,l4=263mil。并且,降低频率为4.32ghz、8.09ghz和15.97ghz。如图所示。如图6所示,返回电流的下降大约发生在降低频率处,这会导致额外的耦合,然后减少在特定频率处的共同节点噪声。符号602表示在4.32ghz处的下降,符号604表示在8.09ghz处的下降,而符号606表示在15.97ghz处的下降。

[0114]

图7是当以带状线结构制造时,在图5的示例差分走线的第二种的返回电流特性的曲线图700。对于带状线结构(sprit-line structure),l

x

=464密耳(mil)(用于4ghz),l

2x

=232mil(用于8ghz),l

4x

=116mil(用于16ghz)。在本例中,l1=348mil,l2=116mil,l3=116mil,l4=232mil。并且,降低频率为4.11ghz、8.0ghz和16.39ghz。如图7所示,返回电流的下降大约发生在降低频率处,这会导致额外的耦合,然后减少在特定频率处的共同节点噪声。符号702表示在4.11ghz处的下降,符号704表示在8.0ghz处的下降,符号706表示在16.39ghz处的下降。降低频率是有谐波相关性的。本发明的实施例无论是在微带结构中还是在带状线结构中,都可用于减少高速走线中的干扰。

[0115]

尽管所揭露的实施例已经以关于一个或多个实施方式来图解和说明,但是在阅读和理解本说明书和附图之后,本技术领域中具有通常知识者将发现或知道等同的更动和修改。此外,虽然本发明的特定特征可能仅在多个实施方式中的一种中公开,但是这种特征可

以与其他实施方式的一个或多个其他特征组合,其对于任何给定或特定应用可能是期望的和有利的。

[0116]

虽然上文已经描述了本发明的各种实施例,但是应当理解,它们仅通过示例而非限制的方式呈现。在不脱离本发明的精神或范围的情况下,可以根据本文的揭露对公开的实施例进行许多变更。因此,本发明的广度和范围不应受到上述任何实施例的限制。相反地,本发明的范围应根据所附权利要求及其等同物来定义。

[0117]

虽然结合以上优选实施例公开了本发明,然而其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,可作更动与润饰,因此本发明的保护范围应当以附上的权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1