基于包络追踪技术和Doherty构架的功率放大电路及其设计方法与流程

基于包络追踪技术和doherty构架的功率放大电路及其设计方法

技术领域

1.本发明属于通信基站技术领域,特别是一种基于包络追踪技术和doherty构架的功率放大电路及其设计方法。

背景技术:

2.目前基站类功放在设计的时候都是采用多尔蒂(doherty)构架的功率放大电路,该功率放大电路可以很好的兼顾输出平均功率时的效率和输出峰值功率时的线性度。

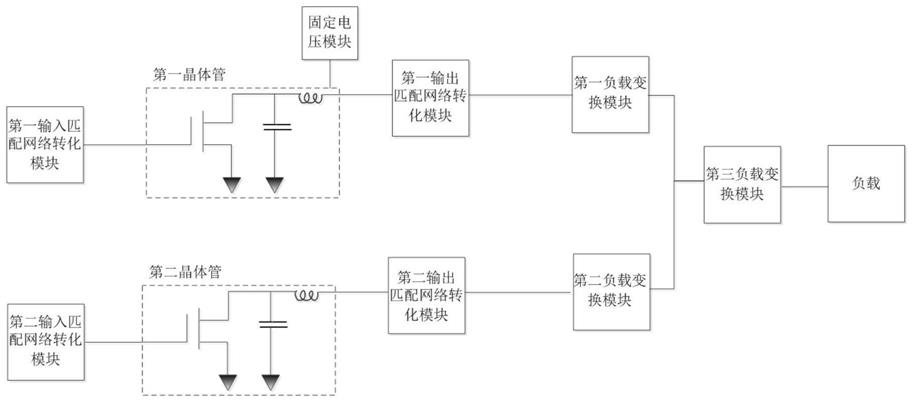

3.传统的适用于窄带信号的doherty架构功放电路结构原理如图1所示,包括doherty构架以及外置电源;

4.doherty构架包括第一输入匹配网络转化模块、第二输入匹配网络转化模块、第一晶体管、第二晶体管、第一输出匹配网络转化模块、第二输出匹配网络转化模块、第一负载变换模块、第二负载变换模块以及第三负载变换模块;

5.第一输入匹配网络转化模块其输出端连接所述第一晶体管的栅极;第二输入匹配网络转化模块的输出端连接所述第二晶体管的栅极;

6.第一晶体管与第二晶体管的源极与接地;

7.第一输出匹配网络转化模块的输入端与第一晶体管的漏极连接;第二输出匹配网络转化模块的输入端与第二晶体管的漏极连接;

8.第一负载变换模块的输入端与第一输出匹配网络转化模块的输出短连接,第二负载变换模块的输入端与第二输出匹配网络转化模块的输出端连接;

9.第三负载变化模块的输入端分别与第一负载变换模块的输出端以及第二负载变化模块的输出端连接,

10.第三负载变化模块的输出端及外部负载;

11.外置电源采用固定电压模块,固定电压模块的输出端与第一晶体管的漏极连接,或者分别和第一晶体管的漏极以及第二晶体管的漏极连接。

12.由于传统doherty架构的功放电路窄带特性逐步显现,为了解决带宽偏窄的问题,国内国外相关专家提出了双匹配的doherty架构的功放电路,其结构如图2所示。该功放电路可以很好的解决带宽问题。

13.但不论是适用于窄带doherty架构的功放电路或是适用于宽带doherty架构的功放电路都存在以下问题:

14.由于使用了固定电压模块仅能提供固定漏压,在基站期望的平均输出功率有回退的时候,功放电路处于线性区,所以效率都很难保证。

技术实现要素:

15.针对传统doherty架构的功放电路存在效率难以保证的问题,本发明提出一种基于包络追踪技术和doherty构架的功率放大电路。

16.同时提供了该电路的设计方法。

17.本发明的目的是通过以下技术方案予以实现,

18.一种基于包络追踪技术和doherty构架的功率放大电路,包括doherty架构以及外置电源;所述外置电源为et电源或apt电源;et电源或apt电源的输出端接入doherty架构中第一晶体管的漏极;

19.或者et电源或apt电源的输出端同时与doherty架构中第一晶体管和第二晶体管的漏极连接。

20.进一步地,上述doherty架构为适用于窄带信号的doherty架构,或者为适用于宽带信号的双匹配doherty架构。

21.本发明还提供了上述基于包络追踪技术和doherty构架的功率放大电路的设计方法,具体实现步骤如下:

22.步骤1:根据给定的输入信号峰均比par和平均有效输出功率pave确定功率放大电路的饱和功率p1;

23.p1=pave+par;

24.步骤2:确定doherty架构中单个晶体管的饱和功率值p1/2;

25.步骤3:采用仿真软件并调用单个晶体管模型,进行loadpull仿真,调整单个晶体管模型漏压,记录晶体管模型的饱和功率为p1/2时对应的晶体管模型漏压值,并将该漏压值作为et电源或apt电源的最大电压值v

max

,以及晶体管模型的饱和功率为pave时对应的晶体管模型漏压值,并将该漏压值作为et电源或apt电源的平均有效电压值v

rms

;

26.步骤4:通过最大电压值v

max

和平均有效电压值v

rms

求取et电源或apt电源的最小电压值v

min

,得到et电源或apt电源的电压范围,从而选取合适的et电源或apt电源;

27.具体计算公式如下:

[0028][0029]

其中,p1、p2为正数因子,取值范围均大于0且小于1;

[0030]

步骤5:et电源或apt电源与晶体管的匹配;

[0031]

步骤5.1:根据选取的et电源或apt电源最佳负载值r1以及晶体管输出额定功率时的漏级效率de,得出晶体管输出平均功率时晶体管电流源输出端plana端面处的阻抗r2;

[0032]

具体计算公式如下:

[0033][0034]

其中,v1为晶体管自有特征电压,晶体管输出额定功率时的漏级效率de再执行步骤3时获取;

[0035]

步骤5.2:基于史密斯圆阻抗变换方法将负载的阻抗转化到晶体管电流源输出端plana端面处的阻抗r2处,从而实现et电源或apt电源与晶体管的匹配;

[0036]

步骤6:基于包络追踪技术的功率放大电路搭建完成。

[0037]

进一步地,上述仿真软件采用advanced design system设计软件系统。

[0038]

与现有技术相比,本发明的有益技术效果如下:

[0039]

相比于传统的doherty架构功率放大电路及双匹配doherty架构功率放大电路,本发明提出的功率放大电路,可实现doherty架构与et/apt之间有效匹配;当et(envelope tracking)电源或apt(average power tracking)电源的最佳负载值与晶体管电流源处的等效电阻值满足匹配条件时,实现et/apt和晶体管最佳匹配效果,使整个et/apt+晶体管的整体效率达到最优;当输出功率是额定功率回退3db或者6db时,由于使用了比固定漏压更低的电压值,使得功放在回退功率下也工作在饱和状态,进而可以有效提高此输出功率下的效率。

附图说明

[0040]

通过阅读下文优选的具体实施方式中的详细描述,本发明各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。说明书附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。显而易见地,下面描述的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。而且在整个附图中,用相同的附图标记表示相同的部件。

[0041]

图1为传统适用于窄带的基于doherty构架的功率放大电路结构示意图;

[0042]

图2为传统适用于宽带的基于doherty构架的功率放大电路结构示意图;

[0043]

图3为实施例1的功率放大电路结构示意图;

[0044]

图4为实施例2的功率放大电路结构示意图;

具体实施方式

[0045]

下面将参照附图更详细地描述本发明的具体实施例。虽然附图中显示了本发明的具体实施例,然而应当理解,可以以各种形式实现本发明而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本发明,并且能够将本发明的范围完整的传达给本领域的技术人员。

[0046]

需要说明的是,在说明书及权利要求当中使用了某些词汇来指称特定组件。本领域技术人员应可以理解,技术人员可能会用不同名词来称呼同一个组件。本说明书及权利要求并不以名词的差异来作为区分组件的方式,而是以组件在功能上的差异来作为区分的准则。如在通篇说明书及权利要求当中所提及的“包含”或“包括”为一开放式用语,故应解释成“包含但不限定于”。说明书后续描述为实施本发明的较佳实施方式,然所述描述乃以说明书的一般原则为目的,并非用以限定本发明的范围。本发明的保护范围当视所附权利要求所界定者为准。

[0047]

为便于对本发明实施例的理解,下面将结合附图以具体实施例为例做进一步的解释说明,且各个附图并不构成对本发明实施例的限定。

[0048]

包络追踪et(envelope tracking)技术或平均功率追踪apt(average power tracking)技术可以根据功放输入射频信号的大小来调整功放漏级电压,既可以保证峰值信号的高线性度,也能保证均值信号和小信号时的高效率。所以et_pa技术一直是功放高效率方案研究的热点。

[0049]

本发明提供了一种基于包络追踪技术和doherty构架的功率放大电路,包括doherty架构以及外置电源;该电路的主要改进思路是:外置电源采用et电源或apt电源;et

电源或apt电源的输出端接入doherty架构中第一晶体管的漏极,或者et电源或apt电源的输出端同时与doherty架构中第一晶体管和第二晶体管的漏极连接;

[0050]

当et电源或apt电源与第一晶体管连接时,只需完成et电源或apt电源与第一晶体管的匹配;当et电源或apt电源同时连接第一晶体管和第二晶体管时,需分别完成络追踪电源与第一晶体管、第二晶体管的匹配。

[0051]

但是,本发明并不是简单的将et电源或apt电源和doherty架构进行结合,如何实现et电源或apt电源和doherty架构之间的最优匹配,从而确保晶体管的输出效率,使整个et/apt+晶体管的整体效率达到最优,本发明还提供了电路的设计方法,具体过程如下:

[0052]

步骤1:根据给定的输入信号峰均比par和平均有效输出功率pave确定功率放大电路的饱和功率p1;

[0053]

p1=pave+par;

[0054]

步骤2:确定doherty架构中单个晶体管的饱和功率值p1/2;

[0055]

步骤3:采用仿真软件(advanced design system)并调用单个晶体管模型,进行loadpull仿真,调整单个晶体管模型漏压,记录晶体管模型的饱和功率为p1/2时对应的晶体管模型漏压值,并将该漏压值作为et电源或apt电源的最大电压值v

max

,以及晶体管模型的饱和功率为pave时对应的晶体管模型漏压值,并将该漏压值作为et电源或apt电源的平均有效电压值v

rms

;

[0056]

步骤4:通过最大电压值v

max

和平均有效电压值v

rms

求取et电源或apt电源的最小电压值v

min

,得到et电源或apt电源的电压范围,从而选取合适的et电源或apt电源;

[0057]

具体计算公式如下:

[0058][0059]

其中,p1、p2为正数因子,取值范围均大于0且小于1;

[0060]

步骤5:et电源或apt电源与晶体管的匹配;

[0061]

步骤5.1:根据选取的et电源或apt电源最佳负载值r1以及晶体管输出额定功率时的漏级效率de,得出晶体管输出平均功率时晶体管电流源输出端plana端面处的阻抗r2;

[0062]

具体计算公式如下:

[0063][0064]

其中,v1为晶体管自有特征电压,晶体管输出额定功率时的漏级效率de再执行步骤3时获取;

[0065]

步骤5.2:基于史密斯圆阻抗变换方法将负载的阻抗转化到晶体管电流源输出端plana端面处的阻抗r2处,从而实现et电源或apt电源与晶体管的匹配;

[0066]

步骤6:基于包络追踪技术的功率放大电路搭建完成。

[0067]

基于上述对本发明电路改进思路及设计方法的说明,现根据以下两个实施例对本发明进行详细的介绍:

[0068]

实施例1

[0069]

该实施例给出了适用于窄带的基于包络追踪技术和doherty构架的功率放大电路结构,如图3所示,包括第一输入匹配网络转化模块、第二输入匹配网络转化模块、第一晶体

管、第二晶体管、et电源或apt电源、第一输出匹配网络转化模块、第二输出匹配网络转化模块、第一负载变换模块、第二负载变换模块以及第三负载变换模块;

[0070]

第一输入匹配网络转化模块其输出端连接所述第一晶体管的栅极;第二输入匹配网络转化模块的输出端连接所述第二晶体管的栅极;

[0071]

第一晶体管与第二晶体管的源极与接地;第一晶体管与第二晶体管都包括各自的内部电流源输出端plana和外部输出端planb;

[0072]

et电源或apt电源的输出端接入第一晶体管的漏极,或者et电源或apt电源的输出端同时与第一晶体管和第二晶体管的漏极连接;本实施例中et电源或apt电源仅连接所述第一晶体管的漏极;

[0073]

第一输出匹配网络转化模块的输入端与第一晶体管的漏极连接;第二输出匹配网络转化模块的输入端与第二晶体管的漏极连接;

[0074]

第一负载变换模块的输入端与第一输出匹配网络转化模块的输出端连接,第二负载变换模块的输入端与第二输出匹配网络转化模块的输出端连接;

[0075]

第三负载变化模块的输入端分别与第一负载变换模块的输出端以及第二负载变化模块的输出端连接,

[0076]

第三负载变化模块的输出端及外部负载连接;

[0077]

本实施例中,各组成部分的功能如下:

[0078]

第一输入匹配网络转化模块和第二输入匹配网络转化模块,用于将第一晶体管和第二晶体管的最大增益阻抗匹配到预设阻抗;

[0079]

第一晶体管和第二晶体管用于信号放大,便于信号传输;

[0080]

et电源或apt电源用于给第一晶体管和/或第二晶体管提供可变电压,提高功率放大器的效率;

[0081]

第一输出匹配网络转化模块和第二输出匹配网络转化模块分别用于将第一晶体管和第二晶体管的最大功率点阻抗匹配到预设阻抗;

[0082]

第一负载变换模块,用于第一晶体管输出额定功率输出时实现功放的高效率;

[0083]

第二负载变换模块,用于实现第二晶体管电路接入时对第一晶体管所在电路(即第一输入匹配网络转化模块至负载)无影响,如果造成影响,会导致第一晶体管输出额定功率时效率变低。

[0084]

第三负载变化模块,用于将负载阻抗转换为第三负载变换模块的输入点阻抗。

[0085]

本实施例中:第一输出匹配网络转化模块和第二输出匹配网络转化模块、第一输入匹配网络转化模块和第二输入匹配网络转化模块均由微带线和电容组成;所述第一晶体管和第二晶体管均包括等效电阻、压控电流源、寄生电感和寄生电容。

[0086]

本实施例在工作时:第一输入匹配网络转化模块将50欧姆负载阻抗匹配到第一晶体管的最大增益阻抗;第一输出匹配网络转化模块将50欧姆负载匹配到第一晶体管的最大功率点(plan b端面)阻抗;第一负载变换模块和第三负载变化模块共同作用将50欧姆负载匹配到100欧姆,采用第一输出匹配网络转化模块将转换的100欧姆电阻匹配到plana端面。

[0087]

其中,采用第一输出匹配网络转化模块将转换的100欧姆电阻匹配到plana端面,与传统实施方式中将转换的100欧姆电阻匹配到功率放大器的最大效率点(plan b端面)阻抗不同。

[0088]

实施例2

[0089]

该实施例给出了适用于宽带的基于包络追踪技术和doherty构架的功率放大电路,如图4所示,包括第一输入匹配模块、第二输入匹配模块、第一晶体管、第二晶体管、et电源或apt电源、第一输出匹配模块、第二输出匹配模块以及负载变换模块;

[0090]

第一输入匹配模块的输出端连接所述第一晶体管的栅极;第二输入匹配模块的输出端连接所述第二晶体管的栅极;

[0091]

第一晶体管与第二晶体管的源极与接地;第一晶体管与第二晶体管都包括各自的内部电流源输出端plana和外部输出端planb;

[0092]

et电源或apt电源的输出端接入第一晶体管的漏极,或者et电源或apt电源的输出端同时与第一晶体管和第二晶体管的漏极连接;本实施例中et电源或apt电源仅连接所述第一晶体管的漏极;

[0093]

第一输出匹配模块的输入端与第一晶体管的漏极连接;第二输出匹配模块的输入端与第二晶体管的漏极连接;

[0094]

负载变换模块的输入端与第一输出匹配模块的输出端以及第二输出匹配模块的输出端连接;

[0095]

负载变化模块的输出端及外部负载连接;

[0096]

本实施例中:第一输入匹配模块和第二输入匹配模块、第一输出匹配模块和第二输出匹配模块均由微带线和电容组成;所述第一晶体管和第二晶体管均包括等效电阻、压控电流源、寄生电感和寄生电容。

[0097]

本实施例在工作时:第一输入匹配模块将50欧姆负载匹配到第一晶体管的最大增益阻抗;第一输出匹配模块在小信号时将25欧姆负载匹配到第一晶体管的最佳效率点阻抗;在大信号时25欧姆负载匹配到第一晶体管的最大功率点(plan b端面)阻抗(其中25欧姆为负载变换模块的输入点阻抗,是通过负载变换模块加50欧姆的负载级联得到);负载变换模块将50欧姆负载匹配到25欧姆;

[0098]

将输入信号输入到第一输入匹配模块,与流过包络追踪电源的信号重合后,依次通过负载变换模块,将50欧姆负载转换为25欧姆,其中25欧姆是通过负载变换模块加50欧姆负载级联得到;采用输出匹配模块将转换的25欧姆电阻匹配到plana端面。

[0099]

图3与图4中,plan a端面表示第一晶体管内部电流源输出端,即图3与图4中plan a虚线与实线的结点;plan b端面表示第一晶体管外部输出端,即图3与图4中plan b虚线与实线的结点。

[0100]

尽管以上结合附图对本发明的实施方案进行了描述,但本发明并不局限于上述的具体实施方案和应用领域,上述的具体实施方案仅仅是示意性的、指导性的,而不是限制性的。本领域的普通技术人员在本说明书的启示下和在不脱离本发明权利要求所保护的范围的情况下,还可以做出很多种的形式,这些均属于本发明保护之列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1