显示面板和显示装置的制作方法

本公开涉及显示,尤其涉及一种显示面板和显示装置。

背景技术:

1、相关技术中,像素驱动电路中的驱动晶体管存在磁滞现象,驱动晶体管的磁滞现象会导致显示面板的闪烁问题。

2、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、根据本公开的一个方面,提供一种显示面板,所述显示面板包括:衬底基板、第五导电层、电极层、像素界定层,第五导电层位于所述衬底基板的一侧,所述第五导电层包括电源线;电极层位于所述第五导电层背离所述衬底基板的一侧,所述电极层包括多个电极部,所述电极部包括相连接的本体部和增设部,所述增设部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影至少部分交叠;像素界定层位于所述电极层背离所述衬底基板的一侧,包括多个像素开口,多个所述像素开口与多个所述电极部一一对应设置,所述像素开口在所述衬底基板上的正投影和与其对应的所述电极部的本体部在所述衬底基板的正投影重合。

2、本公开一种示例性实施例中,多个所述电极部包括三种不同颜色的第一电极部、第二电极部、第三电极部,所述第一电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积大于所述第二电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积,所述第一电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积大于所述第三电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积。

3、本公开一种示例性实施例中,所述第一电极部为蓝色子像素单元对应的b电极部,所述第二电极部为红色子像素单元对应的r电极部,所述第三电极部为绿色子像素单元对应的g电极部;所述第一电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积大于所述第二电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积;所述第二电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积大于所述第三电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积。

4、本公开一种示例性实施例中,所述显示面板还包括多个行列分布的像素驱动电路,所述像素驱动电路包括驱动晶体管、第四晶体管,所述第四晶体管的第一极连接数据线,所述第四晶体管的第二极连接所述驱动晶体管的第一极;所述第二电极部在所述衬底基板上的正投影与所述数据线在所述衬底基板上的正投影的交叠面积大于所述第三电极部在所述衬底基板上的正投影与所述数据线在所述衬底基板上的正投影的交叠面积,所述第三电极部在所述衬底基板上的正投影与所述数据线在所述衬底基板上的正投影的交叠面积大于所述第一电极部在所述衬底基板上的正投影与所述数据线在所述衬底基板上的正投影的交叠面积。

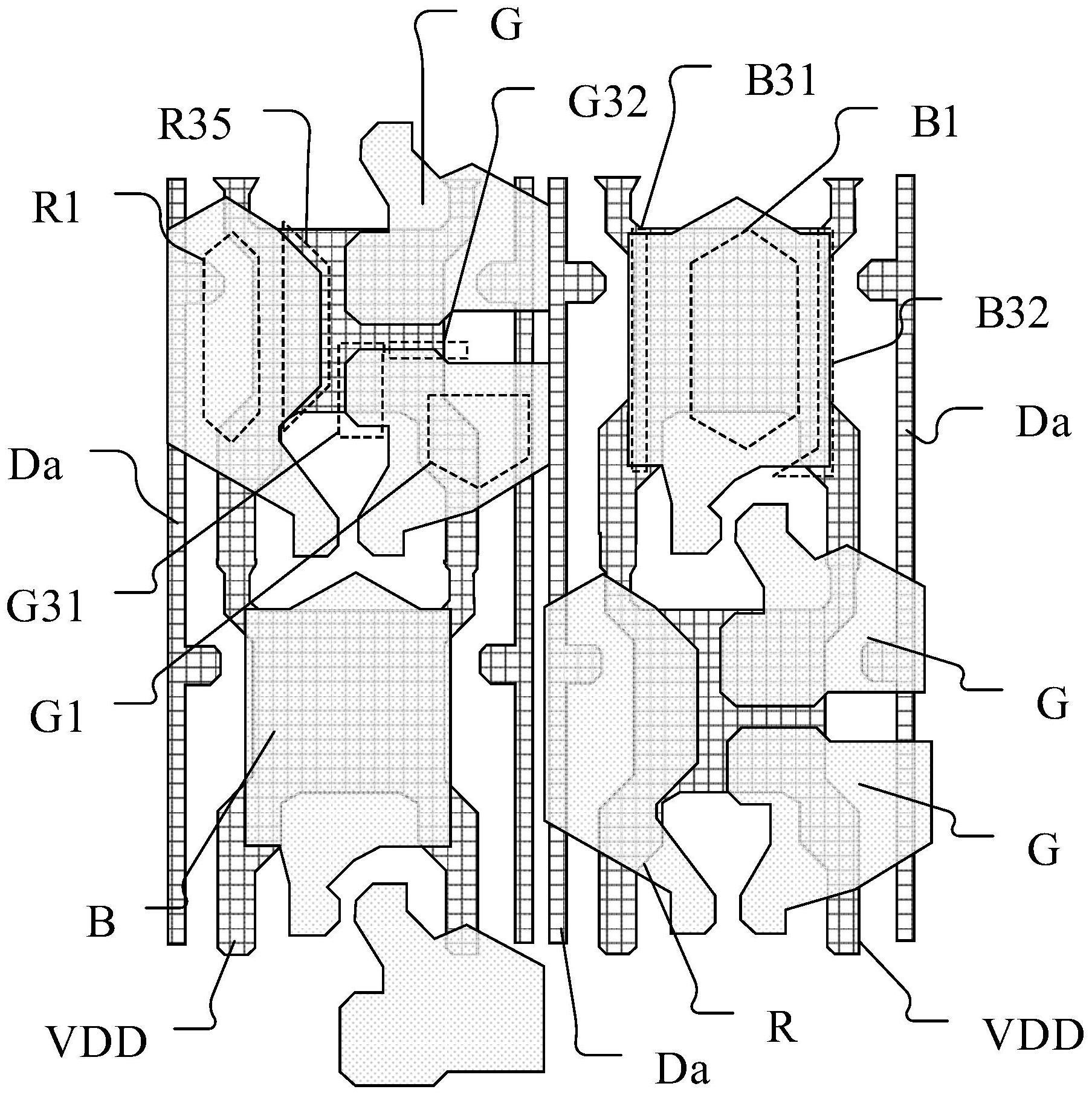

5、本公开一种示例性实施例中,多个所述电极部包括:多个r电极部、多个g电极部、多个b电极部,行方向上相邻的r电极部和b电极部之间设置有两个沿列方向分布的g电极部。

6、本公开一种示例性实施例中,所述r电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积为s1,所述r电极部的本体部在所述衬底基板上的正投影的面积为s2,s1/s2大于等于0.8且小于等于1.9。

7、本公开一种示例性实施例中,所述g电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积为s3,所述g电极部的本体部在所述衬底基板上的正投影的面积为s4,s3/s4大于等于1且小于等于1.7。

8、本公开一种示例性实施例中,所述b电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积为s5,所述b电极部的本体部在所述衬底基板上的正投影的面积为s6,s5/s6大于等于1.6且小于等于2。

9、本公开一种示例性实施例中,所述r电极部的本体部在所述衬底基板上的正投影的面积为s2,所述r电极部的增设部在所述衬底基板上的正投影和所述电源线在所述衬底基板上的正投影的交叠面积为s7,s7/s2大于等于0.04且小于等于1.14。

10、本公开一种示例性实施例中,所述g电极部的增设部包括第一增设部和第二增设部,在位于同一行相邻列的r电极部和g电极部中,所述g电极部的第一增设部在所述衬底基板上的正投影位于所述g电极部的本体部在所述衬底基板上的正投影面向所述r电极部在所述衬底基板上的正投影的一侧,所述g电极部的第二增设部在所述衬底基板上的正投影位于所述g电极部的本体部在所述衬底基板上的正投影面向另一g电极部在所述衬底基板上的正投影的一侧;所述g电极部的本体部在所述衬底基板上的正投影的面积为s4,所述g电极部的增设部在所述衬底基板上的正投影和所述电源线在所述衬底基板上的正投影的交叠面积为s8,s8/s4大于等于0.1且小于等于0.8。

11、本公开一种示例性实施例中,所述b电极部的增设部包括第三增设部和第四增设部,在位于同一行相邻列的b电极部和g电极部中,所述b电极部的第三增设部在所述衬底基板上的正投影位于所述b电极部的本体部在所述衬底基板上的正投影面向所述g电极部在所述衬底基板上的正投影的一侧,所述b电极部的第四增设部在所述衬底基板上的正投影位于所述b电极部的本体部在所述衬底基板上的正投影远离所述b电极部的第三增设部在衬底基板上的正投影的一侧;所述b电极部的本体部在所述衬底基板上的正投影的面积为s6,所述b电极部的增设部在所述衬底基板上的正投影和所述电源线在所述衬底基板上的正投影的交叠面积为s9,s9/s6大于等于0.1且小于等于0.5。

12、本公开一种示例性实施例中,所述第五导电层还包括多个第七桥接部,多个所述第七桥接部与多个所述电极部一一对应设置,所述电极部通过过孔连接与其对应设置的所述第七桥接部;所述r电极部通过第一过孔连接所述第七桥接部,所述r电极部包括相对设置的第一侧边和第二侧边,所述r电极部的第一侧边和第二侧边在衬底基板上的正投影沿列方向延伸,在位于同一行相邻列的r电极部和g电极部中,所述r电极部的第一侧边在所述衬底基板上的正投影位于所述r电极部第二侧边在所述衬底基板上的正投影与所述g电极部在所述衬底基板上的正投影之间,所述r电极部的第一侧边在所述衬底基板上的正投影的延长线经过所述第一过孔在所述衬底基板上的正投影;所述b电极部通过第二过孔连接所述第七桥接部,所述b电极部包括相对的第三侧边和第四侧边,所述b电极部的第三侧边和第四侧边在所述衬底基板上的正投影均沿列方向延伸,所述b电极部的第三侧边和第四侧边在所述衬底基板上的正投影的延长线位于所述第二过孔在所述衬底基板上的正投影的两侧。

13、本公开一种示例性实施例中,所述显示面板还包括像素驱动电路,所述像素驱动电路包括驱动晶体管、第一晶体管、第二晶体管、第六晶体管、第七晶体管;所述第一晶体管的第一极连接所述驱动晶体管的栅极,所述第一晶体管的第二极连接第一初始信号线,所述第二晶体管的第一极连接所述驱动晶体管的栅极,所述第二晶体管的第二极连接所述驱动晶体管的第二极,所述第六晶体管的第一极连接所述驱动晶体管的第二极,所述第七晶体管的第一极连接所述第六晶体管的第二极,所述第七晶体管的第二极连接第二初始信号线。所述显示面板还包括:第一有源层、第二有源层、第四导电层,第一有源层位于所述衬底基板和所述第五导电层之间,所述第一有源层包括第三有源部、第六有源部、第七有源部、第十有源部、第十一有源部,所述第三有源部用于形成所述驱动晶体管的沟道区,所述第六有源部用于形成所述第六晶体管的沟道区,所述第七有源部用于形成所述第七晶体管的沟道区,所述第十有源部连接于所述第七有源部和所述第六有源部之间,所述第十一有源部连接于所述第六有源部和所述第三有源部之间;第二有源层位于所述第一有源层和所述第五导电层之间,所述第二有源层包括第一有源部和第二有源部、第十二有源部,所述第一有源部用于形成所述第一晶体管的沟道区,所述第二有源部与所述第一有源部连接,用于形成所述第二晶体管的沟道区,所述第十二有源部连接于所述第二有源部远离所述第一有源部的一端;第四导电层位于所述第二有源层和所述第五导电层之间,所述第四导电层包括第二桥接部、第三桥接部,所述第二桥接部通过过孔连接所述第十有源部,所述第三桥接部分别通过过孔连接所述第十一有源部和所述第十二有源部;所述第二桥接部和所述第三桥接部在列方向上相对设置。

14、本公开一种示例性实施例中,所述显示面板包括沿行列方向分布的多个重复单元,每个所述重复单元包括两个像素驱动电路,两个所述像素驱动电路包括沿行方向分布的第一像素驱动电路和第二像素驱动电路,所述第一像素驱动电路和所述第二像素驱动电路镜像对称设置;所述像素驱动电路包括驱动晶体管、第六晶体管、第七晶体管,所述第六晶体管的第一极连接所述驱动晶体管的第二极,所述第七晶体管的第一极连接所述第六晶体管的第二极,所述第七晶体管的第二极连接第二初始信号线。所述显示面板还包括:第一有源层、第四导电层,第一有源层位于所述衬底基板和所述第五导电层之间,所述第一有源层包括第三有源部、第六有源部、第七有源部、第十有源部,所述第三有源部用于形成所述驱动晶体管的沟道区,所述第六有源部用于形成所述第六晶体管的沟道区,所述第七有源部用于形成所述第七晶体管的沟道区,所述第十有源部连接于所述第七有源部和所述第六有源部之间;第四导电层位于所述第一有源层和所述第五导电层之间,所述第四导电层包括第一桥接部和第二桥接部,所述第二桥接部通过过孔连接所述第十有源部,所述第一桥接部与所述重复单元一一对应设置,且所述第一桥接部通过过孔连接所述电源线;在行方向上相邻的所述第二桥接部在所述衬底基板上的正投影之间的距离等于l5,在行方向上相邻所述第二桥接部和所述第一桥接部在所述衬底基板上的正投影之间的距离等于l6,l5/l6大于等于0.8且小于等于1.2。

15、本公开一种示例性实施例中,所述显示面板包括沿行列方向分布的多个重复单元,每个所述重复单元包括两个像素驱动电路,两个所述像素驱动电路包括沿行方向分布的第一像素驱动电路和第二像素驱动电路,所述第一像素驱动电路和所述第二像素驱动电路镜像对称设置;所述像素驱动电路包括驱动晶体管、第四晶体管、第五晶体管,所述第四晶体管的第一极连接数据线,所述第四晶体管的第二极连接所述驱动晶体管的第一极,所述第五晶体管的第一极连接所述电源线,所述第五晶体管的第二极连接所述驱动晶体管的第一极。所述显示面板还包括:第一有源层、第四导电层,第一有源层所述第一有源层位于所述衬底基板和所述第五导电层之间,所述第一有源层还包括:第三有源部、第五有源部、第八有源部、第九有源部,第三有源部用于形成所述驱动晶体管的沟道区;第五有源部用于形成所述第五晶体管的沟道区;第八有源部连接于所述第五有源部远离所述第三有源部的一侧;第九有源部连接于同一所述重复单元中两所述第八有源部之间;第四导电层位于所述第一有源层和所述第五导电层之间,所述第四导电层包括:多个第一桥接部,多个所述第一桥接部与多个所述重复单元一一对应设置,所述第一桥接部通过过孔连接所述第九有源部,且所述第一桥接部通过过孔连接所述电源线;所述第一桥接部包括用于连接所述第九有源部的第一过孔连接部和用于连接所述电源线的两个第二过孔连接部,两所述第二过孔连接部连接于所述第一过孔连接部的两侧,且所述第一桥接部上形成有位于所述第一过孔连接部和所述第二过孔连接部之间的缺口;所述电源线在所述衬底基板上的正投影、所述数据线在所述衬底基板上的正投影均沿列方向延伸,每列所述像素驱动电路对应设置一条所述电源线和一条所述数据线;所述数据线包括直线延伸部,所述直线延伸部在所述衬底基板上的正投影沿列方向直线延伸;在同一所述重复单元中,两条所述数据线在所述衬底基板上的正投影位于两条所述电源线在所述衬底基板上的正投影之间,且所述数据线的直线延伸部在所述衬底基板上的正投影和与其相邻的所述电源线在所述衬底基板上的正投影在行方向上的最小距离为l1,所述缺口在所述衬底基板上的正投影在行方向上的尺寸为l4,l1/l4大于等于0.9且小于等于1.1。

16、本公开一种示例性实施例中,所述显示面板包括沿行列方向分布的多个重复单元,每个所述重复单元包括两个像素驱动电路,两个所述像素驱动电路包括沿行方向分布的第一像素驱动电路和第二像素驱动电路,所述第一像素驱动电路和所述第二像素驱动电路镜像对称设置;所述像素驱动电路包括驱动晶体管、第四晶体管、第五晶体管,所述第四晶体管的第一极连接数据线,所述第四晶体管的第二极连接所述驱动晶体管的第一极,所述第五晶体管的第一极连接所述电源线,所述第五晶体管的第二极连接所述驱动晶体管的第一极;所述电源线在所述衬底基板上的正投影、所述数据线在所述衬底基板上的正投影均沿列方向延伸,每列所述像素驱动电路对应设置一条所述电源线和一条所述数据线;所述数据线包括直线延伸部,所述直线延伸部在所述衬底基板上的正投影沿列方向直线延伸;在同一所述重复单元中,两条所述数据线在所述衬底基板上的正投影位于两条所述电源线在所述衬底基板上的正投影之间,且所述数据线的直线延伸部在所述衬底基板上的正投影和与其相邻的所述电源线在所述衬底基板上的正投影在行方向上的最小距离为l1,两所述数据线中直线延伸部在所述衬底基板上的正投影在行方向上的最小距离为l2,l1/l2大于等于1.4。

17、本公开一种示例性实施例中,所述显示面板包括像素驱动电路,所述像素驱动电路包括驱动晶体管、第四晶体管、第五晶体管,所述第四晶体管的第一极连接数据线,所述第四晶体管的第二极连接所述驱动晶体管的第一极,所述第五晶体管的第一极连接所述电源线,所述第五晶体管的第二极连接所述驱动晶体管的第一极;所述电源线在所述衬底基板上的正投影、所述数据线在所述衬底基板上的正投影均沿列方向延伸,每列所述像素驱动电路对应设置一条所述电源线和一条所述数据线;所述数据线包括直线延伸部,所述直线延伸部在所述衬底基板上的正投影沿列方向直线延伸;所述数据线的直线延伸部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影在行方向上的最小距离为l1,所述数据线的直线延伸部在所述衬底基板上的正投影在行方向上的尺寸为l3,l1/l3大于等于1.4且小于等于3。

18、本公开一种示例性实施例中,所述显示面板包括像素驱动电路,所述像素驱动电路包括驱动晶体管、第一晶体管、第二晶体管,所述第一晶体管的第一极连接所述驱动晶体管的栅极,所述第一晶体管的第二极连接第一初始信号线,所述第二晶体管的第一极连接所述驱动晶体管的栅极,所述第二晶体管的第二极连接所述驱动晶体管的第二极,所述显示面板还包括:第一有源层、第二有源层,第一有源层位于所述衬底基板和所述第五导电层之间,所述第一有源层包括第三有源部,所述第三有源部用于形成所述驱动晶体管的沟道区;第二有源层位于所述第一有源层和所述第五导电层之间,所述第二有源层包括:第一有源部和第二有源部,所述第一有源部用于形成所述第一晶体管的沟道区,所述第二有源部与所述第一有源部连接,用于形成所述第二晶体管的沟道区;所述电源线包括:第一延伸部、第二延伸部、第三延伸部,所述第二延伸部连接于所述第一延伸部和所述第三延伸部之间;所述第二延伸部在所述衬底基板上的正投影在行方向上的尺寸大于第一延伸部在所述衬底基板上的正投影在行方向上的尺寸,且所述第二延伸部在所述衬底基板上的正投影在行方向上的尺寸大于所述第三延伸部在所述衬底基板上的正投影在行方向上的尺寸;所述第二延伸部在所述衬底基板上的正投影覆盖所述第一有源部在所述衬底基板上的正投影、所述第二有源部在所述衬底基板上的正投影。

19、本公开一种示例性实施例中,所述显示面板包括沿行列方向分布的多个重复单元,每个所述重复单元包括两个所述像素驱动电路,两个所述像素驱动电路包括沿行方向分布的第一像素驱动电路和第二像素驱动电路,所述第一像素驱动电路和所述第二像素驱动电路镜像对称设置;每列所述像素驱动电路对应设置一条所述电源线,在行方向上相邻所述重复单元中,相邻所述电源线的所述第二延伸部相连接;所述像素驱动电路包括驱动晶体管、电容,所述电容的第一电极连接所述驱动晶体管的栅极,所述电容的第二电极连接所述电源线,所述显示面板还包括:第一有源层、第二导电层,第一有源层位于所述衬底基板和所述第五导电层之间,所述第一有源层包括第三有源部,所述第三有源部用于形成所述驱动晶体管的沟道区;第二导电层位于所述第一有源层和所述第五导电层之间,所述第二导电层包括:第一导电部,所述第一导电部用于形成所述电容的第二电极;在同一所述重复单元中,相邻所述第一导电部连接。

20、本公开一种示例性实施例中,在同一所述重复单元中,相邻所述第一导电部通过第一连接部连接;所述像素驱动电路包括驱动晶体管、第五晶体管,所述第五晶体管的第一极连接所述电源线,所述第五晶体管的第二极连接所述驱动晶体管的第一极;所述第一有源层还包括:第五有源部、第八有源部、第九有源部,第五有源部用于形成所述第五晶体管的沟道区;第八有源部连接于所述第五有源部远离所述第三有源部的一侧;第九有源部连接于同一所述重复单元中两所述第八有源部之间;所述显示面板还包括:第一导电层、第四导电层,第一导电层位于所述第一有源层和所述第五导电层之间,所述第一导电层包括:使能信号线,所述使能信号线在所述衬底基板上的正投影沿行方向延伸,且覆盖所述第五有源部在所述衬底基板上的正投影,所述使能信号线的部分结构用于形成所述第五晶体管的栅极;第四导电层位于所述第一导电层和所述第五导电层之间,所述第四导电层包括:多个第一桥接部,多个所述第一桥接部与多个所述重复单元一一对应设置,所述第一桥接部分别通过过孔连接所述第九有源部、第一连接部,且所述第一桥接部通过过孔连接所述电源线。

21、本公开一种示例性实施例中,所述显示面板包括像素驱动电路,所述像素驱动电路包括驱动晶体管、第四晶体管、第六晶体管、第七晶体管、电容,所述第四晶体管的第一极连接数据线,所述第四晶体管的第二极连接所述驱动晶体管的第一极,所述第六晶体管的第一极连接所述驱动晶体管的第二极,所述第七晶体管的第一极连接所述第六晶体管的第二极,所述第七晶体管的第二极连接第二初始信号线,所述电容的第一电极连接所述驱动晶体管的栅极,第二电极连接所述电源线;所述显示面板还包括:第一有源层、第一导电层,第一有源层位于所述衬底基板和所述第五导电层之间,所述第一有源层包括:第三有源部、第四有源部、第六有源部、第七有源部,第三有源部用于形成所述驱动晶体管的沟道区;第四有源部连接于所述第三有源部的一侧,用于形成所述第四晶体管的沟道区;第六有源部连接于所述第三有源部远离所述第四有源部的一侧,用于形成所述第六晶体管的沟道区;第七有源部连接于所述第六有源部远离所述第三有源部的一侧,用于形成所述第七晶体管的沟道区;第一导电层位于所述第一有源层和所述第五导电层之间,所述第一导电层包括:第二栅线、使能信号线、第二复位信号线、第二导电部,第二栅线在所述衬底基板上的正投影沿行方向延伸且覆盖所述第四有源部在所述衬底基板上的正投影,所述第二栅线的部分结构用于形成所述第四晶体管的栅极;使能信号线在所述衬底基板上的正投影沿行方向延伸且覆盖所述第六有源部在所述衬底基板上的正投影,所述使能信号线的部分结构用于形成所述第六晶体管的栅极;第二复位信号线在所述衬底基板上的正投影沿行方向延伸且覆盖所述第七有源部在所述衬底基板上的正投影,所述第二复位信号线的部分结构用于形成所述第七晶体管的栅极;第二导电部,在所述衬底基板上的正投影覆盖所述第三有源部在所述衬底基板上的正投影,所述第二导电部用于形成所述驱动晶体管的栅极和所述电容的第一电极;其中,在同一所述像素驱动电路中,所述第二导电部在所述衬底基板上的正投影位于所述第二栅线在所述衬底基板上的正投影和所述使能信号线在所述衬底基板上的正投影之间;所述第二复位信号线在所述衬底基板上的正投影位于所述使能信号线在所述衬底基板上的正投影远离所述第二导电部在所述衬底基板上的正投影的一侧。

22、本公开一种示例性实施例中,本行像素驱动电路中的第二栅线复用为上一行像素驱动电路中的第二复位信号线。

23、本公开一种示例性实施例中,所述像素驱动电路还包括第一晶体管、第二晶体管,所述第一晶体管的第一极连接所述驱动晶体管的栅极,所述第一晶体管的第二极连接第一初始信号线,所述第二晶体管的第一极连接所述驱动晶体管的栅极,所述第二晶体管的第二极连接所述驱动晶体管的第二极,所述显示面板还包括:第二导电层、第二有源层、第三导电层,第二导电层位于所述第一导电层和所述第五导电层之间;第二有源层位于所述第二导电层和所述第五导电层之间,所述第二有源层包括:第一有源部、第二有源部,第一有源部用于形成所述第一晶体管的沟道区;第二有源部连接所述第一有源部,用于形成所述第二晶体管的沟道区;第三导电层位于所述第二有源层和所述第五导电层之间,所述第三导电层包括:第一复位信号线、第一栅线,第一复位信号线在所述衬底基板上的正投影覆盖所述第一有源部在所述衬底基板上的正投影,所述第一复位信号线的部分结构用于形成所述第一晶体管的顶栅;第一栅线在所述衬底基板上的正投影覆盖所述第二有源部在所述衬底基板上的正投影,所述第一栅线的部分结构用于形成所述第二晶体管的顶栅;在同一所述像素驱动电路中,所述第一栅线在所述衬底基板上的正投影位于所述第二导电部在所述衬底基板上的正投影和所述第二栅线在所述衬底基板上的正投影之间,所述第一复位信号线在所述衬底基板上的正投影位于所述第二栅线在所述衬底基板上的正投影远离所述第二导电部在所述衬底基板上的正投影的一侧。

24、本公开一种示例性实施例中,所述第二导电层包括:所述第一初始信号线、第三复位信号线、第三栅线,所述第一初始信号线在所述衬底基板上的正投影位于所述第一复位信号线在所述衬底基板上的正投影远离所述第二导电部在所述衬底基板上的正投影的一侧;第三复位信号线通过过孔连接所述第一复位信号线,在所述衬底基板上的正投影覆盖所述第一有源部在所述衬底基板上的正投影,所述第三复位信号线的部分结构用于形成所述第一晶体管的底栅;第三栅线在所述衬底基板上的正投影覆盖所述第二有源部在所述衬底基板上的正投影,所述第三栅线的部分结构用于形成所述第二晶体管的底栅。

25、本公开一种示例性实施例中,所述像素驱动电路还包括第五晶体管,所述第五晶体管的第一极连接所述电源线,所述第五晶体管的第二极连接所述驱动晶体管的第一极,栅极连接所述使能信号线;所述第一晶体管、第二晶体管为n型晶体管;所述驱动晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管为p型晶体管。

26、本公开一种示例性实施例中,所述显示面板还包括:第二导电层、第三导电层、第四导电层,第二导电层位于所述第一导电层和所述第五导电层之间;第三导电层位于所述第二导电层和所述第五导电层之间;第四导电层位于所述第三导电层和所述第五导电层之间,所述第四导电层包括所述第二初始信号线。

27、本公开一种示例性实施例中,多个所述电极部包括:多个r电极部、多个g电极部、多个b电极部;多个所述电极部沿行列方向阵列分布,多个所述电极部包括在行方向依次交替分布的第一电极列和第二电极列,所述第一电极列包括沿列方向依次交替分布的r电极部和b电极部,所述第二电极列包括沿列方向间隔分布的多个g电极部;多个所述电极部包括在列方向依次交替分布的第一电极行和第二电极行,所述第一电极行包括沿行方向依次交替分布的r电极部和b电极部,所述第二电极行包括沿行方向间隔分布的多个g电极部。

28、本公开一种示例性实施例中,所述r电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积为s10,所述r电极部的本体部在所述衬底基板上的正投影的面积为s11,s10/s11大于等于1.1且小于等于2;所述g电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积为s12,所述g电极部的本体部在所述衬底基板上的正投影的面积为s13,s12/s13大于等于0.2且小于等于1;所述b电极部在所述衬底基板上的正投影与所述电源线在所述衬底基板上的正投影的交叠面积为s14,所述b电极部的本体部在所述衬底基板上的正投影的面积为s15,s14/s15大于等于0.8且小于等于1.5。

29、本公开一种示例性实施例中,所述r电极部的本体部在所述衬底基板上的正投影的面积为s11,所述r电极部的增设部在所述衬底基板上的正投影和所述电源线在所述衬底基板上的正投影的交叠面积为s16,s16/s11大于等于0.2且小于等于1.1;所述g电极部的本体部在所述衬底基板上的正投影的面积为s13,所述g电极部的增设部在所述衬底基板上的正投影和所述电源线在所述衬底基板上的正投影的交叠面积为s17,s17/s13大于等于0.15且小于等于0.95;所述b电极部的本体部在所述衬底基板上的正投影的面积为s15,所述b电极部的增设部在所述衬底基板上的正投影和所述电源线在所述衬底基板上的正投影的交叠面积为s18,s18/s15大于等于0.05且小于等于0.4。

30、本公开一种示例性实施例中,所述显示面板包括沿行列方向分布的多个重复单元,每个所述重复单元包括两个像素驱动电路,两个所述像素驱动电路包括沿行方向分布的第一像素驱动电路和第二像素驱动电路,所述第一像素驱动电路和所述第二像素驱动电路镜像对称设置;所述像素驱动电路包括驱动晶体管、第四晶体管、第五晶体管,所述第四晶体管的第一极连接数据线,所述第四晶体管的第二极连接所述驱动晶体管的第一极,所述第五晶体管的第一极连接所述电源线,所述第五晶体管的第二极连接所述驱动晶体管的第一极;所述电源线在所述衬底基板上的正投影、所述数据线在所述衬底基板上的正投影均沿列方向延伸,每列所述像素驱动电路对应设置一条所述电源线和一条所述数据线;所述电源线包括:第一延伸部、第二延伸部、第三延伸部,所述第二延伸部连接于所述第一延伸部和所述第三延伸部之间;所述第二延伸部在所述衬底基板上的正投影在行方向上的尺寸大于第一延伸部在所述衬底基板上的正投影在行方向上的尺寸,且所述第二延伸部在所述衬底基板上的正投影在行方向上的尺寸大于所述第三延伸部在所述衬底基板上的正投影在行方向上的尺寸;在同一所述重复单元中,两条所述数据线在所述衬底基板上的正投影位于两条所述电源线在所述衬底基板上的正投影之间;在行方向上相邻所述重复单元中,相邻所述电源线的所述第二延伸部相连接;所述r电极部在所述衬底基板上的正投影和相连接的两所述第二延伸部在所述衬底基板上的正投影均交叠,所述b电极部在所述衬底基板上的正投影和相连接的两所述第二延伸部在所述衬底基板上的正投影均交叠,所述g电极部在所述衬底基板上的正投影和同一所述重复单元中两所述数据线在所述衬底基板上的正投影均交叠。

31、根据本公开的一个方面,提供一种显示装置,其中,该显示装置包括上述的显示面板。

32、本公开通过在电极部上设置增设部以增加电极部与电源线的交叠面积,从而增加了发光单元电极部的自身电容,进而延长了发光单元发光前的充电时长。即该设置可以减小发光单元在驱动晶体管电流输出不稳定时段发光的时长,从而该设置可以改善显示面板的闪烁问题。

33、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

- 还没有人留言评论。精彩留言会获得点赞!