一种GaN功放的供电时序控制系统及控制方法与流程

一种gan功放的供电时序控制系统及控制方法

技术领域

1.本发明涉及通信技术领域,尤其涉及一种gan功放的供电时序控制方法。

背景技术:

2.随着通信技术的深入发展,5g业务的逐步推广,通信频段已经从传统的3g扩展到6g,传统的ldmos功放已经很难满足高频段大带宽的需求,寻找新的半导体材料也就成了一个重要方向。

3.gan功放应运而生了。gan属于第三代高大禁带宽度的半导体材料,和第一代的si以及第二代的gaas等前辈相比,其在特性上优势突出。由于禁带宽度大、导热率高,gan器件可在200℃以上的高温下工作,能够承载更高的能量密度,可靠性更高;较大禁带宽度和绝缘破坏电场,使得器件导通电阻减少,有利于提升器件整体的能效;电子饱和速度快,以及较高的载流子迁移率,可让器件高速地工作。

4.因此,利用gan技术,人们可以获得具有更大带宽、更高放大器增益、更高能效、更高功率密度、尺寸更小的gan功放。

5.然而,由于gan功放对于上电时序比较苛刻,工作中上电时序问题或电路异常经常导致不可逆的功放损坏。

6.实现多通道功放控制对于带有标志位的负压发生芯片的带载能力,也提出了很大挑战,目前的一些时序管理芯片如ltc1261,难以满足工程实际需求,多载时负压易形成压降。

技术实现要素:

7.针对上述技术问题,本发明目的在于提供一种供电时序控制系统及控制方法,用来控制gan功放。

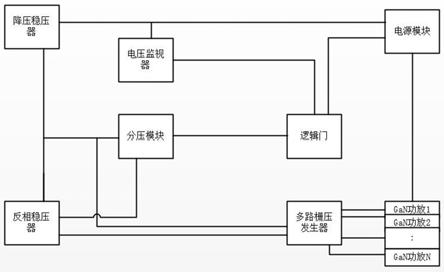

8.为了实现上述发明目的,本发明所采用的技术方案为:一种gan功放的供电时序控制系统,包括电源模块、降压稳压器、反相稳压器、逻辑门,多路栅压发生器,电压监视器、分压模块和gan功放,所述电源模块通过所述降压稳压器输出低电压给反相稳压器、逻辑门、电压监视器、分压模块和多路栅压发生器,所述电压监视器监视电源模块电压状态,根据电压状态输出高低电平给所述逻辑门;所述反相稳压器将正电压转为负电压,一端输出给所述分压模块,另一端通过多路栅压发生器给gan功放栅极供电;所述分压模块根据电平状态输出不同电平给所述逻辑门;所述逻辑门电路控制电源模块开关。

9.进一步的,反相稳压器生成的负电压既可直接用于gan功放的栅极电压,也可用于dac模块的供电。负电压需给分压模块供电促使分压模块产生可以控制三极管通断的高低电平。

10.进一步的,所述多路栅压发生器根据反相稳压器提供的负压产生多路可调节的负压,给多路gan功放栅极电压供电。

11.进一步的,所述电源模块给所述gan功放提供漏极电压。

12.本发明还提供了一种使用上述gan功放的供电时序控制系统的控制方法,包括如下步骤:步骤1:通过所述降压稳压器将电源模块的高电压转为低电压输出给反相稳压器、逻辑门、多路栅压发生器、电压监视器和分压模块;步骤2:通过所述反相稳压器将电源模块的正电压转为负电压,一端输出给所述分压模块,另一端给多路栅压发生器供电;步骤3:通过所述多路栅压发生器,提供给gan功放多路栅压;步骤4:所述分压模块根据电平状态输出不同电平给所述逻辑门;步骤5:通过所述电压监视器监测电源电压状态,当电源电压下降到一定阶段时,电压监视器输出高电平,正常状态下输出低电平;步骤6:所述分压模块输出的电平和所述电压监视器输出的电平通过所述逻辑门电路,控制电源模块开关的通断状态。

13.通过以上步骤,本系统能够实现上电时gan功放栅极电压先上电,漏极电压后上电,下电时栅极电压后下电,漏极电压先下电。电路异常时,gan功放漏极电压不上电。

14.与现有技术相比,本发明的有益效果为:1.现有技术中,电源电压突然降低,易导致gan的栅极电压比漏极电压先降,产生大电流。本系统通过电压检测器触发低电平,提前关闭功放,保护功放;2.现有技术中,想实现同样功能需要反相稳压器带有powergood功能,限制器件选型且价格较贵。本系统通过分压模块实时监测负压产生状态,控制功放开启或关闭,节省成本;3.通过选择带载能力强的反相稳压器,例如adp5074,驱动多路栅压发生器产生多路栅压,就可以实现多路,类如16路功放的控制。可以实现目前5g应用对应多通道的需求。

附图说明

15.图1为本实施例的一种gan功放的供电时序控制系统结构示意图。

16.图2为本实施例的一种gan功放的供电时序控制系统电路结构示意图。

17.图3为本实施例的电源电压28v,降压稳压器输出5v与反相稳压器-5v的上电时序图。

18.图4为本实施例的电源电压28v上电过程中的电压与电压监视器的输出电压对比图。

19.图5为本实施例的反相稳压器-5v,三极管基极和集电极电压对比图。

20.图6为本实施例的三极管输出(逻辑门输入a),电压监视器输出(逻辑门输入b)与逻辑门输出的逻辑图。

21.图7为本实施例的与门电路输出电压与功放漏极电压对比图。

22.图8为本实施例的gan功放漏极电压与gan功放栅极电压上电时序图。

23.图9为本实施例的功放下电时,电压监视器与电源电压,gan功放漏极电压对比图。

24.图10为本实施例的功放下电时,电源电压28v,5v,-5v电压掉电时序对比图。

25.图11为本实施例的gan功放下电时栅极电压与漏极电压时序图。

26.图12为本实施例的反相稳压器异常时系统时序图。

27.图13为本实施例的电压监视器异常时系统时序图。

28.图14为本实施例的三极管或逻辑门异常时系统时序图。

29.图15为本实施例的一种gan功放的供电时序控制系统工作时序图。

具体实施方式

30.为了便于本领域技术人员的理解,下面结合说明书附图和具体实施例对本发明作进一步的说明。

31.如图1所示,本实施例的一种gan功放的供电时序控制系统结构示意图,包括电源模块、降压稳压器、反相稳压器、逻辑门,多路栅压发生器,电压监视器、分压模块和gan功放,所述电源模块通过所述降压稳压器输出低电压给反相稳压器、逻辑门、电压监视器、分压模块和多路栅压发生器,所述电压监视器监视电源模块电压状态,根据电压状态输出高低电平给所述逻辑门;所述反相稳压器将正电压转为负电压,一端输出给所述分压模块,另一端通过多路栅压发生器给gan功放栅极供电;所述分压模块根据电平状态输出不同电平给所述逻辑门;所述逻辑门电路控制电源模块开关。

32.如图2所示,本实施例的一种gan功放的供电时序控制系统电路结构示意图:3.5ghz工作频段的4通道gan功放设计,通过本文中提到的方法,进行了时序控制。

33.q2为gan功放,功放的漏极电压28v通过m2 mos管的开启与关闭控制;mos是mosfet的缩写,简称金氧半场效晶体管;具体控制过程如下:步骤1:降压稳压器u3将电源电压28v降为5v,给反相稳压器u1,逻辑门u4,电压监视器u6和三极管q1供电;步骤2:反相稳压器u1将5v转化为负压,例如-5v,给gan功放q2 的栅极供电;步骤3:电压监视器u6监测28v电源电压并根据不同状态输出不同电平;当电压大于设定值时输出高电平5v;步骤4:三极管q1实时监测负压产生状态,当负压低于一定值时,三极管基极电压小于0.6v,源极输出高电平5v;步骤5:逻辑门u4与门逻辑芯片结合三极管q1和电压监视器u6输出电平状态输出相应电平;步骤6:mos管m1,m2根据逻辑门u4与门逻辑芯片输出电压状态控制28v电源电压的开启与关闭。

34.gan功放主要关注上电和下电时栅极和漏极的上下电顺序,以及使用过程中某些器件的损坏是否会导致上电时序异常。

35.上电时:开启28v电源电压,伴随着电压逐渐提升,降压稳压器u3输出电压逐渐产生并稳定至5v,随着5v电压的逐渐稳定,反相稳压器u1输出的-5v电压也逐渐稳定,如图3所示。当电源电压提升至一定值时,电压监视器u6输出电平由0电平提升至5v,如图4所示。当-5v逐渐降低时,分压电阻提供给三极管q1基极的输入电平逐渐小于其导通电压,导致三极管q1不导通,三极管q1集电极电压由0v逐渐提升至5v,如图5所示。当电压监视器u6输出电平和三极管q1集电极电压都提升至2.5v以上时,逻辑门u4与门逻辑芯片输出高电平,如图6所示。当逻辑门u4与门逻辑芯片输出高电平时,m1 mos管漏极输出低电平控制m2 mos管导

通,28v电源电压通过m2 mos管给gan功放q2提供漏极电压,如图7所示。gan功放q2上电需满足栅极电压先于漏极电压上电,本电路满足此要求,如图8所示。

36.下电时:关闭28v电源电压,当电源电压降低至一定值时,电压监视器u6输出电平由5v电平降低至0v,导致逻辑门u4与门逻辑芯片输出低电平0v,间接导致m2 mos管关闭,gan功放q2漏极逐渐降低至0电平,如图9所示。当电源电压降低至一定值时,降压稳压器u3不再产生5v电压,间接导致反相稳压器u1也不在产生-5v电压。 gan功放q2栅极电压关闭,如图10所示。 gan功放q2的漏极电压先于栅极电压关闭,满足gan功放下电顺序,保证功放不被烧毁,如图11所示。

37.使用过程中,可能会遇到如下几种异常:1.反相稳压器u1芯片异常,当u1芯片异常时,-5v不产生,导致逻辑门u4与门逻辑芯片不输出高电平,导致m2 mos管关闭, gan功放q2漏极电压关闭,保护了功放,如图12所示。

38.2.电压监视器u6芯片异常,当u6芯片异常时,电压监测模块不产生高电平,导致逻辑门u4与门逻辑芯片不输出高电平,导致m2 mos管关闭, gan功放q2漏极电压关闭,保护了功放,如图13所示;3.三极管q1芯片异常,当q1异常时,导致逻辑门u4与门逻辑芯片不输出高电平,导致m2 mos管关闭,gan功放q2 漏极电压关闭,保护了功放,如图14所示;4.逻辑门u4与门逻辑芯片异常,导致逻辑门u4与门逻辑芯片不输出高电平,导致m2 mos管关闭, gan功放q2漏极电压关闭,保护了功放,如图14所示。

39.综上述分析,此系统上下电时序(如图15),栅极电压先上电后掉电,满足gan功放的使用的时序需求,且十分安全,极大的避免了由于上下电时序问题导致功放的损坏。

40.以上所述仅为本发明的优选实例而已,并不用于限制本发明,对于本领域的技术人员而言,本发明可以有各种变化和更改。凡是在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1