一种高Q值单晶薄膜体声波谐振器的制备方法

一种高q值单晶薄膜体声波谐振器的制备方法

技术领域

1.本发明涉及薄膜体声波谐振器,具体涉及一种高q值单晶薄膜体声波谐振器的制备方法。

背景技术:

2.随着无线移动通讯技术的快速发展,体声波器件应用领域越来越广泛。而具有插入损耗低、频带宽、品质因子高等优点的薄膜体声波谐振器逐渐占领市场。目前薄膜体声波谐振器使用的压电薄膜材料大多采用磁控溅射技术制备的多晶氮化物薄膜,薄膜质量较差,缺陷密度较高,无法满足未来移动通讯技术更低的插入损耗、更高的带宽等要求。单晶压电薄膜体声波谐振器不仅具有较高的频率,且部分性能优于传统压电薄膜材料的薄膜体声波谐振器,近年来得到学术界和产业界的高度关注。但为适应未来更高的移动通讯技术要求,突破现有局限制备出具有更高频率和q值的单晶压电薄膜体声波谐振器仍是人们不断追求的目标。

技术实现要素:

3.本发明的目的是针对现有技术的不足,提供一种高q值单晶薄膜体声波谐振器的制备方法。

4.本发明一种高q值单晶薄膜体声波谐振器的制备方法,具体步骤如下:

5.s1:对衬底和基底均进行超声水洗;在衬底的一侧表面沉积剥离层,然后在剥离层上沉积压电层;在基底的一侧表面淀积待键合层一。

6.s2:在压电层表面沉积金属并图形化,形成下电极;在下电极表面沉积金属并图形化,形成下环形结构一;或形成下环形结构一和下环形结构二,下环形结构二置于下环形结构一内,且两者间距设置。

7.s3:在下电极表面沉积钝化层一;只有下环形结构一时,在下环形结构一表面沉积钝化层二;有下环形结构一和下环形结构二时,在下环形结构一和下环形结构二表面沉积钝化层二;然后,在下电极表面通过淀积和图形化,只有下环形结构一时,形成包裹钝化层二和下环形结构一的牺牲层,有下环形结构一和下环形结构二时,形成包裹钝化层二、下环形结构一和下环形结构二的牺牲层;然后,在压电层表面沉积包裹牺牲层和下电极的保护层;最后,在压电层表面淀积包裹保护层的待键合层二,并对待键合层二表面进行平整化。

8.s4:将基底上的待键合层一与待键合层二通过键合工艺连接;然后,去除衬底,并对压电层表面进行平整化。

9.s5:在压电层表面沉积金属并图形化,形成上电极;然后,在上电极表面沉积钝化层三。

10.s6:采用等离子刻蚀或湿法腐蚀工艺将上电极以外的压电层减薄。

11.s7:采用等离子刻蚀或湿法腐蚀工艺在压电层上形成通孔,通孔贯穿下电极和钝化层一,底部开口于牺牲层表面;然后,通过湿法腐蚀工艺或干法腐蚀工艺利用通孔去除牺

牲层,从而在钝化层一和保护层之间形成空腔。

12.优选地,步骤s5和步骤s6之间还有如下步骤:在钝化层三表面沉积金属并图形化,形成上环形结构。

13.优选地,所述压电层的材料为单晶氮化铝、多晶氮化铝、氧化锌、单晶钽酸锂、锆钛酸铅、铌酸锂中的一种或多种按任意配比组合,厚度为10nm-4000nm。

14.优选地,所述待键合层一和待键合层二的材料均为氧化硅、硅中的一种或两种按任意配比组合,厚度均为0.1-10μm。

15.优选地,所述下电极的厚度为50nm-500nm,横向宽度为30-600μm。

16.优选地,所述下电极、下环形结构一、下环形结构二和上电极的材料相同,均为铜、铝、银、钛、钨、金、镍、钼中的一种或多种按任意配比组合。

17.优选地,所述下环形结构一和下环形结构二的厚度均为20nm-300nm,横向宽度均大于0μm且小于10μm。

18.优选地,所述上环形结构的材料为铜、铝、银、钛、钨、金、镍、钼中的一种或多种按任意配比组合。

19.优选地,所述通孔的直径在5um-50um范围内取值。

20.本发明具有的有益效果:

21.本发明在谐振器的下电极上设置下环形结构一和下环形结构二,在下电极上设置钝化层一,在下环形结构一和下环形结构二上设置钝化层二,在上电极上设置钝化层三,将压电层边缘区减薄,优化了谐振器的主谐振声波的泄露问题,将声波能量限制在谐振器中,减少泄露,提升谐振器的q值。

附图说明

22.图1本发明在衬底上制备剥离层并在剥离层上制备压电层的剖面图。

23.图2是在基底上制备待键合层一的剖面图。

24.图3是在图1结构上制备下电极的剖面图。

25.图4是在图3结构上制备下环形结构一和下环形结构二的剖面图。

26.图5是在图4结构上制备钝化层一和钝化层二的剖面图。

27.图6是在图5结构上制备牺牲层的剖面图。

28.图7是在图6结构上制备保护层的剖面图。

29.图8是在图7结构上制备待键合层二并进行化学机械研磨处理的剖面图。

30.图9是图2结构与图8结构经键合成型的剖面图。

31.图10是在图9结构上去除剥离层和衬底的剖面图。

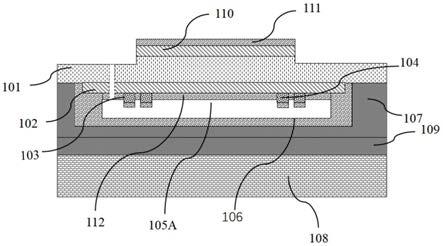

32.图11是在图10结构上制备上电极并在上电极上制备钝化层三的剖面图。

33.图12是在图11结构上减薄压电层边缘的剖面图。

34.图13是在图12结构上制备通孔的剖面图。

35.图14是本发明采用具体的一组结构尺寸但压电层未减薄时是否采用下环形结构一和下环形结构二的谐振器阻抗曲线图。

36.图15是本发明采用具体的一组结构尺寸但压电层未减薄时是否采用下环形结构一和下环形结构二的谐振器相位曲线图。

37.图16是本发明采用具体的一组结构尺寸时压电层未减薄且不采用下环形结构一和下环形结构二、压电层未减薄但采用下环形结构一和下环形结构二以及压电层减薄且采用下环形结构一和下环形结构二的谐振器工作在串联谐振频率点的位移对比图。

38.图17是本发明实施例2的谐振器结构剖面图。

39.图18是本发明实施例3的谐振器结构剖面图。

40.图19是本发明实施例4的谐振器结构剖面图。

具体实施方式

41.下面结合附图对本发明作进一步说明。

42.实施例1:

43.一种高q值单晶薄膜体声波谐振器的制备方法,具体步骤如下:

44.(1)对衬底100和基底108均使用丙酮和异丙醇进行超声水洗;衬底和基底的材料为玻璃、硅、碳化硅、氮化硅或陶瓷中的一种或多种按任意配比组合。

45.(2)如图1所示,在衬底100的一侧表面用金属有机化合物化学气相沉淀工艺(mocvd)沉积剥离层114;剥离层114的材料为gan;然后在剥离层114上制备(可以采用金属有机化合物化学气相沉淀工艺沉积)压电层101,厚度为10nm-4000nm。

46.(3)如图2所示,在基底108的一侧表面采用低压化学气相淀积工艺(lpcvd)淀积待键合层一109,并采用化学机械研磨的方式使待键合层一109表面平整,待键合层一109的材料为氧化硅、硅中的一种或两种按任意配比组合,厚度为0.1-10μm。

47.(4)如图3所示,在压电层101表面采用热蒸发或磁控溅射的方法沉积金属,并采用等离子体或湿法腐蚀的方法进行图形化,形成下电极102,下电极102的横向宽度为30-600μm。

48.(5)如图4所示,在下电极102表面采用热蒸发或磁控溅射的方法沉积金属,并采用等离子体或湿法腐蚀的方法进行图形化,形成下环形结构一103和下环形结构二104;下环形结构二104置于下环形结构一103内,且两者间距设置;

49.(6)如图5所示,用金属有机化合物化学气相沉淀工艺在下电极102表面沉积钝化层一112,在下环形结构一103和下环形结构二104表面沉积钝化层二113;

50.(7)如图6所示,在钝化层一112表面采用等离子体化学气相淀积工艺淀积多晶硅或非晶硅,并采用等离子体或湿法腐蚀的方法进行图形化,形成包裹钝化层二113、下环形结构一103和下环形结构二104的牺牲层105。

51.(8)如图7所示,在压电层101表面用金属有机化合物化学气相沉淀工艺沉积包裹牺牲层105和下电极102的保护层106。

52.(9)如图8所示,在压电层101表面采用低压化学气相淀积工艺(lpcvd)淀积包裹保护层106的待键合层二107,并采用化学机械研磨的方式使待键合层二107表面平整,待键合层二107的材料为氧化硅、硅中的一种或两种按任意配比组合。

53.(10)如图9所示,将基底108上的待键合层一109与待键合层二107贴合,并通过键合工艺连接,使得待键合层一109与待键合层二107形成致密的界面。

54.(11)如图10所示,采用激光剥离技术去除剥离层114和衬底100,并对压电层101表面进行平整化。

55.(12)如图11所示,在压电层101表面采用热蒸发或磁控溅射的方法沉积金属,并采用等离子体或湿法腐蚀的方法进行图形化,形成上电极110;然后,在上电极110表面用金属有机化合物化学气相沉淀工艺沉积钝化层三111;

56.(13)如图12所示,采用等离子刻蚀或湿法腐蚀工艺将上电极110以外的压电层101减薄。

57.(14)如图13所示,采用等离子刻蚀或湿法腐蚀工艺在压电层101上形成通孔;通孔贯穿下电极102和钝化层一112,底部开口于牺牲层105表面;通孔的直径在5um-50um范围内取值。然后,通过湿法腐蚀工艺或干法腐蚀工艺利用通孔去除牺牲层105,从而在钝化层一112和保护层106之间形成空腔105a。

58.下面给出具体的一组结构尺寸:

59.基底108(采用si),厚度为500μm,宽度为200μm;待键合层一和待键合层二(采用si)的厚度均为5μm,宽度为200μm;保护层(采用aln)厚度为50nm,横向宽度为180μm;下电极(采用mo)厚度为170nm,横向宽度为170μm;压电层(采用aln)厚度为650nm,横向宽度为180μm;压电层减薄部分深度为175nm,横向宽度为37.5μm;上电极(采用mo)厚度为150nm,横向宽度为100μm;钝化层一112和钝化层二113(采用aln)的厚度为30nm,钝化层一112和钝化层二113总的横向宽度为170μm;钝化层三111(采用aln)的厚度为50nm,横向宽度为100μm;空腔厚度为2μm,横向宽度为160um。

60.将采用上述具体的一组结构尺寸但压电层不减薄且不使用下环形结构一103和下环形结构二104的结构时,以及采用上述具体的一组结构尺寸但压电层不减薄且下环形结构一103和下环形结构二104的厚度和横向宽度变化时,谐振器的串联谐振频率处的q值(qs)和并联谐振频率处的q值(qp)变化情况列在表1中。

61.表1

[0062][0063][0064]

从表1可见,当压电层不减薄,下环形结构一103的厚度110nm,横向宽度3182nm,下环形结构二104的厚度为45nm,横向宽度为2367nm时,与压电层不减薄且不使用下环形结构一103和下环形结构二104的情况对比,qp从664提升到1460,qs从1525提升到1540。

[0065]

采用上述具体的一组结构尺寸,绘出压电层不减薄,下环形结构一103的厚度110nm,横向宽度3182nm,下环形结构二104的厚度为45nm,横向宽度为2367nm时与压电层不减薄且不使用下环形结构一103和下环形结构二104时的阻抗曲线和相位曲线对比图,分别如图14和15所示,可以看到,在串联谐振频率处和并联谐振频率处之间寄生减少,达到了更好的谐振器性能。

[0066]

绘出采用上述具体的一组结构尺寸但压电层不减薄且不使用下环形结构一103和下环形结构二104的结构,采用上述具体的一组结构尺寸但压电层不减薄、下环形结构一103的厚度110nm、横向宽度3182nm、下环形结构二104的厚度为45nm、横向宽度为2367nm,以及采用上述具体的一组结构尺寸且压电层不减薄、下环形结构一103的厚度110nm、横向宽度3182nm、下环形结构二104的厚度为45nm、横向宽度为2367nm时谐振器工作在串联谐振频率点时的位移对比图,即整个谐振器上表面在工作时的振动大小,如图16所示,可明显观察到随着下电极使用下环形结构一103和下环形结构二104,边缘区相比于有效区的位移比不

使用下环形结构一103和下环形结构二104的谐振器更小,下电极使用下环形结构一103和下环形结构二104时有效区向边缘区的能量泄漏较少,能量更集中在有效区,直接表现为并联谐振频率处的q值提高。在下电极使用下环形结构一103和下环形结构二104的基础上将压电层边缘区减薄一部分(深度175nm,宽度37.5um),发现有效区向边缘区的能量泄漏更少,能量更集中在有效区,qp从1460提升到1587,qs从1540提升到1632。

[0067]

本发明在谐振器的下电极上设置下环形结构一103和下环形结构二104,在下电极上设置钝化层一112,在下环形结构一103和下环形结构二104上设置钝化层二113,在上电极上设置钝化层三,将压电层边缘区减减薄,这些结构改进共同优化了谐振器的主谐振声波的泄露问题,将声波能量限制在谐振器中,减少泄露,提升谐振器的q值。

[0068]

实施例2:

[0069]

一种高q值单晶薄膜体声波谐振器的制备方法,在实施例1的步骤(1)至步骤(12)基础上,进行如下步骤:

[0070]

(13)如图17所示,在钝化层三111表面采用热蒸发或磁控溅射的方法沉积金属,并采用等离子体或湿法腐蚀的方法进行图形化,形成上环形结构115;

[0071]

(14)如图17所示,采用等离子刻蚀或湿法腐蚀工艺将上电极110以外的压电层101减薄。

[0072]

(15)如图17所示,采用等离子刻蚀或湿法腐蚀工艺在压电层101上形成通孔;通孔贯穿下电极102和钝化层一112,底部开口于牺牲层105表面;通孔的直径在5um-50um范围内取值。然后,通过湿法腐蚀工艺或干法腐蚀工艺利用通孔去除牺牲层105,从而在钝化层一112和保护层106之间形成空腔105a。

[0073]

实施例3:

[0074]

本实施例一种高q值单晶薄膜体声波谐振器的制备方法,如图18所示,与实施例1的不同之处在于,步骤(5)只形成下环形结构一103,未形成下环形结构二104;步骤(6)只在下电极102表面沉积钝化层一112以及下环形结构一103表面沉积钝化层二113;步骤(7)牺牲层105包裹钝化层二113和下环形结构一103。

[0075]

实施例4:

[0076]

一种高q值单晶薄膜体声波谐振器的制备方法,在实施例3的步骤(1)至步骤(12)基础上,进行如下步骤:

[0077]

(13)如图19所示,在钝化层三111表面采用热蒸发或磁控溅射的方法沉积金属,并采用等离子体或湿法腐蚀的方法进行图形化,形成上环形结构115;

[0078]

(14)如图19所示,采用等离子刻蚀或湿法腐蚀工艺将上电极110以外的压电层101减薄。

[0079]

(15)如图19所示,采用等离子刻蚀或湿法腐蚀工艺在压电层101上形成通孔;通孔贯穿下电极102和钝化层一112,底部开口于牺牲层105表面;通孔的直径在5um-50um范围内取值。然后,通过湿法腐蚀工艺或干法腐蚀工艺利用通孔去除牺牲层105,从而在钝化层一112和保护层106之间形成空腔105a。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1