一种放大电路及射频芯片的制作方法

1.本技术涉及电子领域,特别涉及一种放大电路及射频芯片。

背景技术:

2.随着信息技术的发展,无线电通信技术已渗透于人们日常生活的方方面面,各种无线电通信标准相继出现,不同标准不同应用往往覆盖多种频带,为支撑不同应用,多功能小型化终端的出现成为必然,因此研制具有宽频带可配置功能的射频收发机芯片成为趋势。

3.放大电路是构成射频接收机的重要部分,传统的放大电路在接收放大有用信号的同时,也会放大带外的干扰信号,而在极端情况下,相邻工作频带强大的干扰信号会导致低噪声放大器的饱和,整体接收机性能将严重恶化。为保证接收机能够正常工作,除了放大电路自身线性度之外,如何提升抗干扰性能成为关键。亟需设计一种具有高带外抑制能力的放大电路。

技术实现要素:

4.本技术提供了一种放大电路及射频芯片,以提高放大电路的带外抑制能力即抗干扰能力。

5.第一方面,本技术提供了一种放大电路,包括:低噪声放大器、第一反馈电路、负载阻抗电路;负载阻抗电路的第一端与低噪声放大器的第一输出端耦合,负载阻抗电路的第二端与低噪声放大器的第二输出端耦合,其中,负载阻抗电路包括并联的多个谐振电路,每个谐振电路分别覆盖不同频段;第一反馈电路包括第一电容和第二电容;第一电容的第一端与第一输出端耦合,第一电容的第二端与低噪声放大器的第一输入端耦合;第二电容第一端与第二输出端耦合,第二电容第二端与低噪声放大器的第二输入端耦合。

6.在一些可能的实施方式中,低噪声放大器包括第一晶体管和第二晶体管;第一输入端与第一晶体管的源极耦合,第一输出端与第一晶体管的漏极耦合;第二输入端与第二晶体管的源极耦合,第二输出端与第二晶体管的漏极耦合;第一晶体管的栅极与第一电容的第二端耦合;第二晶体管的栅极与第二电容的第二端耦合。

7.在一些可能的实施方式中,低噪声放大器还包括:共栅的第三晶体管和第四晶体管,以及第三电容和第四电容;第一输出端与第三晶体管的漏极耦合,第二输出端与第四晶体管的漏极耦合;第一晶体管的漏极与第三晶体管的源极耦合,第二晶体管的漏极与第四晶体管的源极耦合;第三电容的第一端与第一晶体管的源极耦合,第三电容的第二端与第二晶体管的栅极耦合,第四电容的第一端与第一晶体管的栅极耦合,第四电容的第二端与第二晶体管的源极耦合。

8.在一些可能的实施方式中,第一晶体管、第二晶体管、第三晶体管和第四晶体管为nmos管。

9.在一些可能的实施方式中,每个谐振电路,包括:并联的第一电感与反馈电容网

络,其中,反馈电容网络能够根据不同的控制信号配置不同的电容值。

10.在一些可能的实施方式中,反馈电容网络,包括:并联的压控可变电容与选通电容阵列;其中,压控可变电容的电容值能够通过输入电压控制;选通电容阵列,包括:选通电路以及n个反馈电容,n的取值为大于或者等于2的整数;其中,选通电路被配置为接收控制信号,并根据控制信号选通n个反馈电容中的至少一部分反馈电容。

11.在一些可能的实施方式中,选通电路,包括:n个开关,每个开关的第一端与第一输出端连接,每个开关的第二端与每个反馈电容的第一端连接,每个反馈电容的第二端与第二输出端连接。

12.在一些可能的实施方式中,每个反馈电容的电容值均相同;或,每个反馈电容的电容值均不同。

13.第二方面,本技术提供一种射频芯片,包括如第一方面极其可能的实施方式中任一项放大电路。

14.本技术提供的技术方案与现有技术相比存在的有益效果是:

15.在本技术中,通过第一反馈电路将负载阻抗电路的阻抗反馈至低噪声放大器,使低噪声放大器具有一定的带外抑制能力,并且进一步降低低噪声放大器的输入噪声贡献,同步提高输入匹配和噪声性能;另外,多个谐振电路并联覆盖多个频段,从而实现宽带特性。选通电容阵列实现谐振频路粗调节,压控可变电容实现谐振频路细调节,当放大电路工作在不同频点时,可以通过调节谐振电路及其内部反馈电容网络选择合适的负载阻抗,且阻抗特性通过第一反馈电路反馈到低噪声放大器输入端,提高放大电路的带外抑制即抗干扰能力。

16.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术的保护范围。

附图说明

17.图1为本技术实施例中的一种放大电路的示意图;

18.图2为本技术实施例中的一种低噪声放大器示意图;

19.图3为本技术实施例中的另一种低噪声放大器的示意图;

20.图4为本技术实施例中的一种谐振电路的示意图;

21.图5为本技术实施例中的一种反馈电容网络的示意图;

22.图6为本技术实施例中的一种选通电路示意图;

23.图7为本技术实施例中的一种放大电路的示意图;

24.图8为本技术实施例中的一种放大电路的单端电路示意图;

25.图9为本技术实施例中的以三组并联谐振电路为例的放大电路的仿真效果图。

具体实施方式

26.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

27.为了说明本技术所述的技术方案,下面通过具体实施例来进行说明。

28.无线电通信(radio communications)是将需要传送的声音、文字、数据、图像等电信号调制在无线电波上经空间和地面传至目标接收端,利用无线电磁波在空间传输信息的通信方式。目标接收端的射频收发机接收无线电信号,从中选出需要的信号再转换为声音、图像、电码等信息。射频接收机被广泛地运用在车辆监控、遥控、遥测、小型无线网络、工业数据采集系统、小型无线数据终端、安全防火系统、无线遥控系统、生物信号采集、水文气象监控、数据通信、数字音频以及数字图像传输等诸多领域中。

29.放大电路是构成射频接收机的重要部分,传统的放大电路在接收放大有用信号的同时,也会放大带外的干扰信号,而在极端情况下,相邻工作频带强大的干扰信号会导致低噪声放大器的饱和,整体接收机性能将严重恶化。

30.为解决上述问题,本技术实施例提供一种放大电路,该放大电路可以应用于具有通信功能的电子设备中。电子设备可以包括终端设备,终端设备也可以称为终端(terminal)、用户设备(userequipment,ue)、移动台(mobile station,ms)、移动终端(mobile terminal,mt)等。终端设备可以是手机(mobile phone)、智能电视、穿戴式设备、平板电脑(pad)、带无线收发功能的电脑、虚拟现实(virtual reality,vr)终端设备、增强现实(augmented reality,ar)终端设备、工业控制(industrial control)中的无线终端、无人驾驶(self-driving)中的无线终端、远程手术(remote medical surgery)中的无线终端、智能电网(smart grid)中的无线终端、运输安全(transportation safety)中的无线终端、智慧城市(smart city)中的无线终端、智慧家庭(smart home)中的无线终端等等。

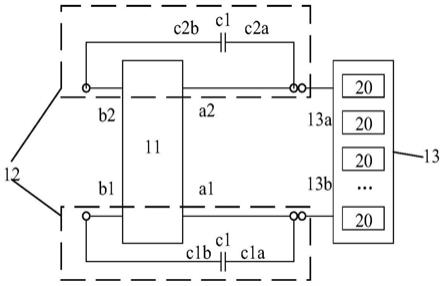

31.图1为本技术实施例中的一种放大电路的示意图,参见图1所示,该放大电路可以包括:低噪声放大器11、第一反馈电路12以及负载阻抗电路13。

32.在一些可能的实施例中,低噪声放大器可以包括第一输出端a1和第二输出端a2以及第一输入端b1和第二输入端b2,第一输入端b1和第二输入端b2用于接收待放大信号,将待放大信号进行放大后经第一输出端a1与第二输出端a2输出。负载阻抗电路13的第一端13a与低噪声放大器11的第一输出端a1耦合,负载阻抗电路13的第二端13b与低噪声放大器的第二输出端a2耦合。第一反馈电路12包括第一电容c1和第二电容c2;第一电容c1的第一端c1a与第一输出端a1耦合,第一电容c1的第二端c1b与低噪声放大器11的第一输入端b1耦合;第二电容c2第一端c2a与第二输出端a2耦合,第二电容c2第二端c2b与低噪声放大器11的第二输入端b2耦合。

33.首先,介绍低噪声放大器的一些可能的实施方式。

34.在一些可能的实施方式中,上述低噪声放大器可以由图2所示的低噪声放大器实现,图2为本技术实施例中的一种低噪声放大器示意图,参见图2所示,上述低噪声放大器11可以包括:第一晶体管m1和第二晶体管m2,第一输入端b1与第一晶体管m1的源极耦合,第一输出端a1与第一晶体管m1的漏极耦合;第二输入端b2与第二晶体管m2的源极耦合,第二输出端a2与第二晶体管m2的漏极耦合;第一晶体管m1的栅极与第一电容c1的第二端c1b耦合;第二晶体管m2的栅极与第二电容c2的第二端c2b耦合。

35.可以理解的,当晶体管为偏置状态时,晶体管m

1与

m2的栅极与源极处于导通状态,此时,所述放大电路处于工作状态,第一反馈电路12可将负载阻抗13的阻抗特性经晶体管的栅极反馈至低噪声放大器11的输入端,能够提升低噪声放大器11的带外抑制能力,进而提

升低噪声放大器11的抗干扰能力。将待放大信号经第一输入端与第二输入端输入低噪声放大器11,由低噪声放大器对射频输入信号进行放大后通过差分输出端进行输出。其中,可以采用提供外部偏置电压的方式为所述晶体管提供偏置,也可采用自稳定偏置晶体管,本技术实施例对此不作限定。

36.可选的,晶体管m1与m2可以是nmos管,也可以是其他具有放大功能的场效应管。

37.在一些可能的实施方式中,低噪声放大器还可以由如图3所示的低噪声放大器实现,图3为本技术实施例中的另一种低噪声放大器的示意图,参见图3所示,低噪声放大器11还可以包括:共栅的第三晶体管m3和第四晶体管m4,以及第三电容c3和第四电容c4;第一输出端a1与第三晶体管m3的漏极耦合,第二输出端a2与第四晶体管m4的漏极耦合;第一晶体管m1的漏极与第三晶体管m3的源极耦合,第二晶体管m2的漏极与第四晶体管m4的源极耦合;第三电容c3的第一端c3a与第一晶体管m1的源极耦合,第三电容c3的第二端c3b与第二晶体管m2的栅极耦合,第四电容c4的第一端c4a与第一晶体管m1的栅极耦合,第四电容c4的第二端c4b与第二晶体管m2的源极耦合。

38.可以理解的,上述晶体管m3和m4可以是如晶体管m1和m2相同的nmos管或其他场效应管。当晶体管m1、m2、m3以及m4均位于偏置状态时,放大电路处于工作状态。当待放大信号经第一输入端b1与第二输入端b2输入低噪声放大器11时,低噪声放大器11在电容c3和电容c4的共同作用下,可以极大降低除待放大信号以外的噪声贡献。同时,第一反馈电路12可以将负载阻抗13的阻抗特性经晶体管的栅极反馈至低噪声放大器11的输入端,能够提升低噪声放大器11的带外抑制能力,进一步提升低噪声放大器11的抗干扰能力。待放大信号经低噪声放大器11进行放大后,经第一输出端a1与第二输出端a2输出。其中,可以采用提供外部偏置电压的方式为上述各晶体管提供偏置,也可以采用自稳定偏置晶体管,本技术实施例对此不作限定。

39.进一步的,介绍负载阻抗电路13的一些可能的实施方式。

40.在一实施例中,负载阻抗电路13可以包括并联的多个谐振电路20,每个谐振电路20分别覆盖不同频段。

41.可以理解的,当低噪声放大器11工作在不同频段时,可以通过选择负载阻抗电路13中的不同频段的谐振电路20选择合适的负载阻抗。上述多个谐振电路20可以是谐振频率设置固定值,各谐振电路20设置不同的谐振频率覆盖不同频段,也可以是通过各谐振电路分别调节谐振频率以覆盖不同频段。

42.在一些可能的实施方式中,图4为本技术实施例中一种谐振电路的示意图,参见图4所示,上述每个谐振电路20可以包括:并联的第一电感l1与反馈电容网络40,其中,反馈电容网络40被配置为根据低噪声放大器的不同频段的工作值配置不同的电容值,进而实现调节谐振电路的谐振频率。

43.可以理解的,反馈电容网络40可以由多个反馈电容组成,其中,多个反馈电容可以是并联的,也可以是串并联混合的。当然,反馈电容网络40中的反馈电容还可以采用任意的组合方式,本技术实施例对此不作具体限定。

44.可选的,反馈电容网络40中各个反馈电容的电容值可以为相同,或者,反馈电容网络40中各个反馈电容的电容值也可以不同。如此,反馈电容网络40通过选通不同的反馈电容,以配置反馈电容网络的电容值。

45.优选的,每一个反馈电容的电容值可以均不相同,呈梯度递增或者递减,以进一步扩展跨阻放大器的带宽,提升跨阻放大器的检测性能。

46.在一些可能的实施方式中,图5为本技术实施例中一种反馈电容网络的示意图,参见图5所示,上述反馈电容网络40,包括:并联的压控可变电容cv与选通电容阵列50;其中,压控可变电容cv的电容值可以通过输入电压控制。选通电容阵列50可以包括:选通电路51以及n个反馈电容52(可以记为c1、c2、

…

、ci…

、cn,i大于或者等于1且小于或者等于n),n的取值为大于或者等于2的整数。

47.在一些可能的实施方式中,上述选通电路51可以被配置为:根据低噪声放大器11所处工作频段,选通n个反馈电容中的至少一部分反馈电容。示例性的,反馈电容网络包括3个反馈电容,如c1、c2和c3。若选通电路51选通其中的c1,此时,反馈电容网络40的电容值即为c1的电容值。若选通电路51根据控制信号选通其中的c1、c2,此时,反馈电容网络40的电容值即为c1、c2的等效电容值,如c1、c2的电容值之和。

48.在本技术实施例中,选通电路可以存在以下实现方式。图6为本技术实施例中的一种选通电路示意图,参见图6所示,选通电路51可以包括k个开关61(可以记为k1、k2、

…

、ki…

、kn),k小于或者等于n。每个开关61的第一端kia与第一输出端a1连接,每个开关61的第二端kib与每个反馈电容52的第一端连接,每个反馈电容52的第二端与第二输出端a2连接。示例性的,开关61可以为单刀单掷开关。

49.下面以具体实施例来对上述放大电路进行说明。

50.图7为本技术实施例中的一种放大电路的示意图,参见图7所示,放大电路可以包括:低噪声放大器11、第一反馈电路12以及负载阻抗电路13。其中,第一反馈电路12可以包括第一电容c1和第二电容c2;第一电容c1的第一端c1a与第一输出端a1耦合,第一电容c1的第二端c1b与低噪声放大器11的第一输入端b1耦合;第二电容c2第一端c2a与第二输出端a2耦合,第二电容c2第二端c2b与低噪声放大器11的第二输入端b2耦合。低噪声放大器11可以包括:第一晶体管m1和第二晶体管m2、共栅的第三晶体管m3和第四晶体管m4,以及第三电容c3和第四电容c4。第一输出端a1与第三晶体管m3的漏极耦合,第二输出端a2与第四晶体管m4的漏极耦合;第一晶体管m1的漏极与第三晶体管m3的源极耦合,第二晶体管m2的漏极与第四晶体管m4的源极耦合;第三电容c3的第一端c3a与第一晶体管m1的源极耦合,第三电容c3的第二端c3b与第二晶体管m2的栅极耦合,第四电容c4的第一端c4a与第一晶体管m1的栅极耦合,第四电容c4的第二端c4b与第二晶体管m2的源极耦合。负载阻抗电路13的第一端13a与低噪声放大器11的第一输出端a1耦合,负载阻抗电路13的第二端13b与低噪声放大器的第二输出端a2耦合。负载阻抗电路13可以由多个并联的谐振电路20组成。如图7所示,以三组并联的谐振电路20为例,每个谐振电路20可以包括:并联的第一电感l1与反馈电容网络40,反馈电容网络40,包括:并联的压控可变电容cv、反馈电容(如c1、c2和c3),开关(如k1、k2、和k3)。其中,c1、c2和c3并联,k1和c1串联,k2和c2串联,k3和c3串联。

51.可以理解的,当晶体管m1、m2、m3和m4位于偏置状态时,放大电路处于工作状态,待放大信号可以通过第噪声放大器的第一输入端b1和第二输入端b2输入。根据低噪声放大器11所处工作频段控制开关ki。此时,第一反馈电路12通过第一电容c1和第二电容c2,将负载阻抗电路13的阻抗特性反馈至低噪声放大器的第一输入端b1和第二输入端b2,用于提高低噪声放大器11的带外抑制能力,进而提升低噪声放大器11的抗干扰能力。同时,低噪声放大

器11在第三电容c3和第四电容c4的共同作用下,进一步降低除待放大信号以外的噪声贡献。待放大信号经低噪声放大器11进行放大后,经第一输出端a1与第二输出端a2输出。

52.图8为本技术实施例中的一种放大电路的单端电路示意图;

53.参见图8,图中第一反馈电路的增益由a1表示,第三电容与第四电容的共同增益由-a2表示,负载阻抗由zl表示,此结构放大电路输入阻抗z

in

可以参见下式所示:

[0054][0055]

其中a1=c1,a2=c3/(c3+cgs),上式中第二项与负载阻抗zl和增益a1、a2相关,在电路设计过程中,可以通过增大g

m1

和第一反馈电路增益a1提高公式第二项在输入阻抗中所占比重,从而对输入阻抗产生更大的影响。负载阻抗zl由谐振电路组成,具有优质的选频特性和良好的带外抑制能力,增大zl对输入阻抗的影响能够有效提高输入阻抗带外抑制能力,抑制带外干扰。

[0056]

图9为本技术实施例中的以三组并联谐振电路为例的放大电路的仿真效果图,参见图9所示,以三组并联的谐振电路为例,其中每个谐振电路内有四组并联的选通电容阵列。三个谐振电路可实现工作频率范围连续覆盖1ghz至5ghz,每个谐振电路16种状态可调(仿真图省略中间状态),在放大电路具有良好的带外抑制能力即抗干扰能力情况下,同时实现宽频带覆盖。

[0057]

以上实施例仅用以说明本技术的技术方案,而非对其限制。尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行替换。而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1