半导体结构和相关芯片和电子装置的制作方法

1.本实用新型是有关于一种半导体结构,特别是一种可依据需求作为多位触发器或同步器的半导体结构。

背景技术:

2.随着芯片系统中的电路日益复杂,在电路设计的阶段,除了电路本身能够执行所需的功能之外,也需要考虑到在实际操作时,是否能够满足电路功耗及信号时序等条件。举例来说,为了减少整体芯片的动态功耗,就可能会加入共享时钟树的多位触发器(multi-bit flip-flop)来降低动态功耗。或者,若芯片系统中包含了在不同时钟频率下工作的电路,就可能会使用同步器(synchronizer)来减少数据出现亚稳态的情况,从而确保跨时钟域的电路之间能够同步地传输数据。

3.然而,设计者在电路设计的阶段可能无法完全预知实际操作的情况,因此常会在模拟或验证后,才调整设计并对应地设置同步器或多位触发器,又或是在事先就设置额外的同步器或多位触发器作为备用。由于同步器与多位触发器的功能不同,也无法共享,因此在设计上较无弹性,导致设计时间拉长,也可能增加所需的电路面积。

技术实现要素:

4.本实用新型的目的之一在于公开一种能够依据需求作为多位触发器或同步器的的半导体结构和相关芯片和电子装置,来解决上述问题。

5.本实用新型的一实施例提供一种半导体结构。半导体结构包含半导体基板(substrate)及宏单元(macro cell)。宏单元设置于该半导体基板上,并可包含时钟输入端、第一d型正反器(d flip flop)、第二d型正反器及第一线路连接单元。该时钟输入端用以接收时钟信号。该第一d型正反器具有时钟信号端、数据输入端及数据输出端,该第一d型正反器的该时钟信号端耦接于该时钟输入端。该第二d型正反器具有时钟信号端、数据输入端及数据输出端,该第二d型正反器的该时钟信号端耦接于该时钟输入端。该第一线路连接单元具有第一端耦接于该第一d型正反器的该数据输出端,第二端耦接于该第二d型正反器的该数据输入端,第三端耦接于第一外部数据输出端,及第四端耦接于第一外部数据输入端。

6.本实用新型的另一实施例提供一种芯片,该芯片包含前述的半导体结构。

7.本实用新型的另一实施例提供一种电子装置,该电子装置包含前述的芯片。

8.本实用新型的半导体结构和相关芯片和电子装置可以共享d型正反器来实作同步器或多位触发器以提升设计、制造流程及/或硬件使用的弹性与效率。

附图说明

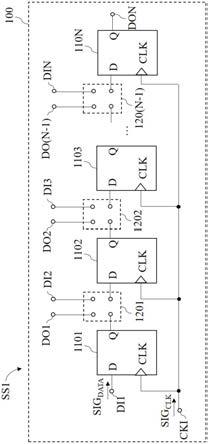

9.图1是本实用新型一实施例的半导体结构的示意图。

10.图2是使用图1的宏单元作为多位触发器的半导体结构的示意图。

11.图3是使用图1的宏单元作为同步器的半导体结构的示意图。

12.图4是本实用新型一实施例的半导体结构的示意图。

具体实施方式

13.以下公开内容提供用于实施本实用新型的不同特征的许多不同实施例或实例。下文描述组件及配置的特定实例以简化本实用新型。当然,此等仅为实例且不旨在限制。举例而言,在下列描述中,第一构件形成于第二构件上方或第一构件形成于第二构件之上,可包含该第一构件及该第二构件直接接触的实施例,且也可包含额外构件形成在该第一构件与该第二构件之间的实施例,使得该第一构件及该第二构件可不直接接触的实施例。另外,本实用新型可在各种实例中重复组件符号及/或字母。此重复出于简化及清楚的目的,且本身不代表所论述的各项实施例及/或组态之间的关系。

14.此外,为便于描述,可在本实用新型中使用诸如“在

…

下面”、“在

…

下方”、“下”、“在

…

上方”、“上”及类似者的空间相对术语来描述一个组件或构件与另一(些)组件或构件的关系,如图中绘示。空间相对术语旨在涵盖除在图中描绘的定向以外的使用或操作中的装置的不同定向。该装置可以有其他定向(旋转90度或按其他定向),同样可以相应地用来解释本实用新型中使用的空间相对描述词。

15.尽管阐述本实用新型的数值范围及参数为近似值,但申请人已尽可能精确地在具体实例中阐述数值。然而,任何数值必然含有源自各自测试环境下的误差。如本实用新型中使用,术语“约”通常意谓在一给定值或范围的10%、5%、1%或0.5%内。术语“约”也可以意谓一般技术者所认知的平均值内的可接受标准误差。除了在操作/工作实例中之外,或除非另外明确指定,否则在全部例项中所记载的数值范围、量、值及百分比(诸如针对材料数量、持续时间、温度、操作条件、量的比率及本实用新型中公开的其类似者的数值范围、量、值及百分比),应理解为均由术语“约”所修饰。因此,除非相反地指示,否则本实用新型及随附权利要求书中阐述的数值参数可依据实际状况变动的近似值,且各数值参数可能经一般舍入方式处理。本实用新型中可将范围表达为自一个数值端点至另一数值端点或在两个数值端点之间。除非另外指定,否则本实用新型中公开的全部范围都包含数值端点。

16.图1是本实用新型一实施例的半导体结构ss1的示意图,半导体结构ss1可包含半导体基板(未绘于图中)及宏单元100。宏单元100可设置于半导体基板上,且在本实施例中,宏单元100可依据需求而用以作为同步器或多位触发器。

17.如图1所示,宏单元100包含时钟输入端cki、外部数据输入端di1、外部数据输出端don、d型正反器1101至110n及线路连接单元1201至120(n-1),其中n为大于1的整数。时钟输入端cki可接收时钟信号sig

clk

。每一个d型正反器1101至110n可具有时钟信号端clk、数据输入端d及数据输出端q,且d型正反器1101至110n的时钟信号端clk可共同耦接至时钟输入端cki。此外,每一个线路连接单元1201至120(n-1)可具有第一端、第二端、第三端及第四端,且每一个线路连接单元1201至120(n-1)可耦接在d型正反器1101至110n对应的两个d型正反器之间。举例来说,线路连接单元1201的第一端可耦接于d型正反器1101的数据输出端q,线路连接单元1201的第二端可耦接于d型正反器1102的数据输入端d,线路连接单元1201的第三端可耦接于外部数据输出端do1,而线路连接单元1201的第四端可耦接于外部数据输入端di2。同样地,线路连接单元1202的第一端可耦接于d型正反器1102的数据输出端q,

线路连接单元1202的第二端可耦接于d型正反器1103的数据输入端d,线路连接单元1202的第三端可耦接于外部数据输出端do2,而线路连接单元1202的第四端可耦接于外部数据输入端di3。线路连接单元120(n-1)的第一端可耦接于d型正反器110(n-1)的数据输出端q(未绘于图中),线路连接单元120(n-1)的第二端可耦接于d型正反器110n的数据输入端d,线路连接单元120(n-1)的第三端可耦接于外部数据输出端do(n-1),而线路连接单元120(n-1)的第四端可耦接于外部数据输入端din。

18.在本实施例中,在尚未决定是否选择将宏单元100作为同步器或多位触发器之前,每一个线路连接单元1201至120(n-1)之中,其第一端、第二端、第三端及第四端中的任两者之间是处于无电性连接的浮接状态,而设计者可以在确定宏单元100作为同步器或多位触发器时,再设置导线以建立每一个线路连接单元1201至120(n-1)中对应端点之间的电性连接。

19.图2是使用宏单元100作为多位触发器的半导体结构ss2的示意图。如图2所示,相较于半导体结构ss1,半导体结构ss2还可包括导线la1至la(n-1)及lb1至lb(n-1)。在本实施例中,导线la1至la(n-1)及lb1至lb(n-1)可以是形成于宏单元100上的导电层。导线la1可耦接于线路连接单元1201的第一端及第三端,而导线lb1可耦接于线路连接单元1201的第二端及第四端。此外,导线la2可耦接于线路连接单元1202的第一端及第三端,而导线lb2可耦接于线路连接单元1202的第二端及第四端,并依此类推。如此一来,每一个d型正反器1101至110n都可独立地自外部接收数据,并将数据输出至外部,此时宏单元100即可作为共享时钟树的多位触发器,并可减少系统的动态功耗。

20.图3是使用宏单元100作为同步器的半导体结构ss3的示意图。如图3所示,相较于半导体结构ss1,半导体结构ss3还可包括导线lc1至lc(n-1)。导线lc1可耦接于线路连接单元1201的第一端及第二端,而导线lc2可耦接于线路连接单元1202的第一端及第二端,并依此类推。如此一来,宏单元100便可自外部数据输入端di1接收数据信号sig

data

,并通过串接的d型正反器1101至110n来传递并调整数据信号sig

data

,使得数据信号sig

data

能够趋于稳定并与时钟信号sig

clk

同步,再通过外部数据输出端don输出。此时,宏单元100即可作为同步器,并可减少数据信号处于亚稳态的机率,从而延长平均故障间隔的时间(mean time between failures,mtbf),并增加系统的稳定性。

21.此外,在本实施例中,宏单元100中每一个线路连接单元1201至120(n-1)的第一端、第二端、第三端及第四端的任两端之间可保持在无电性连接的状态,而设计者可以在半导体结构ss1的电子设计自动化(electronic design automation,eda)流程的自动设置及绕线(automatic placement&routing,apr)阶段设置宏单元100,并在进行模拟或测试之后,依据系统的需求,通过修改金属层的布局来增加导线la1至la(n-1)及lb1至lb(n-1),或增加导线lc1至lc(n-1)。即使在光罩完成后,也可以以工程变更命令(engineering chang order,eco)的方式,在金属层的光罩中增加导线la1至la(n-1)及lb1至lb(n-1)或导线lc1至lc(n-1)的设置,从而形成半导体结构ss2或ss3。如此一来,设计者在得知系统需求之后,就无须重新设置同步器或多位触发器并重新绕线,而可以弹性地选择使宏单元100作为同步器或多位触发器,因此能够给予设计者更多选择,并使设计及制造流程更有效率。此外,由于宏单元100可以依据需求而用以作为同步器或多位触发器,因此也可以增加其被使用的机率,减少因为不符需求而成为冗余组件的情况,从而提升整体系统的硬件使用率。在某

些实施例中,可以将宏单元100当备用单元任意布局在芯片的任何位置,视需求来修改为同步器或多位触发器。

22.图4是本实用新型另一实施例的半导体结构ss4的示意图。半导体结构ss4与ss1具有相似的结构,然而在半导体结构ss4中,宏单元200可包含线路连接单元2201至220(n-1)。在本实施例中,线路连接单元2201至220(n-1)可以是多任务器电路(multiplexer),并可依据控制信号sig

ctrl

来建立线路连接单元2201至220(n-1)中各端点之间的电性连接,以使宏单元200能够用以作为多位触发器或同步器。

23.举例来说,若选择宏单元200作为多位触发器、从而设定控制信号sig

ctrl

,每一个线路连接单元2201至220(n-1)便根据控制信号sig

ctrl

设定好的状态,在其第一端及第三端之间建立电性连接,并且在其第二端及第四端之间建立电性连接。例如,线路连接单元2201中的开关s1及s2都可导通,而开关s3则被截止。如此一来,每一个d型正反器1101至110n都可以自外部接收数据,并将数据输出至外部,此时宏单元200即可作为多位触发器,并可减少系统的动态功耗。

24.相对地,当选择宏单元200作为同步器时,控制信号sig

ctrl

会设定成另一状态,每一个线路连接单元2201至220(n-1)根据控制信号sig

ctrl

在其第一端及第二端之间建立电性连接。例如,线路连接单元2201中的开关s1及s2都可被截止,而开关s3则可被导通。如此一来,宏单元100便可自外部数据输入端di1接收数据信号sig

data

,并通过串接的d型正反器1101至110n来传递并调整数据信号sig

data

,使得数据信号sig

data

能够趋于稳定并与时钟信号sig

clk

同步,再通过外部数据输出端don输出。此时,宏单元100即可作为同步器,并可减少数据信号处于亚稳态的机率。

25.由于线路连接单元2201至220(n-1)可以依据控制信号sig

ctrl

来建立内部端点之间的电性连接,因此在系统通电运作时,仍可依据需求而将宏单元100作为同步器或多位触发器。如此一来,半导体结构ss3在设计及操作上都能提供更多的选择,从而提升半导体结构ss3的硬件使用效率。

26.虽然在图4中线路连接单元2201至220(n-1)可以利用多个开关电路来实作,然而本实用新型并不以此为限,在有些其他实施例中,线路连接单元2201至220(n-1)也可能利用其他的组件或其他的结构来实作多任务器电路以控制其内部四个端点间的电性连接。

27.此外,本实用新型还提出一种芯片,包含半导体结构ss1、ss2、ss3或ss4设置于其中。本实用新型还提出一种包含该芯片的电子装置。具体来说,该电子装置可包含但不限于行动通信设备、超级行动计算机、便携式娱乐设备和其他的电子设备。行动通信设备的特点是具备行动通信功能,并且以提供语音、数据通信为主要目标。这类设备包括:智能型手机(例如iphone)、多媒体手机、功能性手机,以及低端手机等。超级行动计算机属于个人计算机的范畴,有计算和处理功能,一般也具备行动上网特性。这类设备包括:pda、mid和umpc设备等,例如ipad。便携式娱乐设备可以显示和播放多媒体内容。该类设备包括:音讯、视频播放器(例如ipod),掌上游戏机,电子书,以及智能玩具和便携式车载导航设备。

28.由于本实用新型的实施例所提供的宏单元可以包含多个d型正反器,并可依据需求而用以作为同步器或多位触发器,因此在设计及使用上可提供较多的选择,从而提升设计、制造流程及/或硬件使用的弹性与效率。

29.上文的叙述简要地提出了本实用新型某些实施例的特征,而使得本实用新型所属

本领域的技术人员能够更全面地理解本实用新型内容的多种态样。本实用新型所属本领域技术人员当可明了,其可轻易地利用本实用新型内容作为基础,来设计或更动其他制程与结构,以实现与此处的实施方式相同的目的和/或达到相同的优点。本实用新型所属本领域的技术人员应当明白,这些均等的实施方式仍属于本实用新型内容的精神与范围,且其可进行各种变更、替代与更动,而不会悖离本实用新型内容的精神与范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1