测试封装线路板的制作方法

1.本技术涉及芯片封装技术领域,更具体地,涉及一种测试封装线路板。

背景技术:

2.现有的麦克风中的asic芯片封装测试过程中,通常一款asic芯片对应一款pcb(线路板),并且使用时需要焊接探针进行测试。因此,现有的asic芯片在封装测试过程中,只支持单体封装,无法进行批量上产,成本较高。

技术实现要素:

3.本技术的一个目的是提供一种测试封装线路板的新技术方案,至少能够解决现有技术中一款asic芯片对应一款线路板的问题。

4.本技术提供了一种测试封装线路板,用于mems麦克风中的asic芯片的封装测试,所述线路板具有相对设置的第一表面和第二表面,所述第一表面设有多个第一焊盘和第二焊盘,其中,多个所述第一焊盘能够对应至少两种不同类型的asic芯片的端口,多个所述第二焊盘用于焊接电容;所述第二表面设有多个第三焊盘,多个所述第三焊盘用于连接外部测试工装。

5.可选地,所述线路板的截面为方形,所述第一焊盘包括:第一vdd焊盘、第一data焊盘、第一clk焊盘、第一l/r焊盘和第一gnd焊盘,所述第一vdd焊盘、所述第一data焊盘、所述第一clk焊盘、所述第一l/r焊盘和所述第一gnd焊盘在靠近所述线路板的所述第一表面的第一条长边上沿长度方向间隔开布置。

6.可选地,所述第一焊盘还包括:第一sub焊盘、第一mic焊盘、第一inn焊盘和第一inp焊盘,所述第一sub焊盘、所述第一mic焊盘、所述第一inn焊盘和所述第一inp焊盘在靠近所述线路板的所述第一表面的第二条长边上沿长度方向间隔开分布。

7.可选地,所述第一焊盘还包括:第一vmic焊盘、第二inp焊盘、第二inn焊盘和第二mic焊盘,所述第一vmic焊盘、所述第二inp焊盘、所述第二inn焊盘和所述第二mic焊盘靠近所述线路板的所述第一表面的第一条短边上沿宽度方向间隔开布置。

8.可选地,所述第一焊盘还包括:第三mic焊盘,所述第三mic焊盘与所述第二mic焊盘同排布置。

9.可选地,所述第二焊盘的个数为两个,两个所述第二焊盘设在靠近所述线路板的所述第一表面的第二条长边上,且沿所述线路板的长度方向间隔开布置,以用于焊接一个所述电容。

10.可选地,所述第二焊盘的个数为四个,四个所述第二焊盘设在靠近所述线路板的第二条长边上,且沿所述线路板的长度方向间隔开布置,以用于焊接两个所述电容。

11.可选地,所述第三焊盘包括:第二vdd焊盘、第二data焊盘、第二clk焊盘、第二l/r焊盘和第二gnd焊盘,所述第二vdd焊盘、所述第二data焊盘、所述第二clk焊盘、所述第二l/r焊盘和所述第二gnd焊盘在靠近所述线路板的所述第二表面的第一条长边上沿长度方向

间隔开布置。

12.可选地,所述第三焊盘还包括:第二sub焊盘、第四mic焊盘、第三inn焊盘、第三inp焊盘和第二vmic焊盘,所述第二sub焊盘、所述第四mic焊盘、所述第三inn焊盘、所述第三inp焊盘和所述第二vmic焊盘在靠近所述线路板的所述第二表面的第二条长边上沿长度方向间隔开分布。

13.可选地,所述第一表面和所述第二表面之间设有第一线路连接层和第二线路连接层,所述第一线路连接层靠近所述第一表面,所述第二线路连接层靠近所述第二表面。

14.根据本实用新型实施例的测试封装线路板,在线路板的第一表面上设置有多个第一焊盘和第二焊盘,并且多个第一焊盘能够对应至少两种不同类型的asic芯片的端口,在同一个线路把上集成多种asic设计,保证同一个线路板上适用不同种类的asic芯片封装,可进行量产封装,降低封装成本,使用更加便捷,能够满足不同的测试需求。

15.通过以下参照附图对本技术的示例性实施例的详细描述,本技术的其它特征及其优点将会变得清楚。

附图说明

16.被结合在说明书中并构成说明书的一部分的附图示出了本技术的实施例,并且连同其说明一起用于解释本技术的原理。

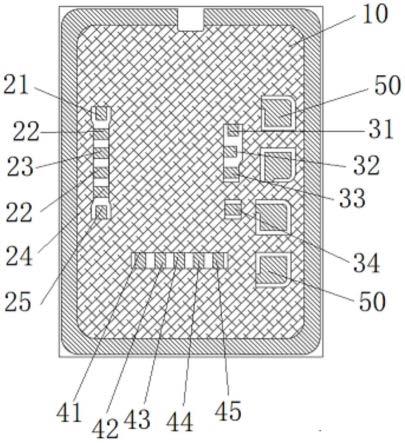

17.图1是本实用新型实施例的测试封装线路板的第一表面的结构示意图;

18.图2是本实用新型实施例的测试封装线路板的第二表面的结构示意图;

19.图3是本实用新型实施例的测试封装线路板的第一线路连接层的结构示意图;

20.图4是本实用新型实施例的测试封装线路板的第二线路连接层的示意图。

21.附图标记:

22.线路板10;

23.第一vdd焊盘21;第一data焊盘22;第一clk焊盘23;第一l/r焊盘24;第一gnd焊盘25;

24.第一sub焊盘31;第一mic焊盘32;第一inn焊盘33;第一inp焊盘34;

25.第一vmic焊盘41;第二inp焊盘42;第二inn焊盘43;第二mic焊盘44;第三mic焊盘45;

26.第二焊盘50;

27.第二vdd焊盘61;第二data焊盘62;第二clk焊盘63;第二l/r焊盘64;第二gnd焊盘65;

28.第二sub焊盘71;第四mic焊盘72;第三inn焊盘73;第三inp焊盘74;第二vmic焊盘75;

29.第一线路连接层81;第二线路连接层82。

具体实施方式

30.现在将参照附图来详细描述本技术的各种示例性实施例。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本技术的范围。

31.以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本技术及其应用或使用的任何限制。

32.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为说明书的一部分。

33.在这里示出和讨论的所有例子中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它例子可以具有不同的值。

34.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步讨论。

35.下面结合附图具体描述根据本实用新型实施例的测试封装线路板10。

36.如图1和图2所示,根据本实用新型实施例的测试封装线路板10,线路板10具有相对设置的第一表面和第二表面,第一表面设有多个第一焊盘和第二焊盘50。

37.具体来说,多个第一焊盘能够对应至少两种不同类型的asic芯片的端口,多个第二焊盘50用于焊接电容。第二表面设有多个第三焊盘,多个第三焊盘用于连接外部测试工装。

38.换言之,根据本实用新型实施例的测试封装线路板10主要用于mems麦克风中的asic芯片(asic,application specific integrated circuit,专用集成电路)的封装测试。线路板10称为印制线路板{printed circuit boards},或者称为印刷电路板。该测试封装线路板10能够适用各类mic asic设计的侧装测试。例如,数字asic以及模拟asic等不同种类的asic芯片。

39.参见图1和图2,该测试封装线路板10具有相对设置的第一表面和第二表面,第一表面设有多个第一焊盘和第二焊盘50。多个第一焊盘和第二焊盘50可以具有不同的功能,以便于满足不同种类的asic芯片的测试需要。其中,多个第一焊盘能够对应至少两种不同类型的asic芯片的端口,asic芯片在测试封装的过程中,可以将asic芯片贴装在线路板10上,并且将asic芯片上待测试的不同端口引脚打在对应的第一焊盘上和/或第二焊盘50上。通过设计多个不同种类的焊盘(第一焊盘和第二焊盘50),能够满足不同种类(数字、模拟asic通用)asic芯片的设计,便于进行量产封装,降低封装成本,使用更加便捷,能够满足不同的测试需求。

40.多个第二焊盘50能够用于焊接电容。多个第二焊盘50可以替代mems作用,多个第二焊盘50能够等效于mems。本领域技术人员能够理解mems麦克风中,mems芯片相当于一个电容器,在本技术中不再详细赘述。

41.需要说明的是,现有技术中在测试封装的过程中,封装线路板10的体积较大,通常为3*3cm。将封装线路板10设置在一个大的测试工装中进行封装测试。因此,现有的封装线路板10仅支持单体封装,无法进行批量生产,导致成本较高。而本技术通过对应设计小尺寸的测试工装,可以将测试封装线路板10设计成4*3mm,线路板10的大小与asic芯片大小一致(4*3mm),极大地减少了线路板10的体积。

42.本技术的测试封装线路板10的第二表面设置有多个第三焊盘,多个第三焊盘主要用于连接外部测试工装,实现asic芯片的封装测试。

43.由此,根据本实用新型实施例的测试封装线路板10,在线路板10的第一表面上设置有多个第一焊盘和第二焊盘50,并且多个第一焊盘能够对应至少两种不同类型的asic芯

片的端口,在同一个线路把上集成多种asic设计,保证同一个线路板10上适用不同种类的asic芯片封装,可进行量产封装,降低封装成本,使用更加便捷,能够满足不同的测试需求。

44.根据本实用新型的一个实施例,线路板10的截面为方形,第一焊盘包括:第一vdd焊盘21、第一data焊盘22、第一clk焊盘23、第一l/r焊盘24和第一gnd焊盘25,第一vdd焊盘21、第一data焊盘22、第一clk焊盘23、第一l/r焊盘24和第一gnd焊盘25在靠近线路板10的第一表面的第一条长边上沿长度方向间隔开布置。

45.也就是说,如图1所示,线路板10的截面可以设计成方形,第一焊盘具有第一vdd焊盘21、第一data焊盘22、第一clk焊盘23、第一l/r焊盘24和第一gnd焊盘25。其中,第一vdd焊盘21、第一data焊盘22、第一clk焊盘23、第一l/r焊盘24和第一gnd焊盘25竖直排布在线路板10的第一表面的靠近第一条长边的一侧。其中,第一data焊盘22的个数为两个,两个第一data焊盘22中间设置第一clk焊盘23。在本技术中,数字asic上对应的引脚可以打在第一vdd焊盘21、第一data焊盘22、第一clk焊盘23、第一l/r焊盘24和第一gnd焊盘25与线路进行电连接,实现数字asic的封装测试。当然,在本技术中,对于vdd表示器件工作电压、clk表示时针信号、data表示数据引脚、l/r表示通道选择以及gnd表示接地等的具体含义和原理,本领域技术人员是可以理解的,在本技术中不再详细赘述。

46.根据本实用新型的一个实施例,第一焊盘还包括第一sub焊盘31、第一mic焊盘32、第一inn焊盘33、第一inp焊盘34和第一vmic焊盘41,第一sub焊盘31、第一mic焊盘32、第一inn焊盘33、第一inp焊盘34和第一vmic焊盘41在靠近线路板10的第一表面的第二条长边上沿长度方向间隔开分布。

47.换句话说,参见图1,第一焊盘还可以包括第一sub焊盘31、第一mic焊盘32、第一inn焊盘33和第一inp焊盘34,其中,第一sub焊盘31、第一mic焊盘32、第一inn焊盘33和第一inp焊盘34竖直排布在线路板10的第一表面的靠近第二条长边上。第一sub焊盘31、第一mic焊盘32、第一inn焊盘33和第一inp焊盘34中的部分焊盘能够用于模拟asic,例如,第一mic焊盘32等。sub焊盘能够方便搭配mems(micro-electro-mechanical system,微机电系统),inn和inp表示输入终端,其中inp焊盘用于单端输入的asic芯片,inn焊盘用于差分输入的asic芯片,便于在同一个线路板10上适用不同种类的asic芯片封装,可进行量产封装,降低封装成本,使用更加便捷,能够满足不同的测试需求。在本技术中,sub、mic、inn、inp、vmic等都是本领域技术人员所熟知的技术名称,在本技术中,不再详细赘述。

48.根据本实用新型的一个实施例,参见图1,第一焊盘还可以包括第一vmic焊盘41、第二inp焊盘42、第二inn焊盘43和第二mic焊盘44,其中,第一vmic焊盘41、第二inp焊盘42、第二inn焊盘43和第二mic焊盘44在靠近线路板10的第一表面的第一条短边上沿宽度方向间隔开布置。第一焊盘还可以包括:第三mic焊盘45,第三mic焊盘45与第二mic焊盘44同排布置。其中,mic和vmic焊盘均可以用于电压偏置的量测,线路板10的第一表面上多个位置、多个焊盘(pad)的设计可以用于不同种类的asic芯片的封装测试,有效降低成本,利于封装进行各种ac/dc信号的相关测试。

49.根据本实用新型的一个实施例,第二焊盘50的个数为两个,两个第二焊盘50设在靠近线路板10的第一表面的第二条长边上,且沿线路板10的长度方向间隔开布置,以用于焊接一个电容。

50.也就是说,第二焊盘50的个数可以设计两个,主要应用在单端输入的asic类型。两

个第二焊盘50设置在线路板10的第一表面上靠近第二条长边的位置处,并且两个第二焊盘50沿线路板10的长度方向间隔开布置,两个第二焊盘50可以用于焊接一个电容,主要用于替换mems,以便于asic芯片模拟在mems的结果下的测试结论。

51.在本实用新型的一些具体实施方式中,如图1所示,第二焊盘50的个数为四个,主要应用在差分输入的asic类型。四个第二焊盘50在靠近线路板10的第二条长边上,且沿线路板10的长度方向间隔开布置,以用于焊接两个电容,便于asic芯片模拟在mems的结果下的测试结论。在本技术中,每个第二焊盘50的截面面积大于每个第一焊盘的截面面积,便于焊接电容。

52.根据本实用新型的一个实施例,如图2所示,第三焊盘包括第二vdd焊盘61、第二data焊盘62、第二clk焊盘63、第二l/r焊盘64和第二gnd焊盘65,第二vdd焊盘61、第二data焊盘62、第二clk焊盘63、第二l/r焊盘64和第二gnd焊盘65设置在靠近线路板10的第二表面的第一条长边上,并且第二vdd焊盘61、第二data焊盘62、第二clk焊盘63、第二l/r焊盘64和第二gnd焊盘65沿长度方向间隔开布置。

53.第三焊盘还包括:第二sub焊盘71、第四mic焊盘72、第三inn焊盘73、第三inp焊盘74和第二vmic焊盘75,第二sub焊盘71、第四mic焊盘72、第三inn焊盘73、第三inp焊盘74和第二mic焊盘44在靠近线路板10的第二表面的第二条长边上沿长度方向间隔开分布。线路板10的第二表面设计10个焊盘(pad)的功能与第一表面上的焊盘是相互对应的,线路板10的第二表面的焊盘用于与连接外部测试工装,实现asic芯片的封装测试。

54.根据本实用新型的一个实施例,如图3和图4所示,第一表面和第二表面之间设置有第一线路连接层81和第二线路连接层82,第一线路连接层81靠近第一表面,第一线路连接层81的线路设计与第一表面上的多个焊盘的布局位置相对应。第二线路连接层82靠近第二表面,第二线路连接层82的线路设计与第二表面上的第三焊盘的布局位置相对应。线路板10的第一表面上的焊盘和第二表面上的焊盘通过第一线路连接层81和第二线路连接层82电连接。

55.总而言之,根据本实用新型实施例的测试封装线路板10,体积较小,通过在线路板10的第一表面上设置有多个第一焊盘和第二焊盘50,并且多个第一焊盘能够对应至少两种不同类型的asic芯片的端口,在同一个线路把上集成多种asic设计,保证同一个线路板10上适用不同种类的asic芯片封装,可进行量产封装,降低封装成本,使用更加便捷,能够满足不同的测试需求。

56.当然,对于本领域技术人员来说,测试封装线路板10的其他结构及其工作原理是可以理解并且能够理解的,在本技术中不再详细赘述。

57.虽然已经通过例子对本技术的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上例子仅是为了进行说明,而不是为了限制本技术的范围。本领域的技术人员应该理解,可在不脱离本技术的范围和精神的情况下,对以上实施例进行修改。本技术的范围由所附权利要求来限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1