FPCB以及用于制造该FPCB的方法与流程

fpcb以及用于制造该fpcb的方法

技术领域

1.相关申请的交叉引用

2.本技术要求于2020年7月28日提交的韩国专利申请第10-2020-0094041号的优先权权益,其全部内容通过引用并入本文。

3.本发明涉及一种fpcb以及一种用于制造该fpcb的方法,更具体地,涉及一种如下fpcb以及一种用于制造该fpcb的方法,在该fpcb上不需要安装熔断器,从而减小总体积并且节省成本。

背景技术:

4.印刷电路板(pcb)广泛用于各种电子产品,诸如tv、电脑、移动电话、显示器、通信网络和半导体模块。作为一种类型的这种pcb,特别是具有柔性的柔性印刷电路板(fpcb)最近已经被广泛使用。

5.通常,fpcb通过如下方式来制造:将铜箔层压在聚酰亚胺膜上以形成覆铜层压板,将干膜层压在该覆铜层压板上以通过曝光、显影和蚀刻工序而形成导体图案,然后将覆盖层附接在最外面的铜箔上。通过利用原材料的柔性,fpcb以弯曲状态被安装在复杂的产品外壳的内部,或者被用在反复移动的部分处,并且由于fpcb的性质,fpcb在小型化(数码相机、摄像机等)、柔性(打印机头、硬盘等)、高密度线材(精密仪器,诸如医疗器械)以及组装合理化(测量仪器、车载电子器件、电池模块等)中以各种方式使用。

6.fpcb通过蚀刻等而形成,因此不会占用很大的体积,也不会经常由于外部冲击而导致诸如断开连接的问题。然而,在完全制造出fpcb之后,诸如熔断器的元件通过安装工序被分开地安装在fpcb上。因此,存在fpcb的总体积增加并且成本也增加的问题。

7.[现有技术文献]

[0008]

(专利文献1)韩国专利公开第1845714号

技术实现要素:

[0009]

技术问题

[0010]

为了解决上述问题,本发明的目的在于提供一种fpcb以及一种用于制造该fpcb的方法,在该fpcb上不需要安装熔断器,从而减小总体积并且节省成本。

[0011]

本发明所要解决的问题不限于上述问题,并且根据以下描述,未提及的其他问题对于本领域技术人员来说可以是显而易见的。

[0012]

技术解决方案

[0013]

在用于实现上述目的的根据本发明的实施例的包括图案电路层的fpcb中,在该图案电路层中嵌入有图案熔断器,并且该图案熔断器包括:第一导线,该第一导线由金属制成并且具有螺旋结构;以及第二导线,该第二导线由金属制成并且具有螺旋结构,其中,该第一导线和该第二导线具有双螺旋结构。

[0014]

此外,第一导线可以包括:第一下导线,该第一下导线被形成在图案电路层的底表

面上;第一上导线,该第一上导线被形成在图案电路层的顶表面上;以及第一导通导线,该第一导通导线被构造成将第一下导线和第一上导线彼此连接,并且第二导线可以包括:第二下导线,该第二下导线被形成在图案电路层的底表面上;第二上导线,该第二上导线被形成在图案电路层的顶表面上;以及第二导通导线,该第二导通导线被构造成将第二下导线和第二上导线彼此连接。

[0015]

此外,第一导线和第二导线可以具有四边形形状和双螺旋结构。

[0016]

此外,第一下导线、第二下导线、第一上导线和第二上导线中的每一个可以被形成为具有直线形状。

[0017]

此外,第一导通导线和第二导通导线中的每一个可以被形成为在图案电路层上在厚度方向上具有直线形状。

[0018]

此外,第一导线和第二导线中的每一个可以具有起始端子和结束端子,该起始端子和该结束端子仅被暴露在图案电路层的顶表面或底表面中的一个上。

[0019]

此外,第一导线的起始端子和第二导线的起始端子可以分开地形成,并且第一导线的结束端子和第二导线的结束端子也可以分开地形成。

[0020]

此外,第一导线的起始端子和第二导线的起始端子可以被形成为彼此连接,并且第一导线的结束端子和第二导线的结束端子可以被形成为彼此连接。

[0021]

此外,第一导线和第二导线中的每一个可以具有被连接到电力汇流条的起始端子以及被连接到感测汇流条的结束端子。

[0022]

此外,第一导线的结束端子可以被连接到第一感测汇流条,并且第二导线的结束端子可以被连接到第二感测汇流条。

[0023]

此外,所述金属可以包括银、铜、金或铝中的至少一种。

[0024]

此外,在图案电路层的顶表面上还可以层压有覆盖层。

[0025]

用于实现上述目的的根据本发明的实施例的用于制造fpcb的方法包括:在基膜的顶表面上形成第一下导线和第二下导线;暴露第一下导线和第二下导线的两端,并且将微柱层压在基膜的顶表面上;在第一下导线和第二下导线的两端上分别形成第一导通导线和第二导通导线;将填料注入基膜的顶表面上的未填充有微柱的空闲空间中;以及在微柱的顶面上形成将第一导通导线彼此连接的第一上导线以及将第二导通导线彼此连接的第二上导线。

[0026]

此外,在第一下导线和第二下导线的形成中,第一下导线和第二下导线可以被形成为平行于第一方向。

[0027]

此外,在第一上导线和第二上导线的形成中,第一上导线和第二上导线可以被形成为平行于第二方向。

[0028]

此外,第一方向和第二方向可以是彼此不同的方向。

[0029]

此外,在第一下导线和第二下导线的形成中,第一下导线和第二下导线可以通过蚀刻或印刷方法中的至少一种方法被形成在基膜的顶表面上。

[0030]

此外,在第一上导线和第二上导线的形成中,第一上导线和第二上导线可以通过蚀刻或印刷方法中的至少一种方法被形成在微柱的顶表面上。

[0031]

此外,在形成第一上导线和第二上导线之后,包括第一下导线、第一导通导线和第一上导线的第一导线以及包括第二下导线、第二导通导线和第二上导线的第二导线可以均

具有被形成在起始部分处的起始端子和被形成在结束部分处的结束端子。

[0032]

此外,第一导线和第二导线可以具有仅被暴露在图案电路层的顶表面或底表面中的一个上的起始端子和结束端子。

[0033]

本发明的其他具体细节被包括在详细描述和附图中。

[0034]

有利效果

[0035]

根据本发明的实施例,至少具有以下效果。

[0036]

由于具有双螺旋结构的图案熔断器使用贯穿聚合物导通(through polymer via,tpv)方法而不是安装方法等被形成在fpcb上,所以能够减小fpcb的总体积并且节省成本。

[0037]

根据本发明的效果不受上文例示的内容的限制,并且在本文中包括更多的各种效果。

附图说明

[0038]

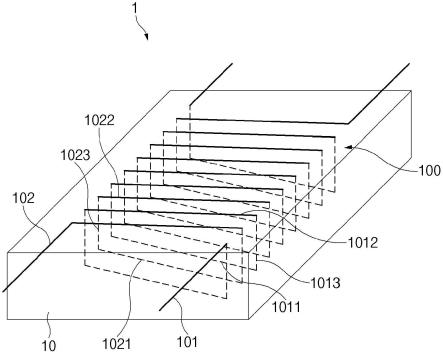

图1是根据本发明的实施例的其中嵌入有图案熔断器100的fpcb1的立体图。

[0039]

图2是示出了根据本发明的实施例的用于制造其中嵌入有图案熔断器100的fpcb 1的方法的流程图。

[0040]

图3是示出了根据本发明的实施例的其中第一下导线1011和第二下导线1021被形成在基膜11上的状态的示意性侧视图。

[0041]

图4是示出了根据本发明的实施例的其中第一下导线1011和第二下导线1021被形成在基膜11上的状态的示意性俯视图。

[0042]

图5是示出了根据本发明的实施例的其中微柱103被形成在基膜11上的状态的示意性侧视图。

[0043]

图6是示出了根据本发明的实施例的其中微柱103被形成在基膜11上的状态的示意性俯视图。

[0044]

图7是示出了根据本发明的实施例的其中第一导通导线1012和第二导通导线1022被形成在基膜11上的状态的示意性侧视图。

[0045]

图8是示出了根据本发明的实施例的其中填料104被注入基膜11中的状态的示意性侧视图。

[0046]

图9是示出了根据本发明的实施例的其中填料104被注入基膜11中的状态的示意性俯视图。

[0047]

图10是示出了根据本发明的实施例的其中第一上导线1013和第二上导线1023被形成的状态的示意性俯视图。

[0048]

图11是示出了根据本发明的实施例的其中起始端子1014和1024以及结束端子1015和1025被形成在第一导线101和第二导线102上的状态的立体图。

[0049]

图12是示出了根据本发明的实施例的其中汇流条21和22被连接到图案熔断器100的状态的示意图。

[0050]

图13是示出了根据本发明的另一个实施例的其中起始端子105和结束端子106被形成在第一导线101和第二导线102上的状态的立体图。

[0051]

图14是示出了根据本发明的另一个实施例的其中汇流条21a和22a被连接到图案熔断器100a的状态的示意图。

具体实施方式

[0052]

通过参考示例性实施例的以下详细描述以及附图,可以更容易地理解本发明构思的优点和特征以及实现它们的方法。然而,本发明构思可以以不同的形式实施,并且不应被解释为限于本文中所阐述的实施例。相反,提供这些实施例是使得本公开将透彻且完整,并且将本发明构思的范围充分地传达给本发明构思所属领域的技术人员。本发明构思将仅由所附权利要求限定。在整个说明书中,相同的附图标记指代相同的元件。

[0053]

除非另有定义,否则本文中使用的所有术语(包括技术术语和科学术语)将以本发明构思所属领域的普通技术人员能够普遍理解的意义来使用。此外,除非有明确定义,否则不会对常用词典中定义的术语进行理想地或过度地解释。

[0054]

本文中使用的术语是为了描述实施例的目的,并且不旨在限制本发明。在本公开中,除非上下文另有明确指示,否则单数形式包括复数形式。如本文中所使用的,术语“包括”和/或“包含”旨在包括所述元件,并且不排除存在或添加一个或多个其他元件的可能性。

[0055]

在下文中,将参考附图详细描述本发明的优选实施例。

[0056]

图1是根据本发明的实施例的其中嵌入有图案熔断器100的fpcb1的立体图。

[0057]

根据本发明的实施例,由于具有双螺旋结构的图案熔断器100使用贯穿聚合物导通(tpv)方法而不是安装方法等被形成在fpcb 1上,所以能够减少fpcb 1的总体积并且节省成本。

[0058]

为此,在根据本发明的实施例的包括图案电路层10的fpcb 1中,在该图案电路层10中嵌入有图案熔断器100,并且图案熔断器100包括:第一导线101,该第一导线101由金属制成并且螺旋地形成;以及第二导线102,该第二导线102由金属制成并且螺旋地形成。第一导线101和第二导线102具有双螺旋结构。

[0059]

如图1所示,根据本发明的实施例的图案熔断器100包括第一导线101和第二导线102。第一导线101由金属制成,并且被嵌入fpcb 1的图案电路层10中。此外,第二导线102也由金属制成,并且被嵌入fpcb 1的图案电路层10中。第一导线101和第二导线102都具有螺旋结构,特别是双螺旋结构。

[0060]

具体地,第一导线101包括第一下导线1011、第一上导线1013和第一导通导线1012。第一下导线1011被形成为在图案电路层10的底表面上具有直线形状,并且第一上导线1013被形成为在图案电路层10的顶表面上具有直线形状。此外,第一导通导线1012将第一下导线1011和第一上导线1013彼此连接,并且被形成为在图案电路层10上在厚度方向上具有直线形状。如上文描述的,由于第一下导线1011、第一上导线1013和第一导通导线1012均具有直线形状,所以第一导线101可以具有四边形形状。此外,由于第一下导线1011、第一导通导线1012和第一上导线1013被依次连接并且重复地形成,所以第一导线101可以具有螺旋结构。

[0061]

以相同的方式,第二导线102包括第二下导线1021、第二上导线1023和第二导通导线1022。第二下导线1021被形成为在图案电路层10的底表面上具有直线形状,并且第二上导线1023被形成为在图案电路层10的顶表面上具有直线形状。此外,第二导通导线1022将第二下导线1021和第二上导线1023彼此连接,并且被形成为在图案电路层10上在厚度方向上具有直线形状。如上文描述的,由于第二下导线1021、第二上导线1023和第二导通导线

1022均具有直线形状,所以第二导线102可以具有四边形形状。此外,由于第二下导线1021、第二导通导线1022和第二上导线1023被依次连接并且重复地形成,所以第二导线102可以具有螺旋结构。

[0062]

第一导线101和第二导线102不被分开地形成,而是以彼此重叠的状态螺旋地形成,即,具有双螺旋结构。此外,用于形成第一导线101和第二导线102的金属可以包括具有高导电性的银、铜、金或铝中的至少一种,特别地,可以优选地包括容易成型、价格低廉且经济的铜。

[0063]

图2是示出了根据本发明的实施例的用于制造其中嵌入有图案熔断器100的fpcb 1的方法的流程图。

[0064]

根据本发明的实施例的用于制造fpcb 1的方法包括:在基膜11的顶表面上形成第一下导线1011和第二下导线1021的过程;暴露第一下导线1011和第二下导线1021的两端并且将微柱103层压在基膜11的顶表面上的过程;在第一下导线1011和第二下导线1021的两端上分别形成第一导通导线1012和第二导通导线1022的过程;将填料104注入基膜11的顶表面上的未填充有微柱103的空闲空间中的过程;以及在微柱103的顶表面上形成将第一导通导线1012彼此连接的第一上导线1013和将第二导通导线1022彼此连接的第二上导线1023的过程。

[0065]

在下文中,将参考图3至图10详细描述在图2的流程图中示出的每一个步骤。

[0066]

图3是示出了根据本发明的实施例的其中第一下导线1011和第二下导线1021被形成在基膜11上的状态的示意性侧视图,并且图4是示出了根据本发明的实施例的其中第一下导线1011和第二下导线1021被形成在基膜11上的状态的示意性俯视图。

[0067]

首先,制备基膜11,并且如图3所示,在基膜11的顶表面上形成第一下导线1011和第二下导线1021(s201)。基膜11可以是包含硅的膜。此外,第一下导线1011和第二下导线1021可以通过蚀刻或印刷方法中的至少一种方法被形成在基膜11的顶表面上。

[0068]

第一下导线1011和第二下导线1021均被设置成多个,并且可以被形成为平行于第一方向。此外,如图4所示,第一方向例如可以具有相对于基膜11的预定倾斜度。此外,第一下导线1011和第二下导线1021可以彼此交替地形成。因此,随后,第一导线101和第二导线102可以具有双螺旋结构。

[0069]

图5是示出了根据本发明的实施例的其中微柱103被形成在基膜11上的状态的示意性侧视图,并且图6是示出了根据本发明的实施例的其中微柱103被形成在基膜11上的状态的示意性俯视图。

[0070]

当形成第一下导线1011和第二下导线1021时,如图5所示,第一下导线1011和第二下导线1021的两端被暴露,并且微柱103被层压在基膜11的顶表面上(s202)。此时,如图6所示,微柱103被设置成多个,并且可以被形成为平行于与第一方向不同的第二方向。此外,随后,第一上导线1013和第二上导线1023沿着微柱103形成。因此,不同的第一下导线1011的端部可以分别被设置在一个微柱103的两端上,或者不同的第二下导线1021的端部可以分别被设置在一个微柱103的两端上。

[0071]

为了层压微柱103,可以首先层压厚光刻胶,然后将该厚光刻胶图案化。微柱103可以是环氧树脂类su-8负性光刻胶,该负性光刻胶通过紫外线交联,并且其剩余部分被清洗以有助于图案化。

[0072]

同时,尽管在附图中未示出,但在层压微柱103之后,可以形成单独的种层,以激活微柱103。为了形成种层,可以使用物理气相沉积(pvd)方法,或者可以使用原子层沉积(ald)方法。此外,种层可以包括具有导电性、对金属的良好粘附性和低加工温度的氮化钛(tin)。

[0073]

图7是示出了根据本发明的实施例的其中第一导通导线1012和第二导通导线1022被形成在基膜11上的状态的示意性侧视图。

[0074]

在层压微柱103之后,可以将第一导通导线1012和第二导通导线1022分别形成在第一下导线1011和第二下导线1021的两端处(s203)。如上文描述的,不同的第一下导线1011的端部可以分别被设置在微柱103的两端上,或者不同的第二下导线1021的端部可以分别被设置在微柱103的两端上。因此,当形成第一导通导线1012和第二导通导线1022时,如图7所示,第一导通导线1012和第二导通导线1022可以沿着微柱103的两端的侧壁形成。

[0075]

为了形成第一导通导线1012和第二导通导线1022,微柱103可以用金属(诸如铜)进行非电解镀。此外,为了防止金属腐蚀,可以用具有低离子化倾向的金属附加地执行电解镀。

[0076]

第一导通导线1012和第二导通导线1022中的每一个也由金属制成,并且当随后形成第一上导线1013和第二上导线1023时,第一导通导线1012和第二导通导线1022分别将下导线1011和1021与上导线1013和1023连接,由此用作被构造成将图案电路层10的底表面和顶表面彼此电连接的贯穿电极。

[0077]

图8是示出了根据本发明的实施例的其中填料104被注入基膜11中的状态的示意性侧视图,并且图9是示出了根据本发明的实施例的其中填料104被注入基膜11中的状态的示意俯视图。

[0078]

如图8和图9所示,在基膜11的顶表面上,将填料104注入未填充有微柱103的空闲空间中(s204)。填料104可以是具有电绝缘性的环氧树脂模塑组合物(emc)。因此,微柱103可以被封装在绝缘体的内部。

[0079]

图10是示出了根据本发明的实施例的其中第一上导线1013和第二上导线1023被形成的状态的示意性俯视图。

[0080]

在微柱103的顶表面上,形成将第一导通导线1012彼此连接的第一上导线1013以及将第二导通导线1022彼此连接的第二上导线1023(s205)。此外,第一上导线1021和第二上导线1023可以通过蚀刻或印刷方法中的至少一种方法被形成在微柱103的顶表面上。

[0081]

第一上导线1013和第二上导线1023都沿着微柱103形成。即,第一上导线1013可以在将第一导通导线1012彼此连接的同时被形成在其上形成有第一导通导线1012的微柱103的顶表面上,并且第二上导线1023可以在将第二导通导线1022彼此连接的同时被形成在其上形成有第二导通导线1022的微柱103的顶表面上。此时,第一上导线1013和第二上导线1023可以被形成为比第一导通导线1012和第二导通导线1022宽,以分别被连接到第一导通导线1012和第二导通导线1022。

[0082]

如上文描述的,不同的第一下导线1011的端部可以分别被设置在一个微柱103的两端上,或者不同的第二下导线1021的端部可以分别被设置在一个微柱103的两端上。因此,第一上导线1013通过第一导通导线1012被连接到不同的第一下导线1011中的每一个第一下导线,并且第二上导线1023通过第二导通导线1012被连接到不同的第二下导线1021中

的每一个第二下导线1021,使得第一导线101和第二导线102可以被螺旋地形成。

[0083]

第一上导线1013和第二上导线1023均被设置成多个,并且都沿着微柱103形成,由此可以被形成为平行于第二方向。优选地,第二方向是不同于第一方向的方向。例如,如图10所示,第二方向可以相对于第一方向具有预定倾斜度。此外,第一上导线1013和第二上导线1023可以彼此交替地形成。因此,在fpcb 1的图案电路层10中,可以嵌入地形成包括具有双螺旋结构的第一导线101和第二导线102的图案熔断器100。此外,在形成图案熔断器100之后,可以移除基膜11。

[0084]

同时,尽管在附图中未示出,但为了保护fpcb 1的电路图案,可以将覆盖层层压在微柱103的顶表面上。覆盖层可以是聚酰亚胺类材料的膜。

[0085]

图11是示出了根据本发明的实施例的其中起始端子1014和1024以及结束端子1015和1025被形成在第一导线101和第二导线102上的状态的立体图。

[0086]

在形成第一上导线1013和第二上导线1023之后,在第一导线101和第二导线102的起始部分处形成起始端子1014和1024,并且在第一导线101和第二导线102的结束部分处形成结束端子1015和1025。此时,第一导线101和第二导线102的起始端子1014和1024以及结束端子1015和1025都仅被暴露在图案电路层10的顶表面或底表面中的一个上。

[0087]

此外,根据本发明的实施例,第一导线101和第二导线102具有均分开地形成的起始端子1014和1024以及结束端子1015和1025。即,如图11所示,在第一导线101的起始部分处,形成第一起始端子1014,并且在第二导线102的起始部分处,分开地形成第二起始端子1024。此外,在第一导线101的结束部分处,形成第一结束端子1015,并且在第二导线102的结束部分处,分开地形成第二结束端子1025。

[0088]

图12是示出了根据本发明的实施例的其中汇流条21和22被连接到图案熔断器100的状态的示意图。

[0089]

如果第一起始端子1014、第二起始端子1024、第一结束端子1015或第二结束端子1025中的至少一个被暴露在图案电路层10的另一个表面上以便被连接到汇流条21和22,则fpcb 1的上表面和底表面应当弯曲成彼此颠倒。然后,应当进一步添加弯曲fpcb 1的工序,并且还存在弯曲部分的耐久性降低从而导致寿命缩短的问题。

[0090]

如图12所示,第一导线101的第一起始端子1014和第二导线102的第二起始端子1024被连接到一个电力汇流条21。然而,根据本发明的实施例,第一起始端子1014和第二起始端子1024都被暴露在图案电路层10的同一表面上,使得当连接到电力汇流条21时,fpcb 1的顶表面和底表面不需要弯曲成彼此颠倒。

[0091]

此外,第一导线101的第一结束端子1015和第二导线102的第二结束端子1025分别被连接到不同的感测汇流条221和222。然而,第一结束端子1015和第二结束端子1025都被暴露在图案电路层10的同一表面上,使得当连接到感测汇流条22时,fpcb 1的顶表面和底表面不需要弯曲成彼此颠倒。

[0092]

图13是示出了根据本发明的另一个实施例的其中起始端子105和结束端子106被形成在第一导线101和第二导线102上的状态的立体图。

[0093]

根据本发明的另一个实施例,第一导线101和第二导线102具有分别被形成为彼此连接的起始端子105和结束端子106。即,如图13所示,被形成在第一导线101的起始部分中的第一起始端子和被形成在第二导线102的起始部分中的第二起始端子被形成为彼此连

接。此外,被形成在第一导线101的结束部分中的第一结束端子和被形成在第二导线102的结束部分中的第二结束端子被形成为彼此连接。特别地,如图13所示,第一起始端子和第二起始端子可以被一体地形成为一个起始端子105,并且第一结束端子和第二结束端子可以被一体地形成为一个结束端子106。然而,本发明不限于此。第一起始端子和第二起始端子以及第一结束端子和第二结束端子可以分开地形成,然后通过单独的结合部(未示出)彼此结合,或者可以通过焊接或粘合剂彼此连接。此外,第一导线101和第二导线102的起始端子105和结束端子106都仅被暴露在图案电路层10的顶表面或底表面中的一个上。

[0094]

图14是示出了根据本发明的另一个实施例的其中汇流条21a和22a被连接到图案熔断器100a的状态的示意图。

[0095]

如图14所示,第一导线101和第二导线102的起始端子105被形成为彼此连接,并且因此被连接到一个电力汇流条21a。然而,第一起始端子和第二起始端子都被暴露在图案电路层10的同一表面上,然后彼此连接,使得当连接到电力汇流条21a时,fpcb 1a的顶表面和底表面不需要弯曲成彼此颠倒。

[0096]

此外,第一导线101和第二导线102的结束端子106也被形成为彼此连接,并且因此被连接到一个感测汇流条22a。然而,第一结束端子和第二结束端子都被暴露在图案电路层10的同一表面上,使得当连接到感测汇流条22a时,fpcb 1a的顶表面和底表面不需要弯曲成彼此颠倒。

[0097]

本发明所属领域的普通技术人员将理解,在不改变其技术精神或基本特征的情况下,本发明可以以其他特定形式实施。因此应当理解,上文描述的实施例在所有方面都是说明性的而不是限制性的。本发明的范围由所附权利要求来表示,而不是由上文的详细描述来表示,并且从权利要求的含义和范围及其等同概念得出的各种实施例应当被解释为被包括在本发明的范围内。

[0098]

[附图标记或符号的描述]

[0099]

1:fpcb

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

2:汇流条

[0100]

10:图案电路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11:基膜

[0101]

21:电力汇流条

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22:感测汇流条

[0102]

100:图案熔断器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

101:第一导线

[0103]

102:第二导线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

103:微柱

[0104]

104:填料

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1011:第一下导线

[0105]

1012:第一导通导线

ꢀꢀꢀꢀꢀꢀꢀ

1013:第一上导线

[0106]

1014:第一起始端子

ꢀꢀꢀꢀꢀꢀꢀ

1015:第一结束端子

[0107]

1021:第二下导线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1022:第二导通导线

[0108]

1023:第二上导线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1024:第二起始端子

[0109]

1025:第二结束端子

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1