集成的肖特基二极管相变存储器装置的制作方法

背景技术:

1、本发明涉及非易失性存储器,更具体地,涉及用于神经形态计算(neuromorphiccomputing)的忆阻装置(memristive device)。

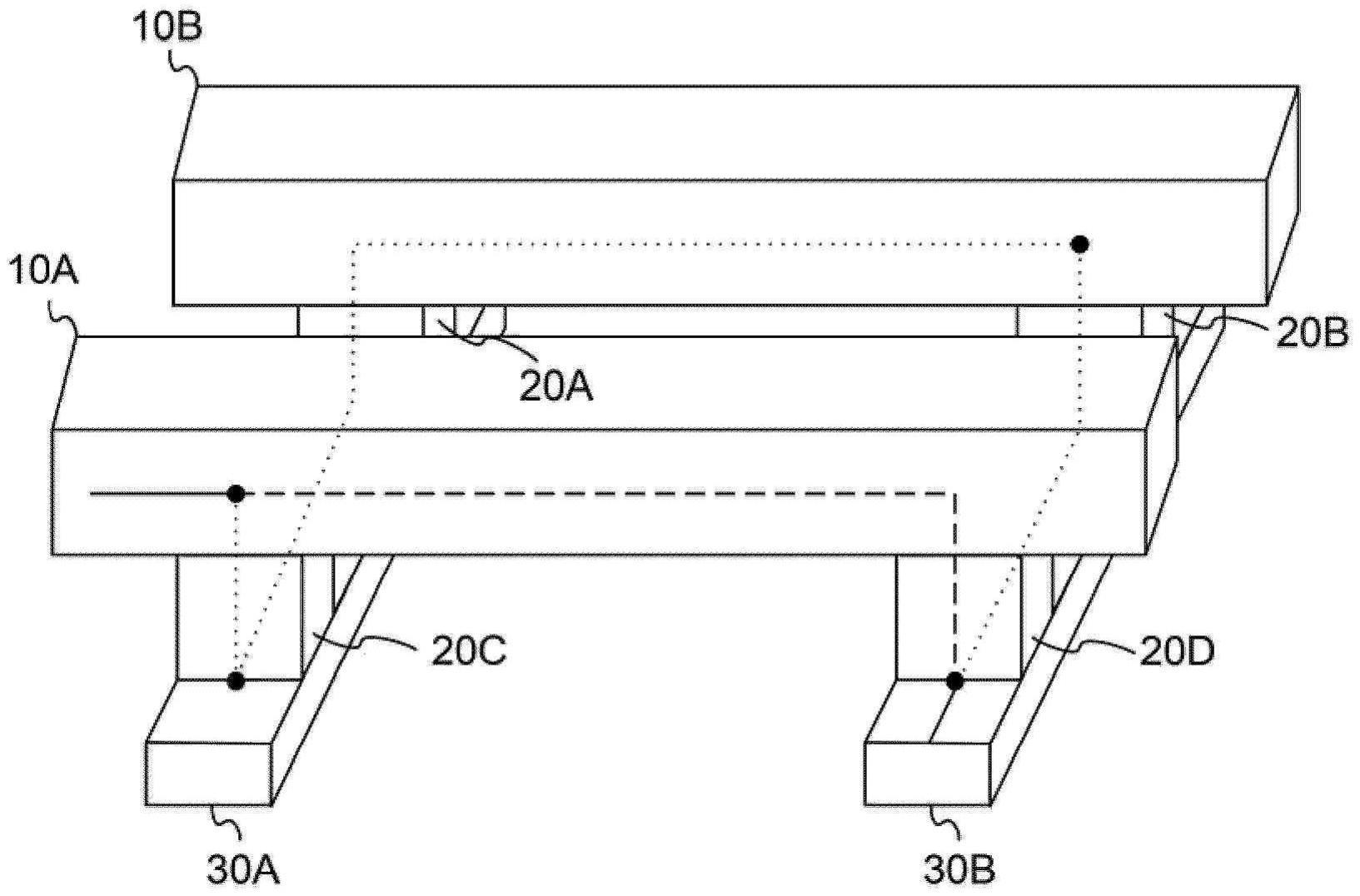

2、“机器学习”用于广泛地描述从数据学习的电子系统的主要功能。在加速的机器学习和认知科学中,人工神经网络(ann)是由动物的生物神经网络,特别是大脑,所启发的一族统计学习模型。ann可以用于估计或近似依赖于大量输入并且通常未知的系统和功能。ann结构、神经形态微芯片和超高密度非易失性存储器可以由被称为交叉式阵列(cross-bar array)的高密度、低成本电路结构形成。一种基本的交叉式阵列配置包括一组导电行线和形成为与该组导电行线交叉的一组导电列线。两组导线之间的交叉部由所谓的交叉点装置分开,交叉点装置可以由薄膜材料形成。交叉点装置可以被实现为所谓的忆阻装置。忆阻装置的特性包括非易失性、存储可变电阻值的能力、以及使用电流或电压脉冲来调高或调低电阻的能力。

技术实现思路

1、一种非易失性存储器结构可以包括相变存储器,该相变存储器包括相变材料。所述非易失性存储器结构可以包括与相变存储器串联的肖特基二极管,其中肖特基二极管的肖特基势垒是相变存储器的表面。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

2、段落[0003]的非易失性存储器结构可以具有其中所述肖特基势垒作为所述相变材料与接触之间的界面。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

3、段落[0004]的非易失性存储器结构可具有选择接触,所述接触具有功函数比相变材料的功函数低0.3-1ev的材料。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

4、段落[0004]的非易失性存储器结构可具有选定接触,所述接触具有选自钛、钼、铝、钽、钨、锰、锆及铪的材料。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

5、段落[0004]的非易失性存储器结构可具有选择接触,所述接触具有功函数比相变材料的功函数高0.3-1ev的材料。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

6、段落[0004]的非易失性存储器结构可具有选择接触,所述接触具有选自钼、氮化钛、钨、金、钴、铜、镍、钯和铱的材料。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

7、一种非易失性存储器结构可以包括位于第一接触和第二接触之间的相变材料,其中第一接触和第二接触是不同的材料。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

8、段落[0009]的非易失性存储器结构可以具有其中所述肖特基势垒作为所述相变材料与接触之间的界面。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

9、段落【0010】的非易失性存储器结构可以选择具有功函数比相变材料的功函数低0.3-1ev的材料的接触。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

10、段落【0010】的非易失性存储器结构可以选择具有从钛、钼、铝、钽、钨、锰、锆和铪中选择的材料的接触。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

11、段落【0010】的非易失性存储器结构可以选择具有功函数高于相变材料的功函数0.3-1ev的材料的接触。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

12、段落【0010】的非易失性存储器结构可以具有选择接触,该接触具有从钼、氮化钛、钨、金、钴、铜、镍、钯和铱中选择的材料。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

13、一种非易失性存储器结构可以包括多条位线和多条字线。pcm存储器结构位于所述多个位线和所述多个字线之间。pcm存储器结构可以包括位于第一接触和第二接触之间的相变材料。第一接触和第二接触是不同的材料。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

14、段落【0015】的非易失性存储器结构可以具有肖特基势垒作为相变材料和接触之间的界面。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

15、段落【0016】的非易失性存储器结构可以选择具有功函数比相变材料的功函数低0.3-1ev的材料的接触。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

16、段落【0016】的非易失性存储器结构可以选择具有从钛、钼、铝、钽、钨、锰、锆和铪中选择的材料的接触。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

17、段落【0016】的非易失性存储器结构可以选择具有功函数高于相变材料的功函数0.3-1ev的材料的接触。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

18、段落【0016】的非易失性存储器结构可以具有选择接触,该接触具有从钼、氮化钛、钨、金、钴、铜、镍、钯和铱中选择的材料。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

19、一种非易失性存储器结构可以包括多条位线和多条字线。pcm存储器结构位于所述多个位线和所述多个字线之间。pcm存储器结构可以包括相变材料和与相变存储器串联的肖特基二极管。肖特基二极管的肖特基势垒是相变存储器的表面。肖特基势垒是相变材料和接触之间的界面。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

20、段落[0021]的非易失性存储器结构可以具有其中肖特基势垒作为相变材料和接触之间的界面。这可以产生集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

21、段落[0021]的非易失性存储器结构可具有选择接触,所述接触具有功函数低于相变材料的功函数0.3-1ev的材料。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

22、段落[0021]的非易失性存储器结构可具有选定接触,所述接触具有选自钛、钼、铝、钽、钨、锰、锆及铪的材料。这可以产生p型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

23、段落[0021]的非易失性存储器结构可具有选择接触,所述接触具有功函数比相变材料的功函数高0.3-1ev的材料。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

24、段落[0021]的非易失性存储器结构可具有选定接触,所述接触具有选自钼、氮化钛、钨、金、钴、铜、镍、钯和铱的材料。这可以产生n型集成二极管-存储器结构,其可以控制电流的方向性而不会对结构的占用面积造成不利影响。

- 还没有人留言评论。精彩留言会获得点赞!