半导体结构及其制备方法、数据存储装置及数据读写装置与流程

本技术涉及半导体,特别是涉及一种半导体结构及其制备方法、数据存储装置及数据读写装置。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)是计算机常用的半导体存储器件。目前dram的存取晶体管通常采用埋入式字线的方式,但制作埋入式字线容易产生栅致漏极泄露(gate-induced drain leakage,gidl)电流。gidl是dram漏电的一个主要途径,gidl电流的大小直接取决于字线与源/漏极重叠区域的电场。

2、为了降低gidl电流,现有工艺采用功函数较低的材料(例如多晶硅)替代一部分功函数较高的金属字线材料(例如钨或氮化钛),可以有效降低前述重叠区域的电场,从而减少gidl漏电。

3、多晶硅取代的金属字线材料越多,gidl漏电越少;然而由于多晶硅的电阻率较高,当多晶硅取代部分金属字线材料时,字线的电阻随之变大,导致存取晶体管的开启速度变慢,影响器件存取速度。

技术实现思路

1、基于此,有必要针对上述背景技术中的问题,提供一种半导体结构及其制备方法、数据存储装置及数据读写装置。

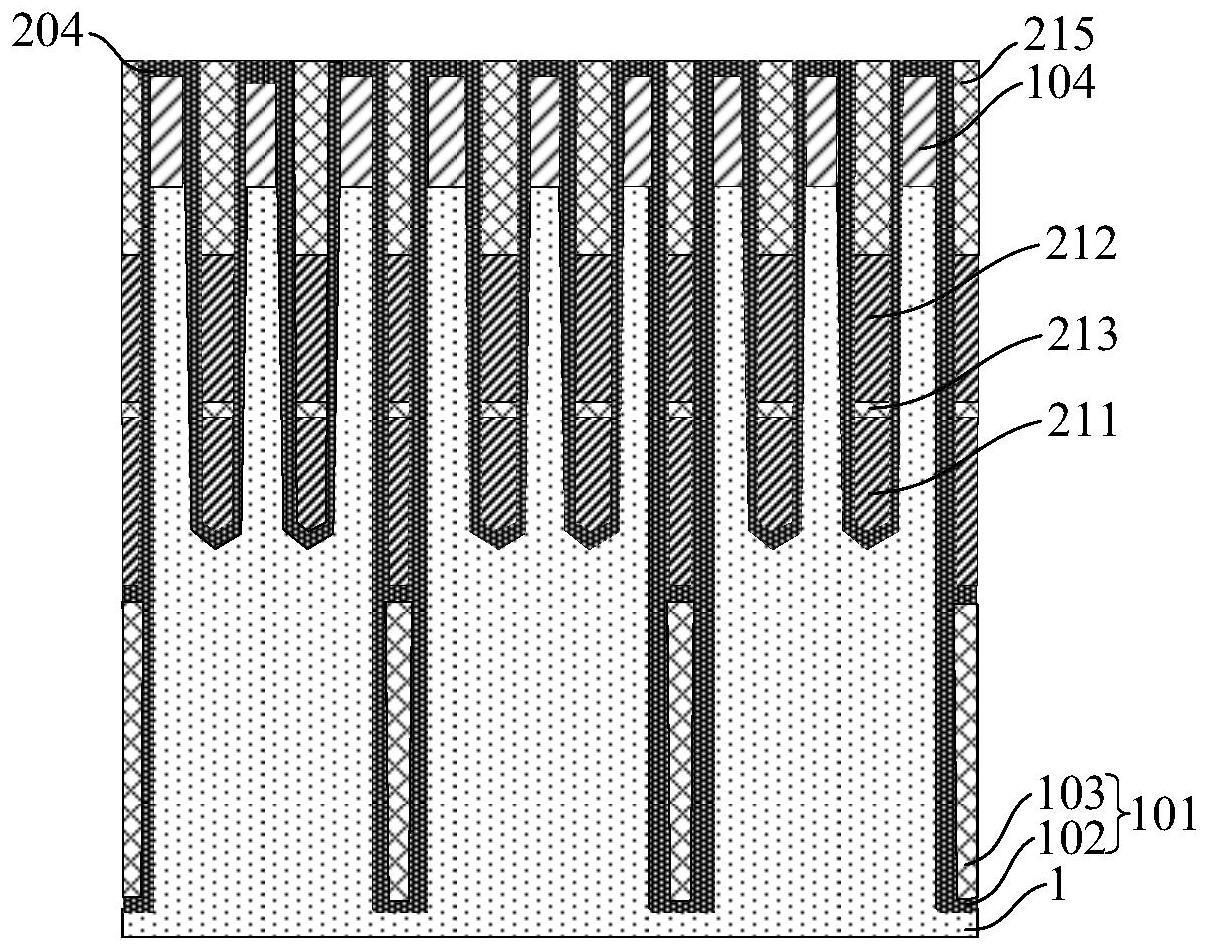

2、根据一些实施例,本技术第一方面提供一种半导体结构,包括:

3、衬底,所述衬底内形成有若干个分立的有源区;

4、沟槽,位于所述有源区内;

5、第一栅极结构,位于所述沟槽内,所述第一栅极结构上具有第一施加电压;

6、第二栅极结构,位于所述沟槽内,且位于所述第一栅极结构上方,所述第二栅极结构上具有第二施加电压,且所述第二施加电压大于所述第一施加电压;

7、绝缘隔离层,位于所述沟槽内,且位于所述第一栅极结构与所述第二栅极结构之间。

8、在其中一个实施例中,所述半导体结构还包括:

9、第一字线驱动器,与所述第一栅极结构电连接,用于向所述第一栅极结构施加所述第一施加电压;

10、第二字线驱动器,与所述第二栅极结构电连接,用于向所述第二栅极结构施加所述第二施加电压。

11、在其中一个实施例中,所述半导体结构还包括:

12、栅氧化层,位于所述沟槽的侧壁及底部;

13、所述第一栅极结构、所述绝缘隔离层及所述第二栅极结构均位于所述栅氧化层的表面。

14、在其中一个实施例中,所述半导体结构还包括:

15、顶层介质层,位于所述沟槽内,且位于所述第二栅极结构上方。

16、在其中一个实施例中,所述沟槽的数量为多个,多个所述沟槽间隔排布。

17、在其中一个实施例中,所述第一栅极结构包括第一栅极金属,所述第一栅极金属包括氮化钛、钨或多晶硅中的至少一种;

18、所述第二栅极结构包括第二栅极金属,所述第二栅极金属包括氮化钛、钨或多晶硅中的至少一种。

19、在其中一个实施例中,所述绝缘隔离层的厚度为5nm-8nm;所述绝缘隔离层包括氧化硅层或氮化硅层中的至少一种。

20、在其中一个实施例中,所述半导体结构还包括:

21、源极,位于所述有源区内,且位于所述第一栅极结构及所述第二栅极结构的一侧;

22、源极接触结构,与所述源极电连接;

23、漏极,与所述源极位于同一所述有源区内,且位于所述第一栅极结构及所述第二栅极结构的远离所述源极的一侧;

24、漏极接触结构,与所述漏极电连接。

25、根据一些实施例,本技术还提供一种半导体结构的制备方法,包括:

26、提供衬底,所述衬底内形成有若干个分立的有源区;

27、于所述有源区内形成若干个沟槽;

28、于所述沟槽内形成第一栅极结构、绝缘隔离层及第二栅极结构;其中

29、所述第二栅极结构位于所述第一栅极结构的上方,所述绝缘隔离层位于所述第一栅极结构与所述第二栅极结构之间;

30、于所述衬底内形成第一字线驱动器及第二字线驱动器,其中

31、所述第一字线驱动器与所述第一栅极结构电连接,用于向所述第一栅极结构施加所述第一施加电压;

32、所述第二字线驱动器与所述第二栅极结构电连接,用于向所述第二栅极结构施加所述第二施加电压,且所述第二施加电压大于所述第一施加电压。

33、在其中一个实施例中,所述于所述沟槽内形成第一栅极结构、绝缘隔离层及第二栅极结构,包括:

34、于所述沟槽内及所述衬底的上表面形成第一栅极金属;

35、去除位于所述衬底上表面的所述第一栅极金属及位于所述沟槽内的部分所述第一栅极金属,剩余的所述第一栅极金属即为所述第一栅极结构;

36、于所述沟槽内及所述衬底的上表面沉积绝缘隔离材料层;

37、去除位于所述衬底上表面的所述绝缘隔离材料层及位于所述沟槽内的部分所述绝缘隔离材料层,剩余的部分所述绝缘隔离材料层即为所述绝缘隔离层;

38、于所述沟槽内及所述衬底的上表面沉积第二栅极金属;

39、去除位于所述衬底上表面的所述第二栅极金属及位于所述沟槽内的部分所述第二栅极金属,剩余的所述第二栅极金属即为所述第二栅极结构。

40、在其中一个实施例中,所述于所述沟槽内及所述衬底的上表面形成第一栅极金属之前,还包括;

41、于所述沟槽的侧壁及底部形成所述栅氧化层。

42、在其中一个实施例中,所述于所述沟槽内形成第一栅极结构、绝缘隔离层及第二栅极结构,还包括:

43、于所述第二栅极结构及所述栅氧化层的表面形成所述顶层介质材料层;

44、去除位于所述第二栅极结构表面的部分所述顶层介质材料层和位于所述栅氧化层的表面的所述顶层介质材料层,剩余的所述顶层介质材料层形成所述顶层介质层。

45、在其中一个实施例中,所述于所述有源区内形成若干个沟槽之后,且所述于所述沟槽内形成第一栅极结构、绝缘隔离层及第二栅极结构之前,还包括:

46、于所述有源区内形成源极及漏极,所述源极及漏极位于所述沟槽相对的两侧。

47、根据一些实施例,本技术还提供一种数据存储装置,包括上述任一实施例提供的半导体结构。

48、根据一些实施例,本技术还提供一种数据读写装置,包括上述任一实施例提供的半导体结构。

49、本技术提供的半导体结构及其制备方法、数据存储装置及数据读写装置可以具有如下有益效果:

50、本技术实施例中的半导体结构,通过绝缘隔离层使得第一栅极结构与第二栅极结构彼此隔离,形成双栅极(dual gate)结构,同时第二栅极结构上施加的电压大于第一栅极结构上施加的电压,从而能够减少gidl漏电;第二栅极结构上施加的电压大于第一栅极结构上施加的电压还能够使得字线与源/漏极重叠区域的电子堆积增加,减少字线电阻,提升驱动电流;并且,由于gidl漏电的减少,使得在该半导体结构的字线沟槽中形成的双栅极结构的高度可以适当增加,进一步提升驱动电流,从而提升器件存取速度。

51、本技术实施例中的半导体结构的制备方法,通过在沟槽内形成第一栅极结构、绝缘隔离层及第二栅极结构,且绝缘隔离层将第一栅极结构与第二栅极结构彼此隔离,使得第一栅极结构与第二栅极结构能够形成双栅极结构,同时第二栅极结构上施加的电压大于第一栅极结构上施加的电压,从而能够减少gidl漏电;第二栅极结构上施加的电压大于第一栅极结构上施加的电压还能够使得字线与源/漏极重叠区域的电子堆积增加,减少字线电阻,提升驱动电流;并且,由于gidl漏电的减少,使得在该半导体结构的字线沟槽中形成的双栅极结构的高度可以适当增加,进一步提升驱动电流,从而提升器件存取速度。

52、本技术中提供的数据存储装置,包括前述实施例提供的半导体结构,前述半导体结构所能实现的技术效果,该数据存储装置也均能实现,此处不再详述。

53、本技术中提供的数据读写装置,包括前述实施例提供的半导体结构,前述半导体结构所能实现的技术效果,该数据读写装置也均能实现,此处不再详述。

- 还没有人留言评论。精彩留言会获得点赞!