一种高速SARADC电路的制作方法

一种高速sar adc电路

技术领域

1.本发明涉及逐次逼近型(sar)模数转换器(adc)。

背景技术:

2.逐次逼近型模数转换器以其低功耗、低延迟的特点获得了广泛应用,但是由于逐次逼近的特点,n bit分辨率的sar adc至少需要n个转换周期,因此速度较慢。尽管异步时序的sar adc在速度上有所提高,但在实际设计中n次转换周期的总时间随着pvt(process, voltage, temperature,工艺-电压-温度)corner(工艺角)变化很大,在最快、最慢的pvt corner下速度很容易就相差一倍,传统设计中将延时单元以及参考电平驱动电路的驱动能力设置在最慢corner下,使得typical(标准工艺角)以及偏快corner的参考电平驱动电路过设计,导致sar adc功耗较大。

技术实现要素:

3.本发明的目的在于提供一种高速sar adc电路,通过自动调节电路延时以及参考电压电路的电流使得异步sar adc在pvt下速度以及性能都能保持稳定,且降低功耗。

4.实现上述目的的技术方案是:一种高速sar adc电路,包括:电容dac阵列、比较器、ref电路、时钟逻辑电路和数据逻辑电路,所述ref电路连接所述电容dac阵列;所述电容dac阵列连接所述比较器的两个输入端;所述比较器连接所述时钟逻辑电路和数据逻辑电路;所述时钟逻辑电路输出比较器时钟给所述比较器;所述数据逻辑电路输出dac控制信号给所述电容dac阵列;其中,所述数据逻辑电路在n位dff单元的基础上增加额外m位dff单元,同时在n位数据处理单元的基础上额外增加m位数据处理单元,n、m均为正整数。

5.优选的,每位所述dff单元与对应的数据处理单元连接;所述数据逻辑电路包括接收采样时钟cks的延迟控制模块;m位dff单元的m位输出连接所述延迟控制模块的输入端;每位所述数据处理单元连接所述比较器;n位数据处理单元的电容dac控制输出ctl端连接所述电容dac阵列;所述延迟控制模块分别连接所述ref电路和时钟逻辑电路。

6.优选的,所述时钟逻辑电路包括非门、第一与非门、第二与非门和延时单元;所述非门的输入端接采样时钟cks;所述第一与非门的两个输入端连接所述比较器;所述第一与非门的输出端连接n+m位dff单元;所述非门的输出端、第一与非门的输出端以及m位dff单元的共同相接端连接所述

第二与非门的三个输入端;所述第二与非门的输出端连接所述延时单元的输入端;所述延时单元的输出端连接所述比较器;所述延时单元连接所述延迟控制模块。

7.优选的,采样时钟cks一方面通过相接的两个非门连接n+m位dff单元,另一方面通过一个非门连接从属于第一位dff单元的与门的一个输入端,从属于第一位dff单元的与门的另一个输入端连接所述第一位dff单元;从属于第一位dff单元的与门的输出端连接对应的数据处理单元;除第一位的其他dff单元各自的与门的两个输入端分别连接从属的dff单元以及前一个dff单元,输出端连接对应的数据处理单元。

8.优选的,还包括:数据计算单元和输出dff单元;所述数据计算单元分别连接所述延迟控制模块、采样时钟cks以及n+m位数据处理单元;所述dff单元连接所述数据计算单元,并通过一个非门连接采样时钟cks。

9.优选的,所述ref电路包括:current dac和ref buffer,所述current dac连接所述延迟控制模块和ref buffer;所述ref buffer连接所述电容dac阵列。

10.本发明的有益效果是:本发明根据芯片所处不同corner自动调整延时以及参考电平驱动电路的电流。通过插入额外的转换位检测当前sar adc的状态,额外转换位的数量可以作为转换时间余量,只需要调整转换位的数量就可以满足不同系统对sar adc误码率、鲁棒性的要求。相比于传统做法将延迟单元以及参考电平驱动电路的电流都设置到最慢corner,本发明将默认档位设置在pvt的typical corner下,在偏慢的corner下减小延时单元的时延来加快速度,并通过current dac来增加参考电平驱动电路的偏置电流,加快sar adc中的电容dac建立时间;在偏慢的corner下通过增加延时单元的时延并通过current dac来减小参考电平驱动电路的偏置电流起到节省功耗的目的。由于最慢pvt corner的统计占比很小,通过自动调节延时以及电流的方法可以有效起到满足高速应用的前提下节省功耗的目的。最后本发明统计额外转换位的数据输出,能够起到改善sar adc噪声的作用,缓解比较器在高速应用速度以及噪声性能的折衷问题,有效提升整个sar adc的速度。

附图说明

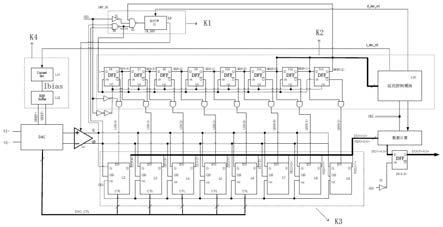

11.图1是本发明的高速sar adc电路的电路图;图2是本发明中sar adc框图;图3是本发明中以5位异步sar adc为例的时序框图图4是本发明中高速sar adc工作流程图。

具体实施方式

12.下面将结合附图对本发明作进一步说明。

13.图2为sar adc框图,主要由电容dac(digital to analog converter,数字模拟转换器)阵列、比较器、ref电路(参考电平驱动电路)、时钟逻辑电路以及数据逻辑电路构成。

ref电路连接所述电容dac阵列;电容dac阵列连接比较器的两个输入端;比较器连接述时钟逻辑电路和数据逻辑电路;时钟逻辑电路输出比较器时钟cmp_en给比较器;数据逻辑电路输出dac控制信号dac_ctl给电容dac阵列。

14.图3是以5位异步sar adc为例的时序框图。在adc的采样阶段,采样时钟cks为高电平,电容dac阵列将输入信号vin+、vin-采样到电容dac阵列中。在转换阶段,cks低电平,时钟逻辑逐个产生比较器时钟cmp_en。在图3的5 bit异步sar adc中,cmp_en产生5个高电平,其中由于每次比较器的比较时间不同,cmp_en的高电平时间也不同。图3中对bit《4》,bit《3》的时钟环路以及数据环路进行说明。其中时钟环路指的是图2中从比较器到时钟逻辑再经由比较器时钟cmp_en反馈到比较器的环路;dac环路指的是图2中从电容dac阵列到比较器再到数据逻辑最后由dac控制信号dac_ctl反馈到电容dac阵列的环路。图3中bit《4》的时钟环路从cmp_en的bit《4》上升沿开始,比较器开始比较,比较结果经过时钟逻辑模块的逻辑延时产生cmp_en下降沿;在cmp_en的下降沿比较器开始复位,复位完成后经过时钟逻辑,其延时为图3的“逻辑延时2”,触发cmp_en的上升沿,开始bit《3》的周期。在dac环路上,当cmp_en的bit《4》上升沿意味着dac已经建立完成,待获得比较器结果后经过数据逻辑电路(其延时为图3中“数据延时”)改变dac的控制信号,开始dac建立其中建立时间为图3中的“bit-3 dac建立”;为了获得较好的sar adc性能,要求bit-3 dac建立在cmp_en的bit《3》高电平上升沿之前完成。异步sar adc的转换速度直接取决于时钟环路的速度,即cmp_en要完成完整的5个周期。其组成部分包括图3的“bit-n比较器建立”,“逻辑延时1”,“比较器复位”,“逻辑延迟2”。在不同corner下,这4个部分的延时都是不同的。

15.如图1所示,本发明的高速sar adc电路,包括:电容dac阵列、比较器、ref电路、时钟逻辑电路和数据逻辑电路。图中,k1模块对应时钟逻辑电路。k2加上k3模块对应数据逻辑电路。k4模块对应ref电路。

16.数据逻辑电路在n位dff单元(i6-i10)的基础上增加额外m位dff(d触发器)单元(对应图1中i11-i13这3位dff),同时在n位数据处理单元(l2-l6)的基础上额外增加m位数据处理单元(对应图1中l7-l9),n、m均为正整数。

17.每位dff单元与对应的数据处理单元连接。数据逻辑电路包括接收采样时钟cks的延迟控制模块(delay control)l10。m位dff单元i11-i13的共同相接端连接延迟控制模块l10的输入端。每位数据处理单元连接比较器lx的q端和qb端。n位数据处理单元l2-l6的dac控制端(ctl端)连接电容dac阵列中相应的电容。延迟控制模块l10分别连接ref电路和时钟逻辑电路。

18.时钟逻辑电路包括非门i1、第一与非门i4、第二与非门i2和延时单元(delay dac)l0。非门i1的输入端接采样时钟cks。第一与非门i4的两个输入端连接比较器lx的q端和qb端。第一与非门i4的输出端连接n+m位dff单元的ck端。非门i1的输出端、第一与非门i4的输出端以及m位dff单元i11-i13的共同相接端(q端)连接第二与非门i2的三个输入端。第二与非门i2的输出端连接延时单元l0的输入端。延时单元l0的输出端连接比较器lx。延时单元l0连接延迟控制模块l10,接收控制信号d_dac_ctl。

19.采样时钟cks一方面通过相接的两个非门连接n+m位dff单元各自的rst端,另一方面通过一个非门连接从属于第一位dff单元i6的与门的一个输入端,从属于第一位dff单元i6的与门的另一个输入端连接第一位dff单元i6的q反端;从属于第一位dff单元i6的与门

的输出端连接对应的数据处理单元l2的en端。除第一位的其他dff单元i7-i13各自的与门的两个输入端分别连接从属的dff单元i7-i13的q反端以及前一个dff单元i6-i12的q端,输出端连接对应的数据处理单元l3-l9。

20.本发明还包括:数据计算单元和输出dff单元。数据计算单元分别连接延迟控制模块l10、采样时钟cks以及n+m位数据处理单元l2-l9的d端。

21.输出dff单元连接数据计算单元,并通过一个非门i5连接采样时钟cks。

22.ref电路包括:current dac( 电流型数模转换器)和ref buffer(参考电压驱动电路),current dac l11连接延迟控制模块l10,接收控制信号i_dac_ctl来调整ref buffer l12的偏置电流ibias。ref buffer l12连接电容dac阵列,提供vref+和vref-。

23.如图4所示,为高速sar adc流程图,下面将结合图1以及图4对本发明进行说明。

24.当电路上电或者复位的时候,延迟控制模块l10处于默认配置,让delay dac l0以及current dac l11处于默认档位。在该档位下,sar adc在典型corner(pvt都是中间档位)下刚好能进行n次正常转换(图1中的5次)以及m-1次额外转换(图1中的2次)。对于处在某一个未知corner的sar adc电路,电路在该默认模式下尝试进行5次正常转换和3次额外转换。其过程如下:采样结束后,cmp_en的上升沿触发比较器lx开始比较,当比较结束后k1模块中的valid信号(比较器比较完成信号,来自第一与非门i4的输出端)获得一个上升沿,并触发相应的dff(i6-i13)输出q=1;在q=1之前,对应位的len《n》或者lren《m》为高电平,让对应的逻辑单元(k2模块中的l2-l9)处于使能状态,存储该位的比较结果,并改变对应的dac开关。其中上述逻辑单元包括2个锁存器来锁存q,qb的信号,当en信号为1时,2个锁存器分别连接到q、qb信号进行锁存工作,d端为q对应锁存器的正向信号输出;当en信号为0时,锁存器断开与q、qb的连接,2个锁存器保持状态,输出d也维持原本状态;rst信号为复位信号,当rst高电平时,让锁存器复位状态;l2-l6内还包含dac控制信号,根据锁存器的结果经过内部逻辑,输出dac控制信号dac_ctl。

25.在尝试n+m次转换后,在下一次cks的上升沿,图1的延迟控制模块l10统计额外m次转换的完成状态,即延时控制模块l10统计dff单元i10,i11,i12的q端输出是否为1。当i10、i11的q=1,q12的q=0,则current dac以及delay dac都不做调整,此时已经收敛到合适的值;当i10、i11、q12的q=1,说明延迟太小,则减小current dac的电流并增加delay dac的延时;当i11的q=0,说明延迟太大,则增加current dac的电流并减小delay dac的延时。同步调整current dac以及delay dac能够在获得合适延时的同时调整dac建立速度,起到节省参考电平驱动电路功耗的作用。

26.调整完成current dac以及delay dac之后,根据转换完成的情况获得数据输出。将正常转换的最后1bit(lsb),如图1的do《0》以及rdo《2:0》做统计。在cks上升沿时刻,dff(i10-i13)的q=1对应的l6-l9输出do《0》、rdo《2:0》为有效值,统计有效值中1的个数,当1的额数占有效值多数,则do1《0》=1,否则do1《0》=0。例如ben《0》=bren《0》=bren《1》=1, bren《2》=0,则有效值为3;当do《0》=1,rdo《0》=rdo《1》=0,则数据1不大于3

÷

2=1.5,因此do1《0》=1,do1《4:1》=do《4:1》。do1《4:0》经过输出dff单元后,adc输出dout《4:0》,sar adc完成本次转换。根据此逻辑能够对最后1bit进行平均,改善adc的噪声性能。

27.综上,本发明通过插入额外的转换位检测当前sar adc的状态,图1中插入额外3位

额外转换位作为例子,实际上转换位的个数可以根据系统对sar adc的要求调节,以达到设计转换时间余量的目的。当系统的误码率要求较高可以插入2位以上的额外转换位来获得较大时间余量;当系统误码率要求较低可以将额外转换位减小到2位来得到较高sar adc速度。

28.以上实施例仅供说明本发明之用,而非对本发明的限制,有关技术领域的技术人员,在不脱离本发明的精神和范围的情况下,还可以作出各种变换或变型,因此所有等同的技术方案也应该属于本发明的范畴,应由各权利要求所限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1