具有嵌入式芯片的动态随机存取存储器装置及其制造方法与流程

本发明涉及一种整合动态随机存取存储器与逻辑芯片的方法,且特别涉及一种具有嵌入式芯片的动态随机存取存储器装置及其制造方法。

背景技术:

1、在目前的半导体技术中,若是要整合动态随机存取存储器(dram)与逻辑芯片,主要有两种方式。

2、一种是在封装过程中使用重布线载板(rdl interposer),将dram芯片与逻辑芯片分别接合到重布线载板,再将重布线载板接合至印刷电路板。

3、另一种是利用wow(wafer on wafer)技术,将dram芯片与逻辑芯片进行晶片级接合,再利用硅穿孔(tsv)和重布线(rdl)制作工艺完成内部的互连。

技术实现思路

1、本发明提供一种具有嵌入式芯片的动态随机存取存储器(dram)装置,能将薄型的逻辑芯片直接嵌入具有动态随机存取存储器的半导体芯片,使动态随机存取存储器与逻辑芯片整合至同一半导体芯片中。

2、本发明另提供一种具有嵌入式芯片的动态随机存取存储器装置的制造方法,能在前端制作工艺中整合逻辑元件与动态随机存取存储器,不需要复杂的后端制作工艺或者封装技术。

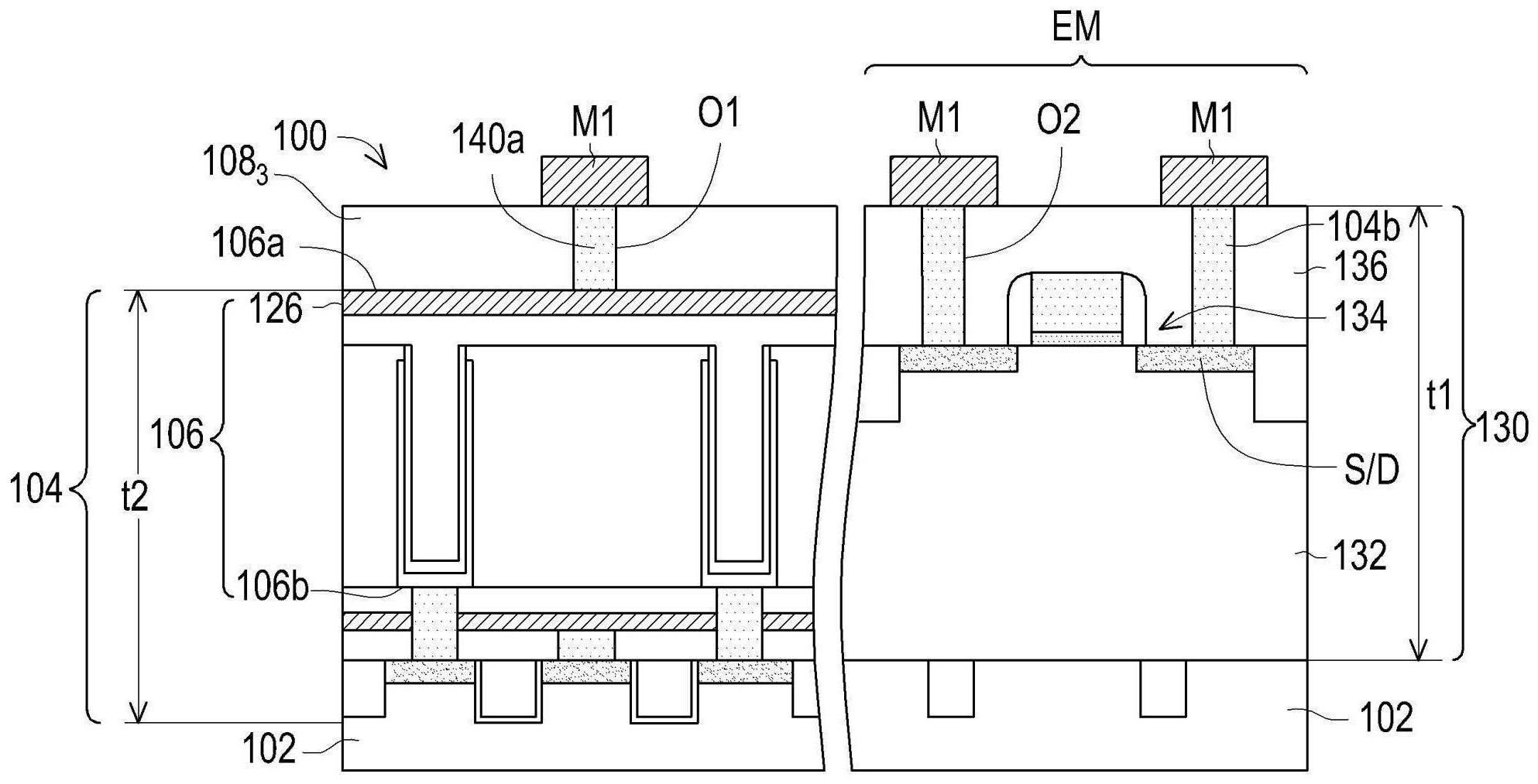

3、本发明的具有嵌入式芯片的动态随机存取存储器装置,包括半导体芯片与逻辑芯片。半导体芯片包括第一基板、动态随机存取存储器以及嵌入区域。动态随机存取存储器形成于第一基板上,并具有位线以及设置在位线上的电容器。嵌入区域定义在动态随机存取存储器以外的半导体芯片中,且嵌入区域的底部在第一基板的表面或表面以下。逻辑芯片则是嵌入在所述嵌入区域,其中逻辑芯片包括第二基板以及形成于第二基板上的逻辑元件,且第二基板的底部位于第一基板的表面或表面以下。

4、在本发明的一实施例中,上述逻辑芯片的厚度小于或等于上述动态随机存取存储器的厚度。

5、在本发明的一实施例中,上述逻辑芯片的第二基板包括硅基底或soi基底。

6、在本发明的一实施例中,上述半导体芯片包括覆盖电容器的第一内层介电层,上述逻辑芯片包括覆盖逻辑元件的第二内层介电层,且上述第一内层介电层的顶面与上述第二内层介电层的顶面共平面。

7、在本发明的一实施例中,上述动态随机存取存储器装置还可包括第一金属层,形成在第一内层介电层与第二内层介电层上。

8、在本发明的一实施例中,上述动态随机存取存储器装置还可包括绝缘材料,介于逻辑芯片与半导体芯片之间,以使逻辑芯片固定在半导体芯片的第一基板上。

9、在本发明的一实施例中,上述嵌入区域包括形成于第一基板中的凹槽,且第二基板的底面接触上述凹槽的底面。

10、在本发明的一实施例中,上述第二基板的表面位于上述电容器的底面与顶面之间。

11、本发明的具有嵌入式芯片的动态随机存取存储器装置的制造方法,包括提供具有动态随机存取存储器的半导体芯片,所述半导体芯片包括第一基板以及形成于第一基板上的动态随机存取存储器,其中所述动态随机存取存储器包括位线以及设置在位线上的电容器。然后,在所述动态随机存取存储器以外的半导体芯片中定义嵌入区域,且所述嵌入区域的底部位于第一基板的表面或在所述表面以下。将逻辑芯片嵌入所述嵌入区域,其中逻辑芯片包括第二基板以及形成于第二基板上的逻辑元件。在所述半导体芯片与所述逻辑芯片上沉积绝缘材料,以使逻辑芯片固定在半导体芯片的第一基板上。之后,形成多个导电插塞,分别与所述电容器以及所述逻辑元件连接,再在半导体芯片与逻辑芯片上形成第一金属层,以形成分别经由导电插塞电连接至电容器与逻辑元件的线路。

12、在本发明的另一实施例中,上述半导体芯片还包括至少一第一内层介电层,形成于第一基板与电容器上。

13、在本发明的另一实施例中,定义上述嵌入区域的方法包括蚀刻去除第一内层介电层。

14、在本发明的另一实施例中,定义上述嵌入区域的方法包括蚀刻去除第一内层介电层,以露出第一基板的表面,然后蚀刻去除部分露出的所述第一基板,以形成凹槽。

15、在本发明的另一实施例中,形成上述多个导电插塞的步骤包括形成与所述电容器连接的多个第一导电插塞以及形成分别与逻辑元件以及动态随机存取存储器的周边电路连接的多个第二导电插塞,其中第二导电插塞的高度大于电容器的高度。

16、在本发明的另一实施例中,形成上述多个导电插塞之前,还可包括利用化学机械平坦化方法研磨所述绝缘材料。

17、在本发明的另一实施例中,上述逻辑芯片还包括第二内层介电层覆盖所述逻辑元件,并在沉积上述绝缘材料之后还可包括回蚀刻所述绝缘材料,以减少半导体芯片与逻辑芯片的表面高低差,然后利用化学机械平坦化方法将所述表面高低差相除后,再研磨至所述多个导电插塞所需的高度即停。

18、在本发明的另一实施例中,上述回蚀刻绝缘材料之前还可包括形成掩模层遮蔽上述动态随机存取存储器上的绝缘材料并暴露出上述第二内层介电层上的绝缘材料。

19、基于上述,本发明使用薄型的逻辑芯片,直接将其嵌入半导体芯片中,由于半导体芯片已形成有动态随机存取存储器,且动态随机存取存储器的电容器一般有约2μm高的电容器,所以逻辑芯片只要厚度控制在略大于或接近电容器的高度,不需要复杂的后端制作工艺或者封装技术,即可将逻辑芯片安装于其中。即使逻辑芯片的厚度远大于电容器的高度,也可通过在基板中形成凹槽的方式,将逻辑芯片嵌入凹槽中,再利用如回蚀刻以及化学机械平坦化方法等,就可以在前端制作工艺中整合逻辑元件与动态随机存取存储器,毋须要复杂的后端制作工艺或者封装技术。

20、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

技术特征:

1.一种具有嵌入式芯片的动态随机存取存储器装置,包括:

2.如权利要求1所述的具有嵌入式芯片的动态随机存取存储器装置,其中所述逻辑芯片的厚度小于或等于所述动态随机存取存储器的厚度。

3.如权利要求1所述的具有嵌入式芯片的动态随机存取存储器装置,其中所述逻辑芯片的所述第二基板包括硅基底或soi基底。

4.如权利要求1所述的具有嵌入式芯片的动态随机存取存储器装置,其中所述半导体芯片包括覆盖所述电容器的第一内层介电层,所述逻辑芯片包括覆盖所述逻辑元件的第二内层介电层,且所述第一内层介电层的顶面与所述第二内层介电层的顶面共平面。

5.如权利要求4所述的具有嵌入式芯片的动态随机存取存储器装置,还包括第一金属层,形成在所述第一内层介电层与所述第二内层介电层上。

6.如权利要求1所述的具有嵌入式芯片的动态随机存取存储器装置,还包括绝缘材料,介于所述逻辑芯片与所述半导体芯片之间,以使所述逻辑芯片固定在所述半导体芯片的所述第一基板上。

7.如权利要求1所述的具有嵌入式芯片的动态随机存取存储器装置,其中所述嵌入区域包括形成于所述第一基板中的凹槽,且所述第二基板的底面接触所述凹槽的底面。

8.如权利要求7所述的具有嵌入式芯片的动态随机存取存储器装置,其中所述第二基板的表面位于所述电容器的底面与顶面之间。

9.一种具有嵌入式芯片的动态随机存取存储器装置的制造方法,包括:

10.如权利要求9所述的具有嵌入式芯片的动态随机存取存储器装置的制造方法,其中所述半导体芯片还包括至少一第一内层介电层,形成于所述第一基板与所述电容器上。

11.如权利要求10所述的具有嵌入式芯片的动态随机存取存储器装置的制造方法,其中定义所述嵌入区域的方法包括蚀刻去除所述第一内层介电层。

12.如权利要求10所述的具有嵌入式芯片的动态随机存取存储器装置的制造方法,其中定义所述嵌入区域的方法包括:

13.如权利要求12所述的具有嵌入式芯片的动态随机存取存储器装置的制造方法,其中形成多个导电插塞的步骤包括:

14.如权利要求9所述的具有嵌入式芯片的动态随机存取存储器装置的制造方法,其中形成所述多个导电插塞之前,还包括利用化学机械平坦化方法研磨所述绝缘材料。

15.如权利要求9所述的具有嵌入式芯片的动态随机存取存储器装置的制造方法,其中所述逻辑芯片还包括第二内层介电层覆盖所述逻辑元件,并在沉积所述绝缘材料之后还包括:

16.如权利要求15所述的具有嵌入式芯片的动态随机存取存储器装置的制造方法,其中回蚀刻所述绝缘材料之前,还包括形成掩模层遮蔽所述动态随机存取存储器上的所述绝缘材料并暴露出所述第二内层介电层上的所述绝缘材料。

技术总结

本发明公开一种具有嵌入式晶片芯片的动态随机存取记忆体存储器装置及其制造方法,其中具有嵌入式芯片的动态随机存取存储器装置包括半导体芯片与逻辑芯片。半导体芯片包括第一基板、动态随机存取存储器以及嵌入区域。动态随机存取存储器形成于第一基板上,并具有位线以及设置在位线上的电容器。嵌入区域定义在动态随机存取存储器以外的半导体芯片中,且嵌入区域的底部在第一基板的表面或表面以下。逻辑芯片则是嵌入在所述嵌入区域,其中逻辑芯片包括第二基板以及形成于第二基板上的逻辑元件,且第二基板的底部位于第一基板的表面或表面以下。

技术研发人员:张立鹏,张三荣

受保护的技术使用者:力晶积成电子制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!