逐次逼近型模数转换器的制作方法

1.本发明涉及集成电路设计领域,特别是涉及一种逐次逼近型模数转换器。

背景技术:

2.高精度逐次逼近(successive approximation,sar)adc是一种非常常用的adc,近些年来,由于sar adc应用的不断推广,研究的逐渐深入,其精度和速度不断取得突破。

3.通用的sar adc主体架构分为三部分,分别是dac、比较器、sar逻辑;其中,sar adc中的核心架构dac的实现主要分为电容式和电阻式,一般在高精度sar adc中会选用电容式dac或者电容和电阻组合式dac,精度大于12bit以上的通常会使用全电容式dac,且将电容矩阵设计为分段式电容阵列以压缩电容的面积,12bit左右一般会分两段,即高权重位段和低权重位段,14bit~18bit一般会分三段,即高权重位段、中权重位段和低权重位段,每段之间以桥接电容为分界点。比较器为了实现高速高精度的性能,一般会使用预防大器和重建立锁存器结构,而且预防大器会使用多级放大以识别微弱信号。

4.随着应用的不断推广,部分应用对sar adc的精度和速度要求也越来越苛刻,sar adc的设计也面临着诸多挑战。在以上介绍的三个部分中,高速高精度比较器是设计高速高精度sar adc的核心之一,高精度意味着比较器要识别的信号非常小,高速也就是比较器的比较时间要非常短,而实现高增益的预放大器带宽必然会下降,特别是在低权重位的比较过程中,等效到比较器输入端的信号都非常微弱,并且比较器容易出现亚稳态,这样在设计中,必须着重优化比较器的设计,权衡各项指标,提高比较精度,这使得设计难度大大提高。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种逐次逼近型模数转换器,用于解决现有技术中优化比较器的比较精度难度大的问题。

6.为实现上述目的及其他相关目的,本发明提供一种逐次逼近型模数转换器,所述逐次逼近型模数转换器包括:dac电路、比较电路及sar逻辑电路;所述dac电路包括第一dac模块及第二dac模块,二者结构相同,均包括高权重位段、中权重位段、低权重位段及并列低权重位段,用于对输入电压进行采样和转换,并在转换阶段,依次执行高权重位段的转换、中权重位段的转换、低权重位段的转换、低权重位段的复位及并列低权重位段的转换;所述比较电路连接所述第一dac模块及所述第二dac模块的高权重位段,用于对各权重位段输出的电压进行比较;所述sar逻辑电路连接于所述比较电路和所述dac电路之间,用于根据所述比较电路输出的比较结果产生相应控制信号,及获取各权重位段的转换结果,并对低权重位段和并列低权重位段的转换结果进行互相校验,以得到低权重位的最终转换结果。

7.可选地,所述高权重位段、所述中权重位段及所述低权重位段均为电容型结构,所述并列低权重位段为电容型结构或电阻型结构;其中,所述高权重位段与所述中权重位段

之间通过一桥接电容连接,所述中权重位段与所述低权重位段和所述并列低权重位段之间通过一个桥接电容及两个桥接开关连接,所述高权重位段的输出端通过一开关连接共模电压,所述低权重位段的输出端通过一电容接参考地。

8.可选地,所述并列低权重位段为电容型结构,所述高权重位段、所述中权重位段、所述低权重位段及所述并列低权重位段的结构相同,均包括至少一个电容,各电容的上极板作为对应权重位段的输出端,下极板分别通过三个开关连接对应输入电压、参考电压及参考地。

9.可选地,所述高权重位段和所述中权重位段的结构相同,均包括至少一个电容,各电容的上极板作为对应权重位段的输出端,下极板分别通过三个开关连接对应输入电压、参考电压及参考地。

10.可选地,所述低权重位段包括至少一个电容,各电容的上极板作为低权重位段的输出端,下极板分别通过三个开关连接参考地、参考电压及参考地。

11.可选地,所述低权重位段包括至少一个电容,各电容的上极板作为低权重位段的输出端,下极板分别通过两个开关连接参考电压及参考地。

12.可选地,所述并列低权重位段为电容型结构,其与所述低权重位段的结构相同。

13.可选地,所述并列低权重位段为电阻型结构,包括至少两个分压电阻及至少一个控制开关,各分压电阻串联于参考电压和参考地之间,各控制开关的一端连接对应相邻两分压电阻的连接节点处,另一端彼此相连并作为所述并列低权重位段的输出端。

14.可选地,所述第一dac模块中的所述并列低权重位段和所述第二dac模块中的所述并列低权重位段共用分压电阻。

15.如上所述,本发明的一种逐次逼近型模数转换器,通过在常规三段式结构中增设一并列低权重位段,使得低权重位段和并列低权重位段的转换结果可以互相校验,从而提高低权重位转换结果的可靠性,降低了对比较器高精度的要求,使得高速高精度sar adc的设计变得更容易。

附图说明

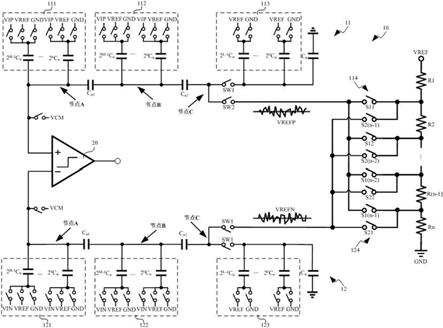

16.图1显示为一种高精度逐次逼近型模数转换器的结构示意图。

17.图2显示为本发明第一示例所述逐次逼近型模数转换器的结构示意图。

18.图3显示为本发明第二示例所述逐次逼近型模数转换器的结构示意图。

19.图4显示为本发明第三示例所述逐次逼近型模数转换器的结构示意图。

20.图5显示为本发明第四示例所述逐次逼近型模数转换器的结构示意图。

21.图6显示为本发明第五示例所述逐次逼近型模数转换器的结构示意图。

22.元件标号说明:10 dac电路,11第一dac模块,12第二dac模块,111、121高权重位段,112、122中权重位段,113、123低权重位段,114、124并列低权重位段,20比较电路,30 sar逻辑电路。

具体实施方式

23.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实

施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

24.请参阅图1至图6。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,虽图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的形态、数量及比例可为一种随意的改变,且其组件布局形态也可能更为复杂。

25.在高速高精度sar adc设计中,dac和高速高精度比较器是关键,两个电路在设计上是独立的,但是工作上是联动的;工作时,比较器是用来区分dac输出端的高精度信号。虽然比较器的高速度要求是adc在每一个转换阶段都需要,但根据sar adc的工作原理,比较器的高精度却并不是一直都需要,只有在低位比较时,比较器的高精度才最关键。

26.具体分析如下:图1 是一种高精度sar adc(输出位数大于14bit)的实现方式,为了简化省略了sar逻辑电路,其中dac为三段式电容型结构,高权重位段dac1实现h bit,中权重位段dac2实现m bit,低权重位段dac3实现l bit,总共为h+m+l=n位dac。

27.如图1所示,输入信号vin、vip首先被采样到电容的下极板,此时电容的上极板连接到共模电压vcm,然后adc开始转换,此时电容的上极板与共模电压vcm断开,并连接到比较器的输入端,即图1中节点a连接到比较器的输入端,转换逐步从高权重位段dac1到中权重位段dac2,最后再到低权重位段dac3;在转换过程中,节点a的差分电压会逐步减小,即在dac1转换阶段节点a的差分电压会较大,而在dac3转换阶段节点a的差分电压会较小,这就意味着在转换过程中比较器输入端的电压越来越小,在dac3转换阶段达到很小,此时比较器就要求在较短时间内识别这个较小信号,也就是此阶段比较器的精度要求非常高而且很容易进入亚稳态,特别是dac3的最低权重位(lsb),此时对比较器精度要求达到最高;基于以上分析可知,对比较器精度要求最高的其实是在dac3转换阶段。

28.而且,比较器在dac1转换阶段如果出现比较出错的情况,dac2和dac3转换阶段可以逐步校正,在dac2转换阶段如果出现比较出错的情况,dac3转换阶段可以校正,但是一旦在dac3转换阶段出现比较出错的情况,就没有更低位来校正了。

29.鉴于此,申请人提出了本发明,通过提高低权重位转换结果的可靠性,来降低对比较器高精度的要求,从而使得高速高精度sar adc的设计变得更容易。

30.如图2-图6所示,本实施例提供一种逐次逼近型模数转换器,所述逐次逼近型模数转换器包括:dac电路10、比较电路20及sar逻辑电路30;其中,所述dac电路10包括第一dac模块11及第二dac模块12。

31.所述第一dac模块11包括高权重位段111、中权重位段112、低权重位段113及并列低权重位段114,用于对正相输入电压vip进行采样和转换;在采样阶段,所述第一dac模块11利用各权重位段对所述正相输入电压vip进行采样;在转换阶段,所述第一dac模块11依次执行高权重位段111的转换、中权重位段112的转换、低权重位段113的转换、低权重位段113的复位及并列低权重位段114的转换。实际应用中,可通过将所述低权重位段113中各权重电容的下极板接参考地gnd实现对其进行复位。

32.具体的,所述高权重位段111、所述中权重位段112及所述低权重位段113均为电容型结构,所述并列低权重位段114为电容型结构或电阻型结构;其中,所述高权重位段111与所述中权重位段112之间通过一桥接电容c

a1

连接,所述中权重位段112与所述低权重位段

113和所述并列低权重位段114之间通过一个桥接电容c

a2

及两个桥接开关sw1、sw2连接,所述高权重位段111的输出端通过一开关连接共模电压vcm,所述低权重位段113的输出端通过一电容接地。需要说明的是,此处所述“中权重位段112与低权重位段113和并列低权重位段114之间通过一个桥接电容c

a2

及两个桥接开关sw1、sw2连接”是指“中权重位段112与低权重位段113之间通过桥接电容c

a2

及桥接开关sw1连接,同时中权重位段112与并列低权重位段114之间通过桥接电容c

a2

及桥接开关sw2连接”。

33.作为第一示例,所述并列低权重位段114为电容型结构,所述高权重位段111、所述中权重位段112、所述低权重位段113及所述并列低权重位段114的结构相同,均包括至少一个电容,各电容的上极板作为对应权重位段的输出端,下极板分别通过三个开关连接正相输入电压vip、参考电压vref及参考地gnd(如图2所示)。

34.本示例中,所述高权重位段111为h bit的dac,包括h个电容,其中第i个电容的值定义为2

i-1cu

,i为不大于h的自然数(不包括0);各电容的上极板连接在一起形成第一节点a,下极板分别通过一开关连接正相输入电压vip、参考电压vref及参考地gnd。所述中权重位段112为m bit的dac,包括m个电容,其中第j个电容的值定义为2

j-1cu

,j为不大于m的自然数(不包括0);各电容的上极板连接在一起形成第二节点b,下极板分别通过一开关连接正相输入电压vip、参考电压vref及参考地gnd。所述高权重位段111与所述中权重位段112的输出端(各电容的上极板)之间通过桥接电容c

a1

连接。所述低权重位段113和所述并列低权重位段114为l bit的dac,均包括l个电容,其中第k个电容的值定义为2

k-1cu

,k为不大于l的自然数(不包括0);各电容的上极板连接在一起形成第三节点c,下极板分别通过一开关连接正相输入电压vip、参考电压vref及参考地gnd。所述低权重位段113的输出端(各电容的上极板)通过一电容(电容值为cu)接地,同时,所述中权重位段112与所述低权重位段113的输出端(各电容的上极板)之间通过桥接电容c

a2

和桥接开关sw1连接,所述中权重位段112与所述并列低权重位段114的输出端(各电容的上极板)之间通过桥接电容c

a2

和桥接开关sw2连接。同一权重段中各电容的值依次呈2倍关系,各权重段中权重最小的电容的值相等,可定义为单位电容cu。需要说明的是,本示例采用四段式电容型结构实现了一个n位adc的设计,其中,高权重位段111实现h bit,中权重位段112实现m bit,低权重位段113实现l bit,并列低权重位段114也实现l bit(低权重位段113和并列低权重位段114均是实现低权重位dac功能),故总共为n=h+m+l位dac。

35.作为第二示例,所述并列低权重位段114为电容型结构,本示例与第一示例的区别在于所述低权重位段113和所述并列低权重位段114;本示例中,所述低权重位段113和所述并列低权重位段114的结构相同,均包括至少一个电容,各电容的上极板作为对应权重位段的输出端,下极板分别通过三个开关连接参考地gnd、参考电压vref及参考地gnd(如图3所示)。

36.作为第三示例,所述并列低权重位段114为电容型结构,本示例与第一示例的区别在于所述低权重位段113和所述并列低权重位段114;本示例中,所述低权重位段113和所述并列低权重位段114的结构相同,均包括至少一个电容,各电容的上极板作为对应权重位段的输出端,下极板分别通过两个开关连接参考电压vref及参考地gnd(如图4所示)。

37.作为第四示例,所述并列低权重位段114为电阻型结构,本示例与第一示例的区别在于所述低权重位段113和所述并列低权重位段114,其中,所述低权重位段113包括至少一

个电容,各电容的上极板作为低权重位段113的输出端,下极板分别通过三个开关连接参考地gnd、参考电压vref及参考地gnd;所述并列低权重位段114包括至少两个分压电阻及至少一个控制开关,各分压电阻串联于参考电压vref和参考地gnd之间,各控制开关的一端连接对应相邻两分压电阻的连接节点处,另一端彼此相连并作为所述并列低权重位段114的输出端。可选地,所述第一dac模块11中的所述并列低权重位段114和所述第二dac模块12中的所述并列低权重位段124共用分压电阻(如图5所示)。

38.本示例中,利用电阻型结构的并列低权重位段114与全电容型结构的低权重位段113的架构差别较大,两种架构并列权重比较时,机制会有差别,这样出现亚稳态的概率会小很多,从而降低比较器发生亚稳态的概率。另外,采用电阻型结构的并列低权重位段114,可以利用其本身的随机注入热噪声(白噪声)将处于亚稳态的比较结果拉高或拉低,从而消除比较器可能存在的亚稳态带来的影响。

39.作为第五示例,所述并列低权重位段114为电阻型结构,本示例与第四示例的区别在于所述低权重位段113,其中,所述低权重位段113包括至少一个电容,各电容的上极板作为低权重位段113的输出端,下极板分别通过两个开关连接参考电压vref及参考地gnd(如图6所示)。

40.需要说明的是,第一示例中,所述低权重位段113和所述并列低权重位段114既参与采样,又参与转换;而第二示例至第五示例中,所述低权重位段113和所述并列低权重位段114不参与采样,仅参与转换。

41.所述第二dac模块12与所述第一dac模块11的结构相同,区别在于将所述第一dac模块11接收的正相输入电压vip替换为相应的反相输入电压vin(差分结构,极性相反),具体结构在此不一一赘述。

42.以第五示例所述结构为例,对本实施例所述dac电路的转换过程进行说明。具体转换过程如下:开始转换前,桥接开关sw1默认导通、sw2默认断开,输入电压vin、vip首先被采样到dac电容的下极板,此时上极板连接到共模电压vcm;然后adc开始转换,首先进入高权重位的转换阶段,对应高权重位输出h-bit,记为dout_h《h-1:0》;然后进入中权重位的转换阶段,对应中权重位输出m-bit,记为dout_m《m-1:0》;接着进入低权重位的转换阶段,对应低权重位输出l-bit,记为dout_c《l-1:0》;低权重位转换完成后,对应低权重位段的各权重电容开关复位,节点a、b、c的电压恢复到中权重位转换阶段结束时的状态;然后桥接开关sw2导通、sw1断开,进入并列低权重位的转换阶段,对应依然是低权重位输出l-bit,记为dout_r《l-1:0》。

43.此时有两个低权重位输出,由于在低权重位的转换阶段,比较器容易比较出错且容易进入亚稳态,而由于并列低权重位段的引入,其与低权重位段具有相同的权重,因此对应输出比较结果具有相同的表征输入电压低l-bit大小的能力,因此,利用并列低权重位段对应的低权重位输出dout_r《l-1:0》和低权重位段对应的低权重位输出结果dout_c《l-1:0》互相校准,并将校准后得到的结果记为dout_l《l-1:0》,和dout_h《h-1:0》、dout_m《m-1:0》共同作为sar adc的最终输出。具体表达如下:dout_l《l-1:0》 = dout_c《l-1:0》

ꢀ⊙ꢀ

dout_r《l-1:0》;dout=2

(l+m)

·

dout_h《h-1:0》 + 2

l

·

dout_h《m-1:0》 + dout_l《l-1:0》。

44.本实施例中,通过并列低权重位段的设计,使得低权重位进行两次转换,利用两次转换结果互相校验,大大提高了低权重位转换结果的可靠性,从而降低对比较器的高精度要求。

45.所述比较电路20连接所述第一dac模块11的高权重位段111及所述第二dac模块12的高权重位段121,用于对各权重位段输出的电压进行比较。

46.具体的,所述比较电路20采用比较器实现,其中,所述比较器的正相输入端连接所述第一dac模块11的第一节点a,所述比较器的反相输入端连接所述第二dac模块12的第一节点a,并输出比较结果;在所述比较器进入亚稳态时,所述sar逻辑电路30控制所述比较器进行强制复位。实际应用中,所述比较器的输入端极性与输入电压的对应关系可互换,不以本实施例为限。

47.所述sar逻辑电路30连接于所述比较电路20和所述dac电路10之间,用于根据所述比较电路20输出的比较结果产生相应控制信号,及获取各权重位段的转换结果,并对低权重位段和并列低权重位段的转换结果进行互相校验,以得到低权重位的最终转换结果。

48.具体的,所述sar逻辑电路30产生各开关的控制信号,用于采样及转换控制。所述sar逻辑电路30还接收各权重位段的转换结果,将高权重位段的转换结果作为高权重位的最终转换结果,将中权重位段的转换结果作为中权重位的最终转换结果,及对低权重位段和并列低权重位段的转换结果进行互相校验,以得到低权重位的最终转换结果。

49.更具体的,若低权重位段和并列低权重位段的转换结果一致,则选择其中之一作为低权重位的最终转换结果;若低权重位段和并列低权重位段的转换结果不一致,则选择亚稳态标志位为“0”的转换结果作为低权重位的最终转换结果;其中,在比较器进入亚稳态时,比较器会进行强制复位,此时将亚稳态标志位置为“1”。

50.综上所述,本发明的一种逐次逼近型模数转换器,通过在常规三段式结构中增设一并列低权重位段,使得低权重位段和并列低权重位段的转换结果可以互相校验,从而提高低权重位转换结果的可靠性,降低了对比较器高精度的要求,使得高速高精度sar adc的设计变得更容易。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

51.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1