时间数字转换器及电子设备的制作方法

1.本技术涉及时间测量技术领域,尤其涉及一种时间数字转换器及电子设备。

背景技术:

2.时间数字转换器(time to digital converter,tdc)是一种将时间间隔转换为数字信号的器件,可以用来测量两个脉冲信号之间的时间间隔,广泛应用于统计激光器后脉冲分布、粒子碰撞时间、量子光学、量子密钥分配、光检测和激光雷达测距等科研领域。

3.目前,相关技术中的时间数字转换器通过计数两个脉冲信号之间参考时钟信号的周期数,以使时间数字转换器具有长动态范围;并通过多相时钟信号将一个参考时钟周期细分为更小的时间单元,以提高时间数字转换器的时间分辨率。

4.但是,上述相关技术中的时间数字转换器的时间分辨率受限于多相时钟信号的时间分辨率,存在时间分辨率低的问题,如何进一步提高时间数字转换器的时间分辨率成为本领域技术人员需要解决的技术问题。

技术实现要素:

5.本技术实施例提供了一种时间数字转换器及电子设备,能够提高时间数字转换器的时间分辨率。

6.第一方面,本技术实施例提供了一种时间数字转换器,包括:第一余量时间指示模块,包括第一时间提取单元、第一时间量化单元和第一指示信号输出单元;第一时间提取单元用于接收第一脉冲信号和多相时钟信号,根据所述第一脉冲信号和所述多相时钟信号生成第一同步信号和第一异步信号,所述第一同步信号和所述第一异步信号之间的时间间隔等于第一余量时间;所述第一时间量化单元用于接收所述第一异步信号,根据所述第一异步信号生成第一多相脉冲信号,所述第一多相脉冲信号中相邻两相脉冲信号的时间间隔小于所述多相时钟信号中相邻两相时钟信号的时间间隔;所述第一指示信号输出单元用于接收所述第一同步信号和所述第一多相脉冲信号,生成第一余量时间指示信号;所述第一余量时间指示信号用于指示所述第一余量时间;和/或,第二余量时间指示模块,包括第二时间提取单元、第二时间量化单元和第二指示信号输出单元;第二时间提取单元用于接收第二脉冲信号和多相时钟信号,根据所述第二脉冲信号和所述多相时钟信号生成第二同步信号和第二异步信号,所述第二同步信号和所述第二异步信号之间的时间间隔等于第二余量时间;所述第二时间量化单元用于接收所述第二异步信号,根据所述第二异步信号生成第二多相脉冲信号,所述第二多相脉冲信号中相邻两相脉冲信号的时间间隔小于所述多相时钟信号中相邻两相时钟信号的时间间隔;所述第二指示信号输出单元用于接收所述第二同步信号和所述第二多相脉冲信号,生成第二余量时间指示信号;所述第二余量时间指示信号用于指示所述第二余量时间。

7.作为一种具体的实施方式,所述第一时间量化单元包括:第一延时器,用于对所述第一异步信号进行延时处理,包括输入端和输出端;所述

第一延时器的输入端用于接收所述第一异步信号,输出端用于输出第一路异步信号和第二路异步信号;所述第二路异步信号和所述第一路异步信号的时间间隔等于所述多相时钟信号中相邻两相时钟信号的时间间隔;第一相位插值器,用于对所述第一路异步信号和所述第二路异步信号进行相位插值处理,包括输入端和输出端;所述第一相位插值器的输入端用于接收所述第一路异步信号和所述第二路异步信号,输出端用于输出所述第一多相脉冲信号。

8.在一种示例性的方案中,所述第一延时器包括:第一延时单元,用于对所述第一异步信号进行延时处理,包括输入端和输出端;所述第一延时单元的输入端用于接收所述第一异步信号,输出端用于输出所述第一路异步信号;第二延时单元,与所述第一延时单元并联连接,用于对所述第一异步信号进行延时处理,包括输入端和输出端;所述第二延时单元的输入端用于接收所述第一异步信号,输出端用于输出所述第二路异步信号;所述第二延时单元和所述第一延时单元的延时量差值等于所述多相时钟信号中相邻两相时钟信号的时间间隔;所述第一指示信号输出单元包括第三延时单元,用于对所述第一同步信号进行延时处理;所述第三延时单元包括输入端和输出端,输入端用于接收所述第一同步信号,输出端用于输出第一延时同步信号;所述第三延时单元的延时量等于所述第一延时单元的延时量;所述第一指示信号输出单元通过所述第一多相脉冲信号对所述第一延时同步信号进行采样,生成所述第一余量时间指示信号。

9.进一步地,所述时间数字转换器还包括延时控制模块;所述延时控制模块包括:第一环形延迟链,包括串联连接的多个第七延时单元,用于接收参考时钟信号,对所述参考时钟信号进行多次延时;所述第七延时单元、所述第一延时单元和所述第三延时单元均包括延时控制端;所述第七延时单元的延时控制端与所述第一延时单元的延时控制端以及所述第三延时单元的延时控制端相连,以使所述第一延时单元和所述第三延时单元的延时量相等,且均等于所述第一路异步信号和所述第一异步信号的时间间隔;第二环形延迟链,包括串联连接的多个第八延时单元,用于接收所述参考时钟信号,对所述参考时钟信号进行多次延时;所述第八延时单元和所述第二延时单元均包括延时控制端;所述第八延时单元的延时控制端与所述第二延时单元的延时控制端相连,用于控制所述第二延时单元的延时量,以使所述第二延时单元和所述第一延时单元的延时量差值等于所述多相时钟信号中相邻两相时钟信号的时间间隔。

10.具体地,在一种示例性的方案中,所述时间数字转换器还包括多相时钟生成模块;所述多相时钟生成模块包括:上述第一环形延迟链,包括串联连接的多个第七延时单元,用于接收参考时钟信号,生成第一初始多相时钟信号;多个第三相位插值器,与所述多个第七延时单元一一对应;每一所述第三相位插值器接收一个所述第七延时单元对应的两相时钟信号,对所述两相时钟信号进行相位插值处理,并由所述多个第三相位插值器输出所述多相时钟信号。

11.具体地,在另一种示例性的方案中,所述时间数字转换器还包括多相时钟生成模块;所述多相时钟生成模块包括:

上述第二环形延迟链,包括串联连接的多个第八延时单元,用于接收参考时钟信号,生成第二初始多相时钟信号;多个第四相位插值器,与所述多个第八延时单元一一对应;每一所述第四相位插值器接收一个所述第八延时单元对应的两相时钟信号,对所述两相时钟信号进行相位插值处理,并由所述多个第四相位插值器输出所述多相时钟信号。

12.作为一种具体的实施方式,所述第二时间量化单元包括:第二延时器,用于对所述第二异步信号进行延时处理,包括输入端和输出端;所述第二延时器的输入端用于接收所述第二异步信号,输出端用于输出第三路异步信号和第四路异步信号;所述第四路异步信号和所述第三路异步信号的时间间隔等于所述多相时钟信号中相邻两相时钟信号的时间间隔;第二相位插值器,用于对所述第三路异步信号和所述第四路异步信号进行相位插值处理,包括输入端和输出端;所述第二相位插值器的输入端用于接收所述第三路异步信号和所述第四路异步信号,输出端用于输出所述第二多相脉冲信号。

13.在一种示例性的实施方式中,所述第二延时器包括:第四延时单元,用于对所述第二异步信号进行延时处理,包括输入端和输出端;所述第四延时单元的输入端用于接收所述第二异步信号,输出端用于输出所述第三路异步信号;第五延时单元,与所述第四延时单元并联连接,用于对所述第二异步信号进行延时处理,包括输入端和输出端;所述第五延时单元的输入端用于接收所述第二异步信号,输出端用于输出所述第四路异步信号;所述第五延时单元和所述第四延时单元的延时量差值等于所述多相时钟信号中相邻两相时钟信号的时间间隔;所述第二指示信号输出单元包括第六延时单元,用于对所述第二同步信号进行延时处理;所述第六延时单元包括输入端和输出端,输入端用于接收所述第二同步信号,输出端用于输出第二延时同步信号;所述第六延时单元的延时量等于所述第四延时单元的延时量;所述第二指示信号输出单元通过所述第二多相脉冲信号对所述第二延时同步信号进行采样,生成所述第二余量时间指示信号。

14.进一步地,所述的时间数字转换器还包括延时控制模块;所述延时控制模块包括:第一环形延迟链,包括串联连接的多个第七延时单元,用于接收参考时钟信号,对所述参考时钟信号进行多次延时;所述第七延时单元、所述第四延时单元和所述第六延时单元均包括延时控制端;所述第七延时单元的延时控制端与所述第四延时单元的延时控制端以及所述第六延时单元的延时控制端相连,以使所述第四延时单元和所述第六延时单元的延时量相等,且均等于所述第三路异步信号和所述第二异步信号的时间间隔;第二环形延迟链,包括串联连接的多个第八延时单元,用于接收所述参考时钟信号,对所述参考时钟信号进行多次延时;所述第八延时单元和所述第五延时单元均包括延时控制端;所述第八延时单元的延时控制端与所述第五延时单元的延时控制端相连,用于控制所述第五延时单元的延时量,以使所述第五延时单元和所述第四延时单元的延时量差值等于所述多相时钟信号中相邻两相时钟信号的时间间隔。

15.在一种示例性的方案中,所述时间数字转换器还包括多相时钟生成模块;所述多相时钟生成模块包括:

第一环形延迟链,包括串联连接的多个第七延时单元,用于接收参考时钟信号,生成第一初始多相时钟信号;多个第三相位插值器,与所述多个第七延时单元一一对应;每一所述第三相位插值器接收一个所述第七延时单元对应的两相时钟信号,对所述两相时钟信号进行相位插值处理,并由所述多个第三相位插值器输出所述多相时钟信号;在另一种示例性的方案中,所述时间数字转换器还包括多相时钟生成模块;所述多相时钟生成模块包括:第二环形延迟链,包括串联连接的多个第八延时单元,用于接收参考时钟信号,生成第二初始多相时钟信号;多个第四相位插值器,与所述多个第八延时单元一一对应;每一所述第四相位插值器接收一个所述第八延时单元对应的两相时钟信号,对所述两相时钟信号进行相位插值处理,并由所述多个第四相位插值器输出所述多相时钟信号。

16.进一步地,所述的时间数字转换器,还包括:整量时间指示模块,用于接收参考时钟信号、所述多相时钟信号、所述第一脉冲信号和所述第二脉冲信号,根据所述参考时钟信号、所述多相时钟信号、所述第一脉冲信号和所述第二脉冲信号生成整量时间指示信号;所述整量时间指示信号用于指示整量时间;数字信号处理模块,用于接收所述整量时间指示信号、第一余量时间指示信号和/或第二余量时间指示信号,获取所述第一脉冲信号和所述第二脉冲信号之间的时间间隔。

17.第二方面,本技术实施例提供了一种电子设备,包括上述时间数字转换器,用于提高时间分辨率。

18.本技术的有益效果:本技术提供的时间数字转换器通过余量时间指示模块将多相时钟信号中相邻两相时钟信号的时间间隔划分为更小的时间单元,利用更小的时间单元对余量时间进行测量,提高时间数字转换器的时间分辨率。进一步,本技术提供的时间数字转换器通过两路异步脉冲信号,其中,两路异步脉冲信号的时间间隔等于多相时钟信号中相邻两相时钟信号的时间间隔,对两路异步脉冲信号进行相位内插实现将多相时钟信号中相邻两相时钟信号的时间间隔划分为更小的时间单元,提高了时间数字转换器的时间分辨率。进一步地,本技术提供的时间数字转换器通过两条环形延迟链控制脉冲信号进行双路延迟,通过相位插值器对双路延迟后的脉冲信号进行相位内插,实现将多相时钟信号中相邻两相时钟信号的时间间隔划分为更小的时间单元,利用更小的时间单元对余量时间进行量化,提高了时间数字转换器的时间分辨率。进一步地,本技术提供的延时控制模块和多相时钟生成模块复用环形延迟链,简化了电路结构。

附图说明

19.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

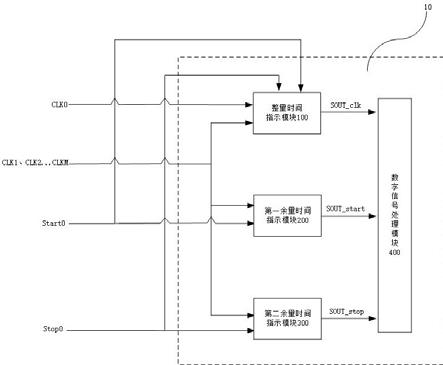

20.图1为本技术提供的一种实施例中,时间数字转换器的一种框架示意图;

图2为本技术提供的一种实施例中,时间数字转换器中多种信号的一组时序状态图,其中,第一多相脉冲信号和第二多相脉冲信号的时间间隔进行了放大处理;图3为本技术提供的一种实施例中,第一余量时间指示模块的一种框架结构示意图;图4为本技术提供的一种实施例中,第一时间提取单元的一种电路结构示意图;图5为本技术提供的一种实施例中,第一时间量化单元的一种电路结构示意图;图6为本技术提供的一种实施例中,第一相位插值器的一种电路结构示意图;图7为本技术提供的一种实施例中,第一指示信号输出单元的一种电路结构示意图;图8为本技术提供的一种实施例中,第二余量时间指示模块的一种框架结构示意图;图9为本技术提供的一种实施例中,第二时间提取单元的一种电路结构示意图;图10为本技术提供的一种实施例中,第二时间量化单元的一种电路结构示意图;图11为本技术提供的一种实施例中,第二相位插值器的一种电路结构示意图;图12为本技术提供的一种实施例中,第二指示信号输出单元的一种电路结构示意图;图13为本技术提供的一种实施例中,整量时间指示单元的一种框架结构示意图;图14为本技术提供的一种实施例中,时间数字转换器的另一种框架结构示意图;图15为图14中,多相时钟生成模块和延时控制模块的电路结构示意图;图16为本技术提供的一种实施例中,时间数字转换器的另一种框架结构示意图。

具体实施方式

21.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

22.如图1所示,一种时间数字转换器10,包括整量时间指示模块100、第一余量时间指示模块200、第二余量时间指示模块300和数字信号处理模块400;整量时间指示模块100用于接收参考时钟信号clk0、多相时钟信号clk1、clk2

…

clkm、第一脉冲信号start0和第二脉冲信号stop0,生成整量时间指示信号sout_clk;其中,多相时钟信号clk1、clk2

…

clkm是根据参考时钟信号clk0生成的一组时钟信号,且相邻两相时钟信号的时间间隔δt_clk=t/m,其中,t为参考时钟信号clk0的周期,m为多相时钟信号clk1、clk2

…

clkm的相数,且m为大于或等于3的正整数;其中,整量时间指示信号sout_clk用于指示整量时间t_clk,整量时间t_clk为第一时钟信号clk_start和第二时钟信号clk_stop之间的时间间隔,第一时钟信号clk_start为第一脉冲信号start0到来之后的第一个时钟信号,第二时钟信号clk_stop为第二脉冲信号stop0到来之后的第一个时钟信号;第一余量时间指示模块200用于接收第一脉冲信号start0和多相时钟信号clk1、clk2

…

clkm,生成第一余量时间指示信号sout_start;其中,第一余量时间指示信号sout_start用于指示第一余量时间t_start,第一余量时间t_start为第一脉冲信号start0和第一时钟信号clk_start之间的时间间隔;第二余量时间指示模块300用于接收第二脉冲信号stop0和多相时钟信号clk1、clk2

…

clkm,生成第

二余量时间指示信号sout_stop;其中,第二余量时间指示信号sout_stop用于指示第二余量时间t_stop,第二余量时间t_stop为第二脉冲信号stop0和第二时钟信号clk_stop之间的时间间隔;数字信号处理模块400用于接收整量时间指示信号sout_clk、第一余量时间指示信号sout_start以及第二余量时间指示模块sout_stop,根据公式一:t=t_clk+t_start-t_stop,获取第一脉冲信号start0和第二脉冲信号stop0之间的时间间隔t。

23.如图3所示,在一种示例性的方案中,第一余量时间指示模块200包括第一时间提取单元210、第一时间量化单元220和第一指示信号输出单元230;第一时间提取单元210用于接收第一脉冲信号start0和多相时钟信号clk1、clk2

…

clkm,根据第一脉冲信号start0和多相时钟信号clk1、clk2

…

clkm生成第一同步信号start_sync和第一异步信号start_async;其中,如图3所示,第一同步信号start_sync和第一异步信号start_async的时间间隔等于第一脉冲信号start0和第一时钟信号clk_start之间的时间间隔,即第一余量时间t_start;第一时间提取单元210利用第一同步信号start_sync和第一异步信号start_async的时间间隔等于第一余量时间t_start,提取所需测量的第一余量时间t_start;第一时间量化单元220用于接收第一异步信号start_async,根据第一异步信号start_async生成第一多相脉冲信号start1、start2

…

startn1;其中, n1为第一多相脉冲信号start1、start2

…

startn1的相数,且n1为大于或等于3的正整数;第一多相脉冲信号start1、start2

…

startn1中相邻两相脉冲信号的时间间隔δt_start=δt_clk/(n

1-1)=t/(m*(n

1-1));第一时间量化单元220利用第一多相脉冲信号start1、start2

…

startn1将相邻两相时钟信号的时间间隔δt_clk进一步细化为n-1个更小的时间间隔δt_start,可用于对第一余量时间t_start进行量化;第一指示信号输出单元230用于接收第一同步信号start_sync和第一多相脉冲信号start1、start2

…

startn1,生成第一余量指示信号sout_start,利用第一余量时间指示信号sout_start指示第一同步信号start_sync和第一异步信号start_async之间的时间间隔,进而指示第一余量时间t_start。

24.如图4所示,第一时间提取单元210包括第一同步器211,第一同步器211用于接收第一脉冲信号start0和多相时钟信号clk1、clk2

…

clkm,根据第一脉冲信号start0和多相时钟信号clk1、clk2

…

clkm,获取第一同步信号start_sync和第一异步信号start_async。理论上,第一同步器211输出的第一同步信号start_sync与第一时钟信号clk_start位于第一脉冲信号start之后的第一个上升沿对齐,即第一异步信号start_async与第一脉冲信号start0对齐;可以理解,此时,第一同步信号start_sync和第一异步信号start_async之间的时间间隔即为第一时钟信号clk_start和第一脉冲信号start0的时间间隔。但是,如图2所示,实际情况中,第一同步器211进行信号处理时存在延时,具体地,第一同步信号start_sync相比第一时钟信号clk_start存在延时δ1,延时δ1与第一同步器211的结构有关,该延时δ1可以通过预先测试得到,相应地,经过测试得到第一同步器211的延时δ1后,第一同步器211接收第一脉冲信号start0,对第一脉冲信号start0进行延时δ1后,生成第一异步信号start_async;此时,第一同步信号start_sync与第一时钟信号clk_start的时间间隔为δ1,第一异步信号start_async与第一脉冲信号start0的时间间隔也为δ1,可以理解,第一同步信号start_sync和第一异步信号start_async之间的时间时间间隔等于第一时钟信号clk_start和第一脉冲信号start0之间的时间间隔,即第一余量时间t_start;第一同步器211利用第一同步信号start_sync和第一异步信号start_async,提取第一余量时

间t_start。

25.在一种具体的实施方式中,第一同步器211包括第一同步信号获取电路2111和第一内部延时电路2112;第一同步信号获取电路2111用于接收第一脉冲信号start0和多相时钟信号clk1、clk2

…

clkm,获取第一同步信号start_sync;第一内部延时电路2112用于接收第一脉冲信号start0,对第一脉冲信号start0进行延时处理,输出第一异步信号start_async;其中,第一内部延时电路2112的延时量可通过预先测试进行调节,比如通过给第一同步器211输入已知相位关系的脉冲信号和多相时钟信号,得到第一同步器211获取同步信号产生的延时δ1,根据测试所得结果,调节第一内部延时电路2112的延时量。

26.如图5所示,第一时间量化单元220包括第一延时器221以及第一相位插值器222,第一延时器221用于接收第一异步信号start_async,对第一异步信号start_async进行延时处理,生成第一路异步信号start_async1和第二路异步信号start_async2;第二路异步信号start_async2和第一路异步信号start_async1的时间间隔等于多相时钟信号clk1、clk2

…

clkm中相邻两相时钟信号的时间间隔δt_clk;第一相位插值器222接收第一路异步信号start_async1和第二路异步信号start_async2,对第一路异步信号start_async1和第二路异步信号start_async2进行相位内插处理,在第一路异步信号start_async1和第二路异步信号start_async2至少内插一相信号,生成第一多相脉冲信号start1、start2

…

startn1,其中,第一多相脉冲信号start1、start2

…

startn1中相邻两相脉冲信号的时间间隔δt_start=t/(m*(n

1-1))。

27.如图5所示,在一种示例性的方案中,第一延时器221包括第一延时单元2211和第二延时单元2212;第一延时单元2211包括输入端和输出端;第一延时单元2211的输入端用于接收第一异步信号start_async,对第一异步信号start_async进行延时处理,生成第一路异步信号start_async1;第一延时单元2211的输出端与第一相位插值器222的第一输入端相连,用于输出第一路异步信号start_async1给第一相位插值器222;第二延时单元2212包括输入端和输出端;第二延时单元2212的输入端用于接收第一异步信号start_async,对第一异步信号start_async进行延时处理,生成第二路异步信号start_async2;第二延时单元2212的输出端与第一相位插值器222的第二输入端相连,用于输出第二路异步信号start_async2给第一相位插值器222;第二延时单元2212的延时量δt_d2大于第一延时单元2211的延时量δt_d1,且δt_d2-δt_d1=δt_clk。

28.在其他示例性的方案中,第二延时单元2212的延时量δt_d2和第一延时单元2211的延时量的延时量δt_d1还可以为其他数值,只需满足δt_d2-δt_d1=δt_clk即可,以通过第一时间量化单元220将多相时钟信号clk1、clk2

…

clkm中相邻两相时钟信号的时间间隔δt_clk划分为更小的第一时间单元δt_start,利用第一时间单元δt_start对第一余量时间t_start进行测量,进一步提高时间数字转换器10的时间分辨率。

29.如图6所示,在一种示例性的方案中,第一相位插值器222为三相插值器,包括三个相位内插器pi(phase interpolator),用于在第一路异步信号start_async1和第二路异步信号start_async2之间内插三相信号,将时间分辨率提高4倍;举例来说,当多相时钟信号clk1、clk2

…

clkm中相邻两相时钟信号的时间间隔δt_clk=t/20时,即第一路异步信号start_async1和第二路异步信号start_async2的时间间隔为t/20时,经过三相内插得到的第一多相脉冲信号start1、start2、start3、start4、start5中相邻两相脉冲信号的时间间

隔等于δt_start=(t/20)/4=t/80。

30.在其他示例性的方案中,第一相位插值器222可为内插更多相数的相位插值器,比如16相内插器,以通过第一相位插值器222将时间间隔δt_clk划分为更小的第一时间单元δt_start,利用更小的第一时间单元δt_start对第一余量时间t_start进行测量,进一步提高时间数字转换器10的时间分辨率。

31.如图7所示,在一种示例性的方案中,第一指示信号输出单元230包括第三延时单元231和第一相位状态统计单元232;第三延时单元231包括输入端和输出端,输入端用于接收第一同步信号start_sync,对第一同步信号start_sync进行延时处理后,生成第一延时同步信号start_sync1,其中,第三延时单元231的延时量δt_d3等于第一延时单元2211的延时量δt_d1,以使第一延时同步信号start_sync1和第一同步信号start_sync的时间间隔等于第一路异步信号start_async1和第一异步信号start_async的时间间隔,进而使得第一多相脉冲信号start1、start2

…

startn1中的第一延时同步信号start_sync1与第一相脉冲信号start1(即第一路异步信号start_async1)的时间间隔等于第一同步信号start_sync和第一异步信号start_async的时间间隔,即余量时间δt_start;第一相位状态统计单元232根据第一多相脉冲信号start1、start2

…

startn1和第一延时同步信号start_sync1,生成第一余量时间指示信号sout_start;具体地,第一相位状态统计单元232通过第一多相脉冲信号start1、start2

…

startn1对第一延时同步信号start_sync1进行采样,并将第一相脉冲信号start1和采样到第一延时同步信号start_sync1的一相脉冲信号之间的相位编码值差值δstart_num作为第一余量时间指示信号sout_start输出。

32.在一种示例性的方案中,第一多相脉冲信号start1、start2

…

startn1采样到第一延时同步信号start_sync1由低电平翻转到高电平时的一相脉冲信号为采样到第一延时同步信号start_sync1的一相脉冲信号。

33.具体地,第一多相脉冲信号start1、start2

…

startn1中的每一相脉冲信号具有一一对应的相位状态编码值start_num1、start_num2

…

start_num n1,比如说,第一相脉冲信号start1的相位状态编码值为1、第二相脉冲信号start2的相位状态编码值为2,第n1相脉冲信号startn1的相位状态编码值为n1;第一相位状态统计单元232通过第一相脉冲信号start1和采样到第一延时同步信号start_sync1的一相脉冲信号之间的相位编码值差值δstart_num,利用公式二:第一余量时间t_start=δt_ start*δstart_num=(t*δstart_num)/(m*(n

1-1)),即可指示第一余量时间t_start。

34.如图8所示,在一种示例性的方案中,第二余量时间指示模块300包括第二时间提取单元310、第二时间量化单元320和第二指示信号输出单元330;第二时间提取单元310用于接收第二脉冲信号stop0和多相时钟信号clk1、clk2

…

clkm,根据第二脉冲信号stop0和多相时钟信号clk1、clk2

…

clkm生成第二同步信号stop_sync和第二异步信号stop_async;其中,第二同步信号stop_sync和第二异步信号stop_async的时间间隔等于第二脉冲信号stop0和第二时钟信号clk_stop之间的时间间隔,即第二余量时间t_stop;第二时间提取单元310利用第二同步信号stop_sync和第二异步信号stop_async的时间间隔等于第二余量时间t_stop,提取所需测量的第二余量时间t_stop;第二时间量化单元320用于接收第二异步信号stop_async,根据第二异步信号stop_async生成第二多相脉冲信号stop1、stop2

…

stopn2;其中, n2为第二多相脉冲信号stop1、stop2

…

stopn2的相数,且n2为为大于或等于3

1))。

38.如图10所示,在一种示例性的方案中,第二延时器321包括第四延时单元3211和第五延时单元3212;第四延时单元3211包括输入端和输出端;第四延时单元3211的输入端用于接收第二异步信号stop_async,对第二异步信号stop_async进行延时处理,生成第三路异步信号stop_async1;第四延时单元3211的输出端与第二相位插值器322的第一输入端相连,用于输出第三路异步信号stop_async1给第二相位插值器322;第五延时单元3212包括输入端和输出端;第五延时单元3212的输入端用于接收第二异步信号stop_async,对第二异步信号stop_async进行延时处理,生成第四路异步信号stop_async2;第五延时单元3212的输出端与第二相位插值器322的第二输入端相连,用于输出第四路异步信号stop_async2给第二相位插值器322;第五延时单元3212的延时量δt_d5大于第四延时单元3211的延时量δt_d4,且δt_d5-δt_d4=δt_clk进一步地,在本实施例中,第四延时单元3211的延时量δt_d4和第一延时单元2211的延时量δt_d1满足:δt_d4=δt_d1;第五延时单元3212的延时量δt_d5和第二延时单元2212的延时量δt_d2满足:δt_d5=δt_d2。

39.在其他示例性的方案中,第五延时单元3212的延时量δt_d5和第四延时单元3211的延时量的延时量δt_d4还可以为其他数值,只需满足δt_d5-δt_d4=δt_clk即可,以通过第二时间量化单元320将多相时钟信号clk1、clk2

…

clkm中相邻两相时钟信号的时间间隔δt_clk划分为更小的第二时间单元δt_stop,利用第二时间单元δt_stop对第二余量时间t_stop进行测量,进一步提高时间数字转换器10的时间分辨率。

40.如图11所示,在一种示例性的方案中,第二相位插值器322为三相内插器,包括三个相位内插器pi(phase interpolator),用于在第三路异步信号stop_async1和第四路异步信号stop_async2之间内插三相信号,将时间分辨率提高4倍;举例来说,当多相时钟信号clk1、clk2

…

clkm中相邻两相时钟信号的时间间隔δt_clk=t/20时,即第三路异步信号stop_async1和第四路异步信号stop_async2的时间间隔为t/20时,经过三相内插得到的第二多相脉冲信号stop1、stop2、stop3、stop4、stop5中相邻两相脉冲信号的时间间隔等于δt_stop=(t/20)/4=t/80。

41.在其他示例性的方案中,第二相位插值器322可为内插更多相数的相位插值器,比如16相内插器,以通过第二相位插值器322将时间间隔δt_clk划分为更小的第二时间单元δt_stop,利用更小的第二时间单元δt_stop对第二余量时间t_stop进行测量,提高时间数字转换器10的时间分辨率。

42.如图12所示,在一种示例性的方案中,第二指示信号输出单元330包括第六延时单元331和第二相位状态统计单元332;第六延时单元331包括输入端和输出端,输入端用于接收第二同步信号stop_sync,对第二同步信号stop_sync进行延时处理后,生成第二延时同步信号stop_sync1,其中,第六延时单元331的延时量δt_d6等于第四延时单元3211的延时量δt_d4,以使第二延时同步信号stop_sync1和第二同步信号stop_sync的时间间隔等于第三路异步信号stop_async1和第二异步信号stop_async的时间间隔,进而使得第二延时同步信号stop_sync1与第二多相脉冲信号stop1、stop2

…

stopn2中的第一相脉冲信号stop1(即第三路异步信号stop_async1)的时间间隔等于第二同步信号stop_sync和第二异步信号stop_async的时间间隔,即第二余量时间δt_stop;第二相位状态统计单元332根据

第二多相脉冲信号stop1、stop2

…

stopn2和第二延时同步信号stop_sync1,生成第二余量时间指示信号sout_stop;具体地,第二相位状态统计单元332通过第二多相脉冲信号stop1、stop2

…

stopn2对第二延时同步信号stop_sync1进行采样,并将第一相脉冲信号stop1和采样到第二延时同步信号stop_sync1的一相脉冲信号之间的相位编码值差值δstop_num作为第二余量时间指示信号sout_stop输出。

43.在一种示例性的方案中,第二多相脉冲信号stop1、stop2

…

stopn2采样到第二延时同步信号stop_sync1由低电平翻转到高电平时的一相脉冲信号为采样到第二延时同步信号stop_sync1的一相脉冲信号。

44.具体地,第二多相脉冲信号stop1、stop2

…

stopn2中的每一相脉冲信号具有一一对应的相位状态编码值stop_num1、stop_num2

…

stop_numn2,比如说,第一相脉冲信号stop1的相位状态编码值为1、第二相脉冲信号stop2的相位状态编码值为2,第n2相脉冲信号stopn2的相位状态编码值为n2;第二相位状态统计单元332通过第一相脉冲信号stop1和采样到第二延时同步信号stop_sync1的一相脉冲信号之间的相位编码值差值δstop_num,利用公式二:第二余量时间t_stop=δt_ stop*δstop_num=(t*δstop_num)/(m*(n

2-1)),即可指示第一余量时间t_stop。

45.在一种示例性的方案中,第二多相脉冲信号stop1、stop2

…

stopn2的相数n2与第一多相脉冲信号start1、start2

…

startn2的相数n2相等;即第一相位插值器222和第二相位插值器322的内插相数一致,优选地,第一相位插值器222和第二相位插值器322采用结构相同的内插器,便于装配和维护,而且简化了设计。

46.如图13所示,在一种示例性的方案中,整量时间指示模块100包括计数器110和相位状态统计单元120;计数器110用于接收第一脉冲信号start0、第二脉冲信号stop0和参考时钟信号clk0,根据第一脉冲信号start0、第二脉冲信号stop0和参考时钟信号clk0,生成计数值count;其中,计数值count用于计数第一脉冲信号start0和第二脉冲信号stop0之间的时间间隔内参考时钟信号clk0的周期数;相位状态统计单元120用于接收第一脉冲信号start0、第二脉冲信号stop0和多相时钟信号clk1、clk2

…

clkm,根据第一脉冲信号start0、第二脉冲信号stop0和多相时钟信号clk1、clk2

…

clkm,生成第一相位状态编码值start_num和第二相位状态编码值stop_num;其中,多相时钟信号clk1、clk2

…

clkm在一个时钟周期t内的m个时间单元δt_clk分别对应m种相位状态,每一种相位状态均具有一一对应的相位状态编码值,其中,每一种相位状态的持续时间等于时间单元δt_clk =t/m;第一相位状态编码值start_num为第一脉冲信号start0在m种相位状态中对应的相位状态编码值,可用于指示第一脉冲信号start0在一个周期t内所处的时间段;第二相位状态编码值stop_num作为第二脉冲信号stop0在m种相位状态中对应的相位状态编码值,可用于指示第二脉冲信号stop0在一个周期t内所处的时间段;整量时间指示模块100根据计数器110获取的计数值count,以及相位状态统计单元120获取的第一相位状态编码值start_num和第二相位状态编码值stop_num,利用公式四:整量时间t_clk=t*count+δt_clk*(stop_num-start_num),或,公式五:整量时间t_clk=t*count+δt_clk*[(stop_num-start_num)+m],可用于指示整量时间t_clk。

[0047]

具体地,当第二脉冲信号stop0对应的第二相位状态编码值stop_num大于或等于第一脉冲信号start0对应的第一相位状态编码值start_num时,整量时间t_clk=t*count+

δt_clk*(stop_num-start_num);当第一脉冲信号start0和第二脉冲信号stop0位于不同周期t内,且第二脉冲信号stop0对应的第二相位状态编码值stop_num小于第一脉冲信号start0对应的第一相位状态编码值start_num时,整量时间t_clk=t*count+δt_clk*[(stop_num-start_num)+m]在本实施例中,第二相位状态编码值stop_num和第一相位状态编码值start_num的差值可用于指示第一脉冲信号start0和第二脉冲信号stop0在不满足周期t的整数倍的时间段内,时间单元δt_clk的数量,即可对第一脉冲信号start0和第二脉冲信号stop0除去周期t的整数倍时间段后剩下的时间进行粗测量。

[0048]

在本实施例中,数字信号处理模块400用于接收计数值count、第一相位状态编码值start_num和第二相位状态编码值stop_num,根据计数值count、第一相位状态编码值start_num和第二相位状态编码值stop_num,利用公式四:t_clk=t*count+δt_clk*(stop_num-start_num),或,公式五:t_clk =t*count+δt_clk*[(stop_num-start_num)+m],获取整量时间t_clk,具体采用公式四还是公式五,根据上述内容可知,取决于第二脉冲信号stop0对应的第二相位状态编码值stop_num与第一脉冲信号start0对应的第一相位状态编码值start_num之间的数值关系;具体地,当第二脉冲信号stop0对应的第二相位状态编码值stop_num大于或等于第一脉冲信号start0对应的第一相位状态编码值start_num时,数字信号处理模块400通过公式四:整量时间t_clk=t*count+δt_clk*(stop_num-start_num),获取整量时间t_clk;当第一脉冲信号start0和第二脉冲信号stop0位于不同周期t内,且第二脉冲信号stop0对应的第二相位状态编码值stop_num小于第一脉冲信号start0对应的第一相位状态编码值start_num时,数字信号处理模块400通过公式五:整量时间t_clk=t*count+δt_clk*[(stop_num-start_num)+m],获取整量时间t_clk;此时,整量时间指示信号sout_start包括计数值count、第一相位状态编码值start_num和第二相位状态编码值stop_num。

[0049]

数字信号处理模块400用于接收第一相位状态编码值差值δstart_num,根据第一相位状态编码值差值δstart_num,结合公式二:第一余量时间t_start=(t*δstart_num)/(m*(n

1-1)),获取第一余量时间t_start;此时,第一余量时间指示信号sout_start为第一相位状态编码值差值δstart_num;数字信号处理模块400用于接收第二相位状态编码值差值δstop_num,根据第二相位状态编码值差值δstop_num,结合公式三:第二余量时间t_stop=(t*δstop_num)/(m*(n

2-1)),获取第二余量时间t_stop=(t*δstop_num)/(m*(n

2-1));此时,第二余量时间指示信号sout_stop为第二相位状态编码值差值δstop_num。

[0050]

数字信号处理模块400还用于根据上述整量时间t_clk、第一余量时间t_start和第二余量时间t_stop,结合公式一:t=t_clk+t_start-t_stop,获取第一脉冲信号start0和第二脉冲信号stop0之间的时间间隔t=t_clk+t_start-t_stop。

[0051]

举例来说,参考时钟信号clk的一个时钟周期t被多相时钟信号clk1、clk2

…

clkm划分为20个时间单元δt_clk,且第一多相脉冲信号start1、start2

…

startn1将时间单元t_clk划分为四个第一时间单元δt_start,第二多相脉冲信号stop1、stop2

…

stopn2将时间单元t_clk划分为四个第二时间单元δt_stop时;当第一脉冲信号start0和第二脉冲信号stop0之间间隔一个时钟周期t,即计数值count为1,且第一脉冲信号start0对应的第一相位状态编码值start_num是3,第二脉冲信号stop0对应的第二相位状态编码值stop_num

是13;第一多相脉冲信号start1、start2

…

startn1中第4相脉冲信号start4检测到第一延时同步信号start_sync1发生电平翻转,即第一相位状态编码差值δstart_num=3;第二多相脉冲信号stop1、stop2

…

stopn2中第二相脉冲信号stop2检测到第二延时同步信号stop_sync1发生电平翻转,即第二相位状态编码差值δstop_num=1;数字信号处理模块400根据计数值count、第一相位状态编码值start_num和第二相位状态编码值stop_num获取的整量时间t_clk=1*t+(13-3)*t/20=1.5t;数字信号处理模块400根据第一相位状态编码差值δstart_num获取的第一余量时间t_start =3*((t/20)/4)=(3/80)t;数字信号处理模块400根据第二相位状态编码差值δstop_num获取的第二余量时间t_stop =1*((t/20)/4)=(1/80)t;数字信号处理模块400根据整量时间t_clk、第一余量时间t_start和第二余量时间t_stop,获取的第一脉冲信号start0和第二脉冲信号stop0之间的时间间隔t=t_clk+t_start-t_stop=1.5t+(3/80)t-(1/80)t=1.525t。

[0052]

如图14所示,在一种示例性的方案中,时间数字转换器10还包括多相时钟信号生成模块500和延时控制模块600;多相时钟信号生成模块500用于接收参考时钟信号clk0,根据参考时钟信号clk0,生成多相时钟信号clk1、clk2

…

clkm;延时控制模块600用于控制第一延时单元2211对第一异步信号start_async进行延时处理的延时量,控制第二延时单元2212对第一异步信号start_async进行延时处理的延时量,控制第三延时单元231对第一同步信号start_sync进行延时处理的延时量;延时控制模块600还用于控制第四延时单元3211对第二异步信号stop_async进行延时处理的延时量,控制第五延时单元3212对第二异步信号stop_async进行延时处理的延时量,控制第六延时单元331对第二同步信号stop_sync进行延时处理的延时量。

[0053]

如图14,15所示,在一种示例性的方案中,延时控制模块600包括第一环形延迟模块610和第二环形延迟模块620;第一环形延迟模块610包括第一环形延迟链611和第一延时自适应调节单元612,第一环形延迟链611包括串联连接的m个第七延时单元6111;第一环形延迟链611的输入端用于接收参考时钟信号clk0,输出端与第一延时自适应调节单元612的输入端相连,用于对参考时钟信号clk0进行多次延时,每一个第七延时单元的延时量均等于t/m,m为第一环形延迟链611中第七延时单元6111的数量,m为大于等于3的正整数;第一延时自适应调节单元612包括第一鉴相器pd1和第一电荷泵cp1,第一鉴相器pd1包括两个输入端和两个输出端,第一电荷泵cp1包括两个输入端和输出端;第一鉴相器pd1的两个输入端分别与第一环形延迟链611的输入端和输出端相连,接收参考时钟信号clk0以及参考时钟信号clk0经过m次延时后的时钟信号;第一鉴相器pd1的两个输出端分别与第一电荷泵cp1的两个输入端一一对应相连;第一电荷泵cp1的输出端分别与多个第七延时单元6111的延时控制端相连,用于控制每一个第七延时单元6111的延时量均等于t/m;第一电荷泵cp1的输出端还与第一延时单元2211和第三延时单元231的延时控制端相连,用于控制第一延时单元2211和第三延时单元231的延时量均为t/m;第一电荷泵cp1的输出端还与第四延时单元3211和第六延时单元331的延时控制端相连,用于控制第四延时单元3211和第六延时单元331的延时量均为t/m。

[0054]

具体地,第一电荷泵cp1的输出端输出第一延时控制电压vtr11给第七延时单元6111、第一延时单元2211、第三延时单元231、第四延时单元3211和第六延时单元331,控制第七延时单元6111、第一延时单元2211、第三延时单元231、第四延时单元3211和第六延时

单元331的延时量。

[0055]

如图15所示,第二环形延迟模块620包括第二环形延迟链621和第二延时自适应调节单元622,第二环形延迟链621包括串联连接的n个第八延时单元6211;第二环形延迟链621的输入端用于接收参考时钟信号clk0,输出端与第二延时自适应调节单元622的输入端相连,用于对参考时钟信号clk0进行多次延时,每一个第八延时单元6211的延时量均等于t/n,n为第二环形延迟链621中第八延时单元6211的数量,n为大于等于2的正整数,且n《m;第二延时自适应调节单元622包括第二鉴相器pd2和第二电荷泵cp2,第二鉴相器pd2包括两个输入端和两个输出端,第二电荷泵cp2包括两个输入端和输出端;第二鉴相器pd2的两个输入端分别与第二环形延迟链621的输入端和输出端相连,两个输出端分别与第二电荷泵cp2的两个输入端一一对应相连;第二电荷泵cp2的输出端分别与多个第八延时单元6211的延时控制端相连,用于控制每一个第八延时单元6211的延时量均等于t/n;第二电荷泵cp2的输出端还用于与第二延时单元2212的延时控制端相连,用于控制第二延时单元2212的延时量均为t/n;第二电荷泵cp2的输出端还用于与第五延时单元3212的延时控制端相连,用于控制第五延时单元3212的延时量均为t/n。

[0056]

具体地,第二电荷泵cp2的输出端输出第二延时控制电压vtr12给第八延时单元6211、第二延时单元2212以及第五延时单元3212,控制第八延时单元6211、第二延时单元2212以及第五延时单元3212的延时量。

[0057]

在本实施例中,第一环形延迟链611控制的第一延时单元2211和第三延时单元231的延时量t/m与第二环形延迟链621控制的第二延时单元2212的延时量t/n满足:(t/n)-(t/m)=δt_clk,以使第一路异步信号start_async1和第二路异步信号start_async2的时间间隔等于多相时钟信号clk1、clk2

…

clkm中相邻两相脉冲信号的时间间隔δt_clk,由第一路异步信号start_async1和第二路异步信号start_async2经过相位内插处理,得到的第一多相脉冲信号第一多相脉冲信号start1、start2

…

startn1用于将时间间隔δt_clk划分为更小的第一时间单元δt_start,提高了时间数字转换器10的时间分辨率;同理可得,第一环形延迟链611控制的第四延时单元3211和第六延时单元331的延时量t/m与第二环形延迟链621控制的第五延时单元3212的延时量 t/n满足:(t/n)-(t/m)=δt_clk,以使第三路异步信号stop_async1和第四路异步信号stop_async2的时间间隔等于多相时钟信号clk1、clk2

…

clkm中相邻两相脉冲信号的时间间隔δt_clk,由第三路异步信号stop_async1和第四路异步信号stop_async2经过相位内插处理,得到的第二多相脉冲信号stop1、stop2

…

stopn2用于将时间间隔δt_clk划分为更小的第二时间单元δt_stop,提高了时间数字转换器10的时间分辨率。

[0058]

在本实施例中,第一环形延迟链611控制第一延时单元2211和第三延时单元231的延时量相等,以使第一延时同步信号start_sync1和第一路异步信号start_async1之间的时间间隔等于第一同步信号start_sync和第一异步信号start_async的时间间隔,即第一余量时间t_start;第一相位状态统计单元232通过获取第一延时同步信号start_sync1和第一路异步信号start_async1(即第一多相脉冲信号start1、start2

…

startn1中的第一相脉冲信号start1)之间的相位状态,即可生成第一相位状态编码值差值δstart_num;第一环形延迟链611控制第四延时单元3211和第六延时单元331的延时量相等,以使第二延时同步信号stop_sync1和第三路异步信号stop_async1之间的时间间隔等于第二同步信号

stop_sync和第二异步信号stop_async的时间间隔,即第二余量时间t_stop;第二相位状态统计单元332通过获取第二延时同步信号stop_sync1和第三路异步信号stop_async1(即第二多相脉冲信号stop1、stop2

…

stopn2中的第一相脉冲信号stop1)之间的相位状态,即可生成第二相位状态编码值差值δstop_num。

[0059]

如图15所示,在一种示例性的方案中,多相时钟生成模块500包括第一环形延迟链611和m个第三相位插值器510,m个第三相位插值器510与第一环形延迟链611中的m个第七延时单元6111一一对应;第一环形延迟链611中的m个第七延时单元6111分别对接收的参考时钟信号clk0进行一次延时、两次延时

…

m次延时后,生成第一初始多相时钟信号clk01、clk02

…

clk0m,其中,相邻两相时钟信号之间的时间间隔等于t/m;每一个第三相位插值器510接收一一对应的第七延时单元6111两端的两相时钟信号,对接收的两相时钟信号进行相位插值处理,并由m个第三相位插值器510输出的多组时钟信号组成多相时钟信号clk1、clk2

…

clkm;其中,第三相位插值器510的内插相数p满足:δt_clk =(t/m)/(p+1)=(t/n)-(t/m),可得p =(2n-m)/(m-n)。

[0060]

作为一种具体的实施方式,m=n+1;此时,δt_clk=t/(n*(n+1));p=n-1。

[0061]

在一种示例性的方案中,第一环形延迟链611包括串联连接的五个第七延时单元6111,即m=5,每一个第七延时单元6111的延时量均等于t/5,第一延时单元2211、第三延时单元2321和第四延时单元3211、第六延时单元331的延时量均等于t/5;第二环形延迟链621包括串联连接的四个第七延时单元6111,即n=4,每一个第八延时单元6211的延时量均等于t/4,第二延时单元2212和第五延时单元3212的延时量也为t/5;第三相位插值器510的内插相数p=3;此时,多相时钟生成模块500生成二十相时钟信号clk1、clk2、clk3、clk4、clk5、clk6、clk7、clk8、clk9、clk10、clk11、clk12、clk13、clk14、clk15、clk16、clk17、clk18、clk19、clk20,相邻两相时钟信号的时间间隔δt_clk=t/20;第一路异步信号start_async1和第二路异步信号start_async2的时间间隔=t/4-t/5=t/20=δt_clk;第三路异步信号stop_async1和第四路异步信号stop_async2的时间间隔=t/4-t/5=t/20=δt_clk。

[0062]

具体地,五个第七延时单元6111分别对参考时钟信号clk0进行一次延时、两次延时、三次延时、四次延时和五次延时,生成第一初始多相时钟信号clk01、clk02、clk03、clk04、clk05,其中,相邻两相时钟信号之间的时间间隔等于t/5;第五相初始时钟信号clk05与参考时钟信号clk0同频同相;多相时钟生成模块500包括五个第三相位内插器510;第三相位内插器510均为三相内插器,用于在接收的两相时钟信号之间内插三个相位;其中,第一个第三相位内插器510用于接收参考时钟信号clk0和第一相时钟信号clk01,在参考时钟信号clk0和第一相时钟信号clk01之间内插三个相位后,输出第一组多相时钟信号clk1(参考时钟信号clk0)、clk2、clk3、clk4、clk5(第一相时钟信号clk01);第二个第三相位内插器510用于接收第一相时钟信号clk01和第二相时钟信号clk02,在第一相时钟信号clk01和第二相时钟信号clk02之间内插三个相位后,输出第二组多相时钟信号clk5(第一相时钟信号clk01)、clk6、clk7、clk8、clk9(第二相时钟信号clk02);第三个第三相位内插器510用于接收第二相时钟信号clk02和第三相时钟信号clk03,在第二相时钟信号clk02和第三相时钟信号clk03之间内插三个相位后,输出第三组多相时钟信号clk9(第二相时钟信号clk02)、clk10、clk11、clk12、clk13(第三相时钟信号clk03);第四个第三相位内插器510用于接收第三相时钟信号clk03和第四相时钟信号clk04,在第三相时钟信号clk03和第四

相时钟信号clk04之间内插三个相位后,输出第四组多相时钟信号clk13(第三相时钟信号clk03)、clk14、clk15、clk16、clk17(第四相时钟信号clk04);第五个第三相位内插器510用于接收第四相时钟信号clk04和第五相时钟信号clk05,在第四相时钟信号clk04和第五相时钟信号clk05之间内插三个相位后,输出第五组多相时钟信号clk17(第四相时钟信号clk05)、clk18、clk19、clk20、clk05;第一组多相时钟信号clk1、clk2、clk3、clk4、clk5,第二组多相时钟信号clk5、clk6、clk7、clk8、clk9,第三组多相时钟信号clk9、clk10、clk11、clk12、clk13,第四组多相时钟信号clk13、clk14、clk15、clk16、clk17以及第五组多相时钟信号clk17、clk18、clk19、clk20、clk05组成多相时钟信号clk1、clk2、clk3、clk4、clk5、clk6、clk7、clk8、clk9、clk10、clk11、clk12、clk13、clk14、clk15、clk16、clk17、clk18、clk19、clk20;多相时钟信号clk1、clk2、clk3、clk4、clk5、clk6、clk7、clk8、clk9、clk10、clk11、clk12、clk13、clk14、clk15、clk16、clk17、clk18、clk19、clk20将参考时钟信号clk0的一个时钟周期t划分为20个时间单元δt_clk=t/20。

[0063]

如图16所示,在另一种示例性的方案中,多相时钟生成模块500包括第二环形延迟链621和n个第四相位插值器520,n个第四相位插值器520与第二环形延迟链611中的n个第八延时单元6211一一对应;第一环形延迟链611中的n个第八延时单元6211分别对接收的参考时钟信号clk0进行一次延时、两次延时

…

n次延时后,生成第二初始多相时钟信号clk01、clk02

…

clk0n,其中,相邻两相时钟信号之间的时间间隔等于t/n;每一个第四相位插值器520接收一一对应的第八延时单元6211两端的两相时钟信号,对接收的两相时钟信号进行相位插值处理,并由n个第四相位插值器520输出多组时钟信号组成多相时钟信号clk1、clk2

…

clkm;其中,第四相位插值器520的内插相数q满足:δt_clk =(t/n)/(q+1)=(t/n)-(t/m),可得q=n/(m-n)。

[0064]

作为一种具体的实施方式,m=n+1;此时,δt_clk=t/(n*(n+1));q=n。

[0065]

在一种示例性的方案中,第一环形延迟链611包括串联连接的五个第七延时单元6111,即m=5,每一个第七延时单元6111的延时量均等于t/5,第一延时单元2211、第三延时单元2321和第四延时单元3211、第六延时单元331的延时量均等于t/5;第二环形延迟链621包括串联连接的四个第七延时单元6111,即n=4,每一个第八延时单元6211的延时量均等于t/4,第二延时单元2212和第五延时单元3212的延时量也为t/5;第四相位插值器520的内插相数q=4;此时,多相时钟生成模块500生成二十相时钟信号clk1、clk2、clk3、clk4、clk5、clk6、clk7、clk8、clk9、clk10、clk11、clk12、clk13、clk14、clk15、clk16、clk17、clk18、clk19、clk20,相邻两相时钟信号的时间间隔δt_clk=t/20;第一路异步信号start_async1和第二路异步信号start_async2的时间间隔=t/4-t/5=t/20=δt_clk;第三路异步信号stop_async1和第四路异步信号stop_async2的时间间隔=t/4-t/5=t/20=δt_clk。

[0066]

具体地,四个第八延时单元6211分别对参考时钟信号clk0进行一次延时、两次延时、三次延时和四次延时,生成第二初始多相时钟信号clk001、clk002、clk003、clk004(与参考时钟信号clk0同频同相),其中,相邻两相时钟信号之间的时间间隔等于t/4;多相时钟生成模块500包括四个第四相位内插器520;第四相位内插器520均为四相内插器,用于在接收的两相时钟信号之间内插四个相位;其中,第一个第四相位内插器520用于接收参考时钟信号clk0和第一相时钟信号clk001,在参考时钟信号clk0和第一相时钟信号clk001之间内插四个相位后,输出第一组多相时钟信号clk1(参考时钟信号clk0)、clk2、clk3、clk4、

clk5、clk6(第一相时钟信号clk001);第二个第四相位内插器520用于接收第一相时钟信号clk001和第二相时钟信号clk002,在第一相时钟信号clk001和第二相时钟信号clk002之间内插四个相位后,输出第二组多相时钟信号clk6(第一相时钟信号clk001)、clk7、clk8、clk9、clk10、clk11(第二相时钟信号clk002);第三个第二相时钟信号clk12用于接收第二相时钟信号clk12和第三相时钟信号clk13,在第二相时钟信号clk12和第三相时钟信号clk13之间内插四个相位后,输出第三组多相时钟信号clk11(第二相时钟信号clk002)、clk12、clk13、clk14、clk15、clk16(第三相时钟信号clk003);第四个第四相位内插器520用于接收第三相时钟信号clk13和第四相时钟信号clk14,在第三相时钟信号clk13和第四相时钟信号clk14之间内插四个相位后,输出第四组多相时钟信号clk16(第三相时钟信号clk003)、clk17、clk18、clk19、clk004;第一组多相时钟信号clk1、clk2、clk3、clk4、clk5、clk6,第二组多相时钟信号clk6、clk7、clk8、clk9、clk10、clk11,第三组多相时钟信号clk11、clk12、clk13、clk14、clk15、clk16,第四组多相时钟信号clk16、clk17、clk18、clk19、clk20、clk004组成多相时钟信号clk1、clk2、clk3、clk4、clk5、clk6、clk7、clk8、clk9、clk10、clk11、clk12、clk13、clk14、clk15、clk16、clk17、clk18、clk19、clk20;多相时钟信号clk1、clk2、clk3、clk4、clk5、clk6、clk7、clk8、clk9、clk10、clk11、clk12、clk13、clk14、clk15、clk16、clk17、clk18、clk19、clk20将参考时钟信号clk0的一个时钟周期t划分为20个时间单元δt_clk=t/20。

[0067]

本技术实施例还提供一种电子设备,该电子设备包括上述时间数字转换器10和安装件。安装件用于将时间数字转换器10安装于电子设备上。

[0068]

在一种示例性的方案中,上述电子设备为激光雷达,其中,是以发射激光光束来探测目标物体的位置、速度等特征量的雷达系统。激光雷达还包括激光发射装置和激光接收装置;激光发射装置在发射电信号的驱动下向探测区域射出发射光信号;再由激光接收装置接收从目标物体反射的反射光信号,并将反射光信号转换为反射电信号;电子设备可通过时间数字转换器10获取发射电信号(第一脉冲信号start)和接收电信号(第二脉冲信号stop)之间的时间间隔,即可获取探测目标物体的位置。

[0069]

在另一种示例性的方案中,电子设备还可以为手机、电脑等任意的具有测距功能的设备,本技术实施例对此并不作出限定。

[0070]

以上所述仅为本技术的较佳实施例而已,并不用以限制本技术,凡在本技术的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1